Abstract

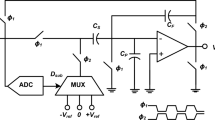

A correlation-based digital background calibration algorithm for pipelined Analog-to-Digital Converters (ADCs) is presented in this paper. The merit of the calibration algorithm is that the main errors information, which include the capacitor mismatches and residue amplifier distortion, are extracted integrally. A modified 1st pipelined stage is adopted to solve the signal overflow caused by the Pseudo-random Noise (PN) sequences. Behavioral simulation results verify the effectiveness of the algorithm. It improves the Signal-to-Noise-plus-Distortion Ratio (SNDR) and Spurious-Free-Dynamic-Range (SFDR) of the pipelined ADC from 41.8 dB to 78.3 dB and 55.6 dB to 98.6 dB, respectively, which is comparable to the prior arts.

Similar content being viewed by others

References

M. Taherzaheh-Sani and A. A. Hamoui. Digital background calibration of capacitor-mismatch errors in pipeline ADCs. IEEE Transactions on Circuits and Systems II, 53(2006)9, 966–970.

S. Y. Zhang, L. Ding, J. J. Xu, et al.. Digital background calibration of MDAC stage gain error and DAC error in pipelined ADC. IEEE International Conference on Solid-State and Integrated Circuit Technology, Shanghai, China, November 2010, 251–253.

K. Fan, X. M. Liu, and A. Lee. Digital calibration technique for a 14-bit 125-MS/s pipelined ADC using PN dithering. IEEE International Symposium on Intelligent Signal Processing and Communications Systems, Chiang Mai, Thailand, December 2010, 1–4.

A. Panigada and I. Galton. Digital background correction of harmonic distortion in pipelined ADCs. IEEE Transactions on Circuits and System I, 53(2006)9, 1885–1895.

N. Sun. Exploiting Process variation and noise in comparators to calibrate interstage gain nonlinearity in pipelined ADCs. IEEE Transactions on Circuits and System I, 59(2012)4, 685–695.

Y. S. Shu and B. S. Song. A 15-bit linear 20-MS/s pipelined ADC digitally calibrated with signal-dependent dithering. IEEE Journal of Solid-State Circuits, 43(2008)2, 342–350.

L. Cheng, L. Luo, F. Ye, et al.. A novel digital calibration with low complexity for pipelined ADC. IEEE 8th International Conference on ASICON, Changsha, China, October 2009, 222–225.

L. Luo, K. Ling, L. Cheng, et al.. A digitally calibrated 14-bit linear 100-MS/s pipelined ADC with wideband sampling front end. 35th European Solid State Circuits Conference, Athens, Greece, September 2009, 472–475.

O. Stroeble, V. Dias, and C. Schwoerer. An 80 MHz 10b pipeline ADC with dynamic range doubling and dynamic reference selection. Proceedings of IEEE International Solid-State Circuits Conference, CA, USA, February 2004, Vol. 1, 462–539.

L. X. Shi, W. Zhao, J. H. Wu, et al.. Digital background calibration techniques for pipelined ADC based on comparator dithering. IEEE Transactions on Circuits and Systems II, 59(2012)4, 239–243.

W. W. Tang, Q. Li, and G. J. Li. A digital nonlinearity correction technique for pipelined ADC’s. IEEE Asia Pacific Conference on Postgraduate Research in Microelectronics and Electronics, Shanghai, China, September 2010, 119–122.

Author information

Authors and Affiliations

Corresponding author

Additional information

Supported by the Doctoral Program Foundation of Institutions of Higher Education of China (No. 20120111120008), State Key Lab of ASIC & System (Fudan University) (No. 11KF001), and Special Fund for Doctoral Program (Hefei University of Technology) (No. 2011HGBZ0953).

Communication author: Xie Guangjun, born in 1970, male, Ph.D., Professor.

About this article

Cite this article

Wu, C., Zhang, Z., Gao, S. et al. Digital background calibration of capacitor mismatches and harmonic distortion in pipelined ADC. J. Electron.(China) 30, 299–307 (2013). https://doi.org/10.1007/s11767-013-3011-8

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11767-013-3011-8

Key words

- Analog-to-Digital Converter (ADC)

- Capacitor mismatches

- Harmonic distortion

- Pseudo-random Noise (PN) sequence

- Calibration