Abstract

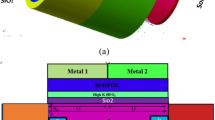

The present study simulated and investigated a 3D double-gate junctionless transistor with a gate length of 10 nm and using dual P+-wire (DPW) on the leftmost and rightmost ends of the main channel in the DC and AC modes. The DC analysis showed that more carriers are depleted from the middle of the channel in the DPW structure compared to the same structure without DPW which is the main structure of this study. Moreover, the drain leakage currents at temperatures of 233 K, 300 K, 400 K, and 500 K experienced significant reductions in the DPW structure compared to the main structure. The results are also indicative of the improved drain-induced barrier lowering (DIBL) and ION/IOFF in the DPW structure compared to the main structure. On the other hand, the AC analysis showed that the parasitic capacitances in the DPW structure are reduced at a frequency of 1 MHz compared to the main structure, in turn increasing the cut-off frequency. The analysis results also showed that maximum available power gain (GMA), maximum stable power gain (GMS), max transducer power gain, and unilateral power were improved in the DPW structure compared to the main structure.

Similar content being viewed by others

References

E. Chebaki, F. Djeffal, and T. Bentrcia, Physica Status Solidi (c) 9, 2041 (2012).

G.L. Priya and N.B. Balamurugan, AEU-Int. J. Electron. C. 99, 130 (2019).

S. Sahay and M.J. Kumar, IEEE J. Electron Dev. Soc. 4, 110 (2016).

A. Pal and A. Sarkar, Eng. Sci. Technol. Int. J. 17, 205 (2014).

M. Bavir, A. Abbasi, and A.A. Orouji, SILICON 12, 1593 (2019).

M.S. Parihar, D. Ghosh, and A. Kranti, IEEE Trans. Electron Devices 60, 1540 (2013).

H. Ferhati and F. Djeffal, J. Comput. Electron. 17, 129 (2017).

M. Gupta and V.P.-H. Hu, IEEE Electron Device Lett. 41, 473 (2020).

S.L. Tripathi, S.K. Sinha, and G.S. Patel, J. Electron. Mater. 49, 4291 (2020).

M.A. Raushan, N. Alam, and M.J. Siddiqui, J. Comput. Electron. 18, 864 (2019).

A.A. Orouji and A. Abbasi, Superlattices Microstruct. 52, 552 (2012).

M. Saremi, M. Saremi, H. Niazi, M. Saremi, and A.Y. Goharrizi, J. Electron. Mater. 46, 5570 (2017).

M. K. Anvarifard, Int. J. Numer. Model. Electron. Netw. Devices Fields 32, (2018).

J.-P. Colinge, C.-W. Lee, A. Afzalian, N.D. Akhavan, R. Yan, I. Ferain, P. Razavi, B. O’Neill, A. Blake, M. White, A.-M. Kelleher, B. McCarthy, and R. Murphy, Nat. Nanotechnol. 5, 225 (2010).

M. Fallahnejad, M. Vadizadeh, A. Salehi, A. Kashaniniya, and F. Razaghian, Physica E Low-Dimens. Syst. Nanostruct. 115, 113715 (2020).

T.A. Oproglidis, T.A. Karatsori, C.G. Theodorou, A. Tsormpatzoglou, S. Barraud, G. Ghibaudo, and C.A. Dimitriadis, IEEE Trans. Electron Devices 67, 424 (2020).

M. Kumar, K. Aditya, and A. Dixit, IEEE Trans. Electron Devices 67, 3424 (2020).

K. Kumar, A. Raman, B. Raj, S. Singh, and N. Kumar, Appl. Phys. A 126, 1 (2020).

E. Buitrago, G. Fagas, M.F.-B. Badia, Y.M. Georgiev, M. Berthomé, and A.M. Ionescu, Sens. Actuators, B Chem. 183, 1 (2013).

A. Garg, B. Singh, Y. Singh, and A.E.U. Int, J. Electron. Commun. 118, 153140 (2020).

V. Raju and K. Sivasankaran, Int. J. Numer. Model. Electron. Netw. Devices Fields 32, e2481 (2018).

B. Singh, D. Gola, K. Singh, E. Goel, S. Kumar, and S. Jit, Mater. Sci. Semicond. Process. 58, 82 (2017).

S. Gundapaneni, S. Ganguly, and A. Kottantharayil, IEEE Electron Device Lett. 32, 261 (2011).

A.K. Jain and M.J. Kumar, IEEE Access 8, 137540 (2020).

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Bavir, M., Abbasi, A. & Orouji, A.A. Dual P+-Wire Double-Gate Junctionless MOSFET with 10-nm Regime for Low Power Applications. J. Electron. Mater. 51, 2083–2094 (2022). https://doi.org/10.1007/s11664-022-09462-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11664-022-09462-5