Abstract

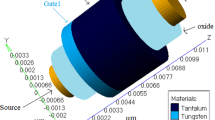

This research article presents a simulation study on a dielectric pocket engineered dual metal nanowire ferroelectric (DPE-DM-NW-Fe FET) MOSFET. The aim is to mitigate the Gate-Induced Drain Leakage (GIDL) effect in the off-state condition and improve the subthreshold swing. GIDL is a type of SCE which is detrimental for the device as continuous gate leakage current. Severely hamper the performance of the device particularly in analog applications. To prevent this a novel structure is proposed in which two dielectric pockets are introduced adjacent to the source and drain to reduce the SCEs. GIDL occurs even when the gate voltage is nearly zero, but it becomes significant when the gate region is at a lower bias and the drain region is at a higher bias. The introduced dielectric pockets act as diffusion stoppers, forming insulating barriers to prevent off-state current. Simulation studies were conducted to analyze off-state GIDL currents for different channel lengths (30 nm, 40 nm, and 50 nm). Various parameters such as electric field, electron concentration, electron velocity, and surface potential have been simulated and compared with a Single Metal Gate (SMG) cylindrical MOSFET. Critical performance parameters including drain current, transconductance (gm), output conductance (gd), input capacitance (CGG), cutoff frequency (fT), gain transconductance frequency product (GTFP), gain frequency product (GFP), maximum transfer power gain (MTPG), unilateral power gain (UPG), and early voltage (Vea) have been calculated. Additionally, the noise performances of the DPE-DM-NW-Fe FET have been examined, and its implementation as a CMOS inverter have been explored for determining noise margins. The lower noise margin makes the device suitable for high-frequency applications. The simulations have been conducted using the ATLAS-3D simulator.

Similar content being viewed by others

References

Aaesha A, Ammar N, Victor N (2013) Electric-field and temperature dependence of the activation energy associated with gate induced drain leakage. J Appl Phys 113(044513):1–5

Ana F (2012) Suppression of gate induced drain leakage current (GIDL) by gate work function engineering: analysis and model. J Electron Dev 13:984–996

Bhuyan MH (2020) A review of the fabrication process of the pocket implanted MOSFET structure. SEU J Sci Eng 14(1)

Bouhdada A, Bakkali S, Touhami A (1997) Modelling of gate-induced drain leakage in relation to technological parameters and temperature. Microelectron Reliab 37(4):649–652

Chang C, Haddad SA, Swaminathan BA, Lien J (1988) Drain-avalanche and hole-trapping induced gate leakage in thin-oxide MOS devices. IEEE Electron Dev Lett 9(11):588–590

Chen J, Chan TY, Chen IC, Ko PK, Hu C (1987) Subbreakdown drain leakage current in MOSFET. IEEE Electron Dev Lett 8(11):515–517

Chen JH, Wong SC, Wang YH (2001) An analytic three-terminal band-to-band tunneling model on GIDL in MOSFET. IEEE Trans Electron Dev 48(7):1400–1405

Chen JF, Yan CR, Lin YC, Fan JJ, Yang SF, Shih WC (2011) Analysis of GIDL-induced off-state breakdown in high-voltage depletion-mode nMOSFETs. IEEE Trans Electron Dev 58(6):1608–1613

Fan J, Li M, Xu X, Yang Y, Xuan H, Huang R (2014) Insight into gate-induced drain leakage in silicon nanowire transistors. IEEE Trans Electron Devices 62(1):213–219

Garg S, Kaur J, Goel A, Haldar S, Gupta RS (2023a) Physics based analytical modeling and simulation of Cylindrical Junctionless Nanowire Ferroelectric field effect transistor (CJNFe-FET) for enhanced analog performance. Microsyst Technol 13:1–3

Garg S, Haldar S, Kaur J, Gupta RS, Goel A (2023) Temperature sensitive analysis of junctionless nanowire ferroelectric field effect transistor (JNFe- FET) for enhanced analog performance. In: IEEE Devices for Integrated Circuit (DevIC), Kalyani, India, pp 425–429

Goel A, Rewari S, Verma S, Gupta RS (2019) Shallow extension engineered dual material surrounding gate (SEE-DM-SG-DMGFeFET). Semicond Sci Technol 34:6

Goel A, Rewari S, Verma S, Gupta RS (2021) Modeling of shallow extension engineered dual metal surrounding gate (SEE-DM-SG) MOSFET gate-induced drain leakage (GIDL). Indian J Phys 95:299–308

Jayanarayanan SK, Dey S, Donnelly JP, Banerjee SK (2006) A novel 50 nm vertical MOSFET with a dielectric pocket. Solid-State Electron 50(5):897–900

Jimenez D, Saenz JJ, Iniguez B, Sune J, Marsal LF, Pallares J (2004) Modeling of nanoscale gate-all-around MOSFETs. IEEE Electron Device Lett 25(5):314–316

Jong-Tae P, Colinge J-P (2002) Multiple gate SOI MOSFETs: device design guidelines. IEEE Tran Electron Dev 49(12):2222–2229

Jurczak M, Skotnicki T, Gwoziecki R, Paoli M, Tormen B, Ribot P, Dutartre D, Monfray S, Galvier J (2001) Dielectric pockets-a new concept of the junctions for deca-nanometric CMOS devices. IEEE Trans Electron Dev 48(8):1770–1775

Kobayashi M, Hiramoto T (2023) Device design guideline for slope ferroelectric FET using negative capacitance in sub-0.2 operation. Oper Speed Mater Requirement Energy Efficiency

Kumar MJ, Chaudhry A (2004) Two-dimensional analytical modeling of fully depleted DMG SOI MOSFET and evidence for diminished SCEs. IEEE Trans Electron Dev 51(4):569–574

Madan J, Gupta RS, Chaujar R (2017) Performance investigation of heterogeneous gate dielectric-gate metal engineered–gate all around-tunnel FET for RF applications. Microsyst Technol 23:4081–4090

Maity NP, Maity R, Baishya S (2017) Voltage and oxide thickness dependent tunneling current density and tunnel resistivity model: application to high-k material HfO2 based MOS devices. Superlattices Microstruct 111:628–641

Mehta H, Kaur H (2016) Modeling and simulation study of novel double gate ferroelectric junction-less (DGFJL) transistor. Superlattices Microstruct 97:536–547

Mehta H, Kaur H (2018) Impact of Gaussian doping profile and negative capacitance effect on double-gate junction-less transistors (DGJLTs). IEEE Trans Electron Dev 65:7

Neeraj N, Sharma S, Goel A, Rewari S, Gupta RS (2023) Improved analog and AC performance for high frequency linearity-based applications using gate-stack dual metal (DM) nanowire (NW) FET (4H-SiC). Microsyst Technol 10:1–4

Nirmal D, Kumar PV, Joy D, Jebalin BK, Kumar NM (2013) Nanoscale tri gate MOSFET for ultralow power applications using high-k dielectrics. In: 2013 IEEE 5th International Nanoelectronics Conference (INEC), pp 12–19

Nirmali, Kumar V, Samuel PC, Shrithi, Thomassmohan DMK (2024) Analysis of dual gate MOSFETS using high K dielectrics

Pahwa G, Member S, Dutta T, Agarwal A, Chauhan YS (2017) Compact model for ferroelectric negative capacitance transistor with MFIS structure. IEEE Trans Electron Dev 64:3

Panchanan S, Maity R, Baishya S, Maity N (2023a) Charge-based trans-capacitance model for SiO2/HfO2 based nano scale trigate FinFET including quantum mechanical effect. SILICON 16:1–12

Panchanan S, Maity R, Baidya A (2023b) Role of fin shape on drain current of SiO2/HfO2 based trigate FinFET including quantum mechanical effect. SILICON 15:3883–3895

Ranjan R (2019) Performance reliability of ultra-thin Si-SiO2, Si-Al2O3, Si-ZrO2 and Si-HfO2 interface in rectangular steep retrograded nano-regimes devices. Microelectron Reliab 96:21–28

Roldan JB, Gamiz F, Lopez-Villanueva JA (1998) IEEE Trans Electron Devices 45:2249

Roy S, Chakarabarty P, Pally R (2022) Assessing RF/AC performance and linearity analysis of NCFET in CMOS compatible thin body FDSOI. IEEE Trans Electron Dev 69(2)

Sakurai T, Newton AR (1990) IEEE Solid State Circ 25:584

Shih CH, Chen YM, Lien C (2004) An analytical model of short-channel effect for metal–oxide–semiconductor field-effect transistor with insulated shallow extension. Jpn J Appl Phys 43(12R):7993

Trivedi N, Kumar M, Haldar S, Deswal SS, Gupta M, Gupta RS (2019) Assessment of analog RF performance for insulated shallow extension (ISE) cylindrical surrounding gate (CSG) MOSFET incorporating gate stack. Microsyst Technol 25:1547–1554

Yu B, Wann CH, Nowak ED, Noda K, Hu C (1997) Short-channel effect improved by lateral channel-engineering in deep-submicronmeter MOSFET’s. IEEE Trans Electron Dev 44(4):627–634

Yu B, Lu H, Liu M, Taur Y (2007) Explicit continuous model for double gate and surrounding gate MOSFET. IEEE Tran Electron Dev 54(10):2715–2222

Acknowledgements

The authors are gratified to the Director, Maharaja Agrasen Institute of Technology for providing necessary facilities to carry out this research work.

Author information

Authors and Affiliations

Contributions

A. The author solely responsible for literature survey and writing the paper. B. The author ensures that questions related to the accuracy or integrity of any part of the work are appropriately addressed. C.D. performed the analysis of paper in terms of authenticity and verified the simulated results. E. to investigate and supervised the findings of this work.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Garg, S., Kaur, J., Goel, A. et al. Dielectric pocket engineered, gate induced drain leakages (GIDL) and analog performance analysis of dual metal nanowire ferroelectric MOSFET (DPE-DM-NW-Fe FET) as an inverter. Microsyst Technol (2024). https://doi.org/10.1007/s00542-024-05681-4

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00542-024-05681-4