Abstract

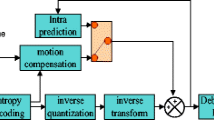

The deblocking filter (DF) is one of the most complex functional cores of the H.264/AVC and SVC codecs. Its computational cost is heavily dependent on the video profile and the selected scalability level. With the goal of providing faster and better solutions, developers are focused on designing hardware architectures. Thus, it is possible taking advantage of multitasking, reusability and parallelization techniques. In this context, this work proposes a scalable DF architecture that is able to adapt its structure and performance to different video configurations, due to its modular and regular structure. The scalability feature avoids redesigning the whole architecture in case of the environmental demands or the configuration settings change. These facts mean savings in terms of design productivity and silicon area by adapting the necessary logical resources to each condition. Furthermore, regarding the data dependences involved in the H.264/AVC DF algorithm, the proposed architecture relies on an improved version of a traditional wavefront parallelization strategy, also proposed by the authors. This solution reduces the amount of clock cycles needed to filter a video frame as compared to traditional strategies. Implementation results, in an FPGA Virtex-5, demonstrate the performance benefits of this flexible solution as compared to some rigid state-of-the-art deblocking filter approaches.

Similar content being viewed by others

References

Werda, I., Dammak, T., Grandpierre, T., Ayed, M., Masmoudi, N.: Real-time H.264/AVC baseline decoder implementation on TMS320C6416. J. Real-Time Imag. Process. pp. 1–18. Springer Berlin (2010)

Suarez, N., Callico, G.M., Lopez, S., Lopez, J., Sarmiento, R.: Performance analysis of the scalable video coding (SVC) extension of H.264/AVC for constrained scenarios; Proceedings SPIE 8067, VLSI Circuits and Systems V, pp. 1–9 (2011)

Horowitz, M., Joch, A., Kossentini, F., Hallapuro, A.: H.264/AVC baseline profile decoder complexity analysis. IEEE Transactions on Circuits and Systems for Video Technology, vol. 13, no. 7, pp. 704–716, July 2003

Schwarz, H., Marpe, D., Wiegand, T.: Overview of the scalable video coding extension of the H.264/AVC standard. IEEE Transactions on Circuits and Systems for Video Technology. vol. 17, no. 9, pp. 1103–1120, September 2007

International Telecommunication Union: H.264: advanced video coding for generic audiovisual services. In: H.264 Recommendations. Available at: http://www.itu.int/rec/T-REC-H.264. Accessed August 2012

Warsaw, T., Lukowiak, M.: Architecture design of an H.264/AVC decoder for real-time FPGA implementation. Proceedings of International Conference on Application-specific Systems, Architectures and Processors (ASAP), pp. 253–256 (2006)

Liu, T.M., Lee, W.P., Lee, C.Y.: An in/post-loop deblocking filter with hybrid filtering schedule. IEEE Transactions on Circuits System Video Technology, vol. 17, no. 7, pp. 937–943 (2007)

Lai, Y.K., Chen, L.F., Chiou, W.C.: A memory interleaving and interlacing architecture for deblocking filter in H.264/AVC. IEEE Transactions on Consumer Electronics, vol. 56, no. 4, pp. 2812–2817 (2010)

Chien, C.A., Jian, G.A., Chang, H.C., Chen, K.H., Guo, J.I.: High efficiency data access system architecture for deblocking filter supporting multiple video coding standards. IEEE Transactions on Consumer Electronics, vol. 58, no. 2, pp. 670–678 (2012)

Jia, W., Liu, L., Yin, S., Zhu, M., Wang, Z.: A fast complete deblocking filter on a coarse-grained reconfigurable processor supporting H.264 high profile decoding. Pacific Conference on Postgraduate Research on Microelectronics and Electronics (Prime Asia), pp. 1–4 (2010)

Kefalas, N., Theodoridis, G.: A high throughput pipelined architecture for H.264/AVC deblocking filter. International Conference on Electronics, Circuits, and Systems (ICECS), pp. 387–391 (2010)

Liu, T., Yang, E., Cheng, R., Fu, Y.: CUDA-based H.264/AVC deblocking filtering. International Conference on audio language and image processing (ICALIP), pp. 1547–1551 (2010)

Krutz, A., Glantz, A., Tok, M., Sikora, T.: Adaptive global motion temporal filtering. Picture Coding Symposium (PCS), pp. 289–292 (2012)

Van der Tol, E.B., Jaspers, E.G., Gelderblom, R.H.: Mapping of H.264 decoding on a multiprocessor architecture. In: Proceedings SPIE Conference on Image and Video Communications and Processing, vol. 5022, pp. 707–718 (2009)

Kim, W., Cho, K., Chung, K.: Stage-based Frame-Partitioned Parallelization of H.264/AVC Decoding. IEEE Transactions on Consumer Electronics, vol. 56, no. 2, pp. 1088–1096 (2010)

Zhang, Y., Yan, C., Dai, F., Ma, Y.: Efficient parallel framework for H.264/AVC deblocking filter on many-core platform. IEEE Transactions on Multimedia, vol. 14, no. 3, pp. 510–524 (2012)

[KKL10]Kthiri, M., Kadionik P., Levi, H., Loukil, H., Ben Atitallah, A., Masmoudi, N.: A parallel hardware architecture of deblocking filter in H264/AVC, 2010 9th International Symposium on Electronics and Telecommunications (ISETC), pp. 341–344, 11–12 November 2010

Wang, S.W., Yang, S.S., Chen, H.M., Yang, C.L., Wu, J.L.: A multi-core architecture based parallel framework for H.264/AVC deblocking filters. J. Signal Process. Syst. vol. 57, no. 2, pp. 195–211, Ed. Springer, (2009)

Pieters, B., Hollemeersch, C.F.J., De Cock, J., Lambert, P., De Neve, W., De Walle, R.V.: Parallel Deblocking Filtering in MPEG-4 AVC/H.264 on Massively Parallel Architecture. IEEE Transactions on Circuits System Video Technology, Transactions Letters, vol. 21, no. 1, pp. 96–100 (2011)

Yan, C., Dai, F., Zhang, Y.: Parallel deblocking filter for H.264/AVC on the TILERA many-core systems. Advances in Multimedia Modelling, Lecture Notes in Computer Science, vol. 6523/2011, pp 51–61 (2011)

Sihn K.H., Baik, H., Kim, J.T., Bae, S., Song, H.J.: Novel approaches to parallel H.264 decoder on symmetric multicore systems. IEEE International Conference on Acoustic, Speech and Signal Processing (ICASSP), pp. 2017–2020 (2009)

Su, H., Zhang, C., Chai, J., Yang, Q.: An efficient parallel deblocking filter based on GPU: implementation and optimization. IEEE Pacific Rim Conference on Communications, Computers and Signal Processing, pp. 280–285 (2011)

Ciric, V., Milentijevic, I.: Area-time tradeoffs in H.264/AVC deblocking filter design for mobile devices. International Symposium on Signal Processing and its Applications, pp. 1–4 (2007)

Ernst, E.G.: Architecture design of a scalable adaptive deblocking filter for H.264/AVC. MSc Dissertation, Rochester Institute of Technology, NY, pp. 1–89 (2007)

Tsai, T.h., Pan, Y.n.: High efficient H.264/AVC deblocking filter architecture for real-time QFHD. IEEE Transactions on Consumer Electronics, vol. 55, no. 4, pp. 2248–2256, November 2009

Rosa, V.S., Susin, A.A., Bampi, S.: An HDTV H.264 deblocking filter in FPGA with RGB video output. IEEE International Conference on Very Large Scale Integration (VLSI), pp. 308–311 (2007)

Parlak, M., Hamzaouglu, I.: Low power H.264 deblocking filter hardware implementations. IEEE Transactions on Consumer Electronics, vol. 54, no. 2, pp. 808–816 (2008)

Correa, G., Agostini, L., Cruz, L.: A fast FPGA implementation of the inter-layer deblocking filter for H.264/SVC. Conference on Telecommunications, pp. 1–4 (2009)

Loukil, H., Atitallah, A.B., Masmoudi, N.: Hardware architecture for H.264/AVC deblocking filter algorithm. International Multi-Conference on Systems, Signals and Devices, pp. 1–6 (2009)

Khraisha, R., Lee, J.: A scalable H.264/AVC deblocking filter architecture using dynamic partial reconfiguration. IEEE International Conference on Acoustic, Speech and Signal Processing (ASSP), pp. 1566–1569 (2010)

Silva, T., Cruz, L.A., Agostini, L.: A novel macroblock-level filtering up sampling architecture for H.264/AVC scalable extension. Proccedings of the 23rd Symposium on Integrated Circuits and System Design, pp. 163–167 (2010)

Messaoudi, K., Bourennane, E., Toumi, S., Ochoa, G.: Performance comparison of two hardware implementations of the deblocking filter used in H.264 by changing the utilized data width. International Workshop on Systems, Signal Processing and their Applications (WOSSPA), pp. 55–58 (2011)

Chen, Q., Zheng, W., Fang, J., Luo, K., Shi, B., Zhang, M., Zhang, X.: A pipelined hardware architecture of deblocking filter in H.264/AVC. International Conference on Communications and Networking in China, pp. 815–819 (2008)

Xu, K., Choy, C.S.: A five-stage pipeline, 204 cycles/MB, single-port SRAM-based deblocking filter for H.264/AVC. IEEE Transactions on Circuits Systems Video Technology, vol. 18, no. 3, pp. 363–374 (2008)

Chien, C.A., Chang, H.C., Guo, J.I.: A high throughput deblocking filter design supporting multiple video coding standards. IEEE International Symposium on Circuits and Systems (ISCAS), pp. 2377–2380 (2009)

Min, K.Y., Chong, J.W.: A memory efficient architecture of deblocking filter in H.264/AVC using hybrid processing order. International Soc Design Conference (ISOOC), pp. 67–70 (2009)

Lin, Y.: A two-result-per-cycle deblocking filter architecture for QFHD H.264/AVC decoder. IEEE Transactions on Very Large Scale Integration (VLSI) System, vol. 17, no. 6, pp. 838–843 (2009)

Torabi, M., Vafaee, A., Movahhedinia, N.: A fast architecture for deblocking filter in H.264/AVC using clock cycles saving process. International Conference on Multimedia, Signal Processing and Communication Technologies (IMPACT), pp. 324–327 (2009)

Zhou, J., Zhou, D., Zhang, H., Hong, Y., Liu, P., Goto, S.: A 136 cycles/MB, luma-chroma parallelized H.264/AVC deblocking filter for QFHD applications. IEEE International Conference on Multimedia & Expo (ICME), pp. 1134–1137 (2009)

Chen, K.H.: 48 cycles-per-macroblock deblocking filter accelerator for high-resolution H.264/AVC decoding. IET Circuits, Devices & Electronic, vol. 4, no. 3, pp. 196–206 (2010)

Chen, X., Xia, W., Lu, X.: A high-throughput low-power hardware architecture for H.264 deblocking filter. IEEE International Conference on Computer Engineering and Technology, vol. 2, pp. 561–565 (2010)

Chung, H.C., Chen, Z.Y., Chang, P.C.: Low power architecture design and hardware implementations of deblocking filter in H.264/AVC. IEEE International Conference on Consumer Electronics (ICCE), pp. 405–406 (2011)

Acknowledgement

This work was supported by the Spanish Government and the European Union (FEDER funds), under project DREAMS (TEC2011-28666-C04-04).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Cervero, T., Otero, A., López, S. et al. A scalable H.264/AVC deblocking filter architecture. J Real-Time Image Proc 12, 81–105 (2016). https://doi.org/10.1007/s11554-013-0359-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11554-013-0359-9