Abstract

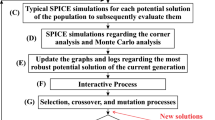

The hybrid CMOS molecular (CMOL) circuit, which combines complementary metal–oxide–semiconductor (CMOS) components with nanoscale wires and switches, can exhibit significantly improved performance. In CMOL circuits, the nanodevices, which are called cells, should be placed appropriately and are connected by nanowires. The cells should be connected such that they follow the shortest path. This paper presents an efficient method of cell allocation in CMOL circuits with the hybrid CMOS/nanodevice structure; the method is based on a cultural algorithm with chaotic behavior. The optimal model of cell allocation is derived, and the coding of an individual representing a cell allocation is described. Then the cultural algorithm with chaotic behavior is designed to solve the optimal model. The cultural algorithm consists of a population space, a belief space, and a protocol that describes how knowledge is exchanged between the population and belief spaces. In this paper, the evolutionary processes of the population space employ a genetic algorithm in which three populations undergo parallel evolution. The evolutionary processes of the belief space use a chaotic ant colony algorithm. Extensive experiments on cell allocation in benchmark circuits showed that a low area usage can be obtained using the proposed method, and the computation time can be reduced greatly compared to that of a conventional genetic algorithm.

Similar content being viewed by others

References

P. Lin, S. Pi, and Q. Xia, 3D integration of planar crossbar memristive devices with CMOS substrate, Nanotechnology 25(40), 405202 (2014)

N. P. Dasgupta and P. D. Yang, Semiconductor nanowires for photovoltaic and photoelectrochemical energy conversion, Front. Phys. 9(3), 289 (2014)

Z. L. Pan, L. Chen, G. Z. Zhang, and P. H. Wu, Detecting the micro-defects in the GaAs materials by time resolved emissions, Chin. Sci. Bull. 59(16), 1838 (2014)

A. Sulaev, M. Zeng, S. Q. Shen, S. K. Cho, W. G. Zhu, Y. P. Feng, S. V. Eremeev, Y. Kawazoe, L. Shen, and L. Wang, Electrically tunable in-plane anisotropic magnetoresistance in topological insulator BiSbTeSe2 nanodevices, Nano Lett. 15(3), 2061 (2015)

R. Tenne, Recent advances in the research of inorganic nanotubes and fullerene-like nanoparticles, Front. Phys. 9(3), 370 (2014)

Z. L. Pan, L. Chen, G. Z. Zhang, and P. H. Wu, A singlephoton fault-detection method for nanocircuits that use GaN material, Science China-Technological Sciences, 57(2), 270 (2014)

C. Dong, W. Wang, and S. Haruehanroengra, Efficient logic architectures for CMOL nanoelectronic circuits, Micro & Nano Lett. 1(2), 74 (2006)

D. B. Strukov and K. K. Likharev, CMOL FPGA: A reconfigurable architecture for hybrid digital circuits with twoterminal nanodevices, Nanotechnology 16(6), 888 (2005)

Z. Abid and M. Liu, 3D integration of CMOL structures for FPGA applications, IEEE Trans. Comput. 60(4), 463 (2011)

M. S. Zaveri and D. Hammerstrom, CMOL/CMOS implementations of bayesian polytree inference: Digital and mixed-signal architectures and performance/price, IEEE Trans. NanoTechnol. 9(2), 194 (2010)

A. Afifi, A. Ayatollahi, and F. Raissi, CMOL implementation of spiking neurons and spike-timing dependent plasticity, International Journal of Circuit Theory and Applications 39(4), 357 (2011)

Z. Abid, A. Almaaitah, M. Barua, and W. Wang, Efficient CMOL gate designs for cryptography applications, IEEE Trans. NanoTechnol. 8(3), 315 (2009)

G. Chen, X. Y. Song, and P. Hu, A theoretical investigation on CMOL FPGA cell assignment problem, IEEE Trans. NanoTechnol. 8(3), 322 (2009)

W. N. Hung, C. Gao, X. Song, and D. Hammerstrom, Defect-tolerant CMOL cell assignment via satisfiability, IEEE Sens. J. 8(6), 823 (2008)

Z. Chu, Y. Xia, W. N. Hung, and L. Wang, A memetic approach for nanoscale hybrid circuit cell mapping, 13th Euromicro Conference on Digital System Design: Architectures, Methods and Tools, Lille, France, pp 681–688 (2010)

Z. Chu, Y. Xia, L. Wang, and M. Hu, CMOL cell assignment based on dynamic interchange, IEEE 8th International Conference on ASIC, Changsha, China, 921–924 (2009)

X. J. Wang and L. Y. Wang, A pseudo-boolean programming approach for CMOL cell assignment, IEEE International Conference on Electronics, Communications and Control, Ningbo, China, pp 1265–1268 (2011)

M. H. Magnusson, B. J. Ohlsson, M. T. Bjork, K. A. Dick, M. T. Borgström, K. Deppert, and L. Samuelson, Semiconductor nanostructures enabled by aerosol technology, Front. Phys. 9(3), 398 (2014)

K. Shao, N. Ding, S. Huang, S. Ren, Y. Zhang, Y. Kuang, Y. Guo, H. Ma, S. An, Y. Li, and C. Jiang, Smart nanodevice combined tumor-specific vector with cellular microenvironment-triggered property for highly effective antiglioma therapy, ACS Nano 8(2), 1191 (2014)

H. Y. Fan, S. Wang, and L. Y. Hu, Evolution of the singlemode squeezed vacuum state in amplitude dissipative channel, Front. Phys. 9(1), 74 (2014)

M. Z. Ali and R. G. Reynolds, Cultural algorithms: A Tabu search approach for the optimization of engineering design problems, Soft Comput. 18(8), 1631 (2014)

Q. F. Luo, Y. Q. Zhou, P. G. Guo, and X. Chen, Functional network design using parallel cultural algorithm, Appl. Math. Inf. Sci. 8(4), 1949 (2014)

S. Srinivasan and S. Ramakrishnan, A social intelligent system for multi-objective optimization of classification rules using cultural algorithms, Computing 95(4), 327 (2013)

E. M. Sentovich, K. J. Singh, and L. Lavagno, SIS: A system for sequential circuit synthesis, Technical Report UCB/ERL M92/41, University of California, Berkeley, 1992

D. B. Strukov and K. K. Likharev, A reconfigurable architecture for hybrid CMOS/nanodevice circuits, 14th ACM International Symposium on Field Programmable, New York, pp 131–140 (2006)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Pan, ZL., Chen, L. & Zhang, GZ. Efficient design method for cell allocation in hybrid CMOS/nanodevices using a cultural algorithm with chaotic behavior. Front. Phys. 11, 116201 (2016). https://doi.org/10.1007/s11467-015-0531-8

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s11467-015-0531-8