Abstract

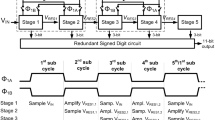

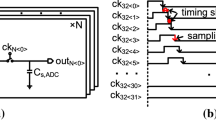

A 32-bit pipeline accumulator with carry ripple topology is implemented for direct digital frequency synthesizer. To increase the throughout while hold down the area and power consumption, a method to reduce the number of the pre-skewing registers is proposed. The number is reduced to 29% of a conventional pipeline accumulator. The propagation delay versus bias current of the adder circuit with different size transistors is investigated. We analyze the delay by employing the open circuit time constant method. Compared to the simulation results, the maximum error is less than ±8%. A method to optimum the design of the adder based on the propagation delay is discussed. The clock traces for the 32-bit adder are heavily loaded, as there are 40 registers being connected to them. Moreover, the differential clock traces, which are much longer than the critical length, should be treated as transmission lines. Thus a clock distribution method and a termination scheme are proposed to get high quality and low skew clock signals. A multiple π-type termination scheme is proposed to match the transmission line impedance. The 32-bit accumulator was measured to work functionally at 5.3 GHz.

Article PDF

Similar content being viewed by others

Avoid common mistakes on your manuscript.

References

Thuries S, Tournier E, Cathelin A, et al. A 6-GHz low-power BiCMOS SiGe:C 0.25 μm direct digital synthesizer. IEEE Microwave Wireless Compon Lett, 2008, 18: 46–48

Bhansali P, Hosseini K, Kennedy M P. Performance analysis of low power high speed pipelined adders for digital ΣΔ modulators. Electron Lett, 2006, 42: 1442–1444

Strollo A G M, Caro D D, Petra N. A 630 MHz, 76 mW direct digital frequency synthesizer using enhanced ROM compression technique. IEEE J Solid-State Circuits, 2007, 42: 350–360

Yeoh H C, Jung J H, Jung Y H, et al. A 1.3-GHz 350-mW hybrid direct digital frequency synthesizer in 90-nm CMOS. IEEE J Solid-State Circuits, 2010, 45: 1845–1855

Kim Y S, Kang S-M. In: Sowers J, Thorburn M, eds. A High Speed Low-power Accumulator for Direct Digital Frequency Synthesizer. In: IEEE MTT-S Int Microw Symp Dig, 2006 June 11–16, San Francisco, CA. 502–505

Alioto M, Palumbo G. CML and ECL: Optimized design and comparison. IEEE Trans Circuits Syst Fundam Theory Appl, 1999, 46: 1330–1341

Rodwell M J W, Urteaga M, Betser Y, et al. Scaling of InGaAs/InAlAs HBTs for high speed mixed-signal and mm-wave ICs. Int J High Speed Electron Syst, 2001, 11: 159–215

Bogatin E. Signal Integrity: Simplified. Beijing: Publishing House of Electronics Industry, 2007

Lu F, Samueli H, Yuan J, et al. A 700-MHz 24-b pipelined accumulator in 1.2-μm CMOS for application as a numerically controlled oscillator. IEEE J Solid-State Circuits, 1993, 28: 878–886

Turner S E, Elder R B, Jansen D S, et al. 4-bit adder-accumulator at 41-GHz clock frequency in InP DHBT technology. IEEE Microwave Wireless Compon Lett, 2005, 4: 144–146

Laemmle B, Wagner C, Knapp H, et al. High speed low power phase accumulators for DDS applications in SiGe bipolar technology. In: IEEE Bipolar/BiCMOS Circuits and Technol Meeting, 2009 Oct. 12–14, Capri, Italy. 162–165

Author information

Authors and Affiliations

Corresponding authors

Additional information

This article is published with open access at Springerlink.com

Rights and permissions

This article is published under an open access license. Please check the 'Copyright Information' section either on this page or in the PDF for details of this license and what re-use is permitted. If your intended use exceeds what is permitted by the license or if you are unable to locate the licence and re-use information, please contact the Rights and Permissions team.

About this article

Cite this article

Chen, J., Wu, D., Zhou, L. et al. A 5.3-GHz 32-bit accumulator designed for direct digital frequency synthesizer. Chin. Sci. Bull. 57, 2480–2487 (2012). https://doi.org/10.1007/s11434-012-5157-4

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11434-012-5157-4