Abstract

To achieve a high product quality for nano-scale systems, both realistic defect mechanisms and process variations must be taken into account. While existing approaches for variation-aware digital testing either restrict themselves to special classes of defects or assume given probability distributions to model variabilities, the proposed approach combines defect-oriented testing with statistical library characterization. It uses Monte Carlo simulations at electrical level to extract delay distributions of cells in the presence of defects and for the defect-free case. This allows distinguishing the effects of process variations on the cell delay from defectinduced cell delays under process variations. To provide a suitable interface for test algorithms at higher levels of abstraction, the distributions are represented as histograms and stored in a histogram data base (HDB). Thus, the computationally expensive defect analysis needs to be performed only once as a preprocessing step for library characterization, and statistical test algorithms do not require any low level information beyond the HDB. The generation of the HDB is demonstrated for primitive cells in 45 nm technology.

Similar content being viewed by others

References

ITRS. International Technology Roadmap for Semiconductors. 2009 ed. http://www.itrs.net/Links/2009ITRS/Home2009.htm

Hapke F, Krenz-Baath R, Glowatz A, et al. Defect-oriented cell-aware ATPG and fault simulation for industrial cell libraries and designs. In: Proceedings of IEEE International Test Conference, Austin, Texas, USA, 2009. Paper 1.2

Ferguson F J, Shen J. Extraction and simulation of realistic CMOS faults using inductive fault analysis. In: Proceedings of IEEE International Test Conference, Washington DC, USA, 1988. 475–484

Shen J P, Maly W, Ferguson F J. Inductive fault analysis of NMOS and CMOS circuits. IEEE Des Test, 1985, 2: 13–26

Khare J, Maly W. From Contamination to Defects, Faults and Yield Loss. Dordrecht: Kluwer Academic Publishers, 1996

Srivastava A, Sylvester D, Blaauw D. Statistical Analysis and Optimization for VLSI: Timing and Power. New York: Springer, 2005

Stefano B, Bertozzi D, Benini L, et al. Process variation tolerant pipeline design through a placement-aware multiple voltage island design style. In: Proceedings of Design, Automation and Test in Europe, Munich, Germany, 2008. 967–972

Aitken R C. Defect or variation? Characterizing standard cell behavior at 90 nm and below. IEEE Trans Semicond Manuf, 2008, 21: 46–54

Ingelsson U, Al-Hashimi B M, Khursheed S, et al. Process variation-aware test for resistive bridges. IEEE Trans CAD Integr Circ Syst, 2009, 28: 1269–1274

Xiong J, Shi Y, Zolotov V, et al. Statistical multilayer process space coverage for at-speed test. In: Proceedings of Design Automation Conference, San Francisco, CA, USA, 2009. 340–345

DATE Workshop on Process Variability. New techniques for the design and test of nanoscale electronics. In: Proceedings of Design, Automation and Test in Europe, Nice, France, 2009

Gizopoulos D, ed. Advances in Electronic Testing: Challenges and Methodologies (Frontiers in Electronic Testing). New York: Springer, 2006

Menezes N. The good, the bad, and the statistical. In: Proceedings of International Symposium on Physical Design, Austin, Texas, USA, 2007. 168

Sachdev M, Pineda de Gyvez J. Defect-Oriented Testing for Nano-Metric CMOS VLSI Circuits (Frontiers in Electronic Testing). 2nd ed. New York: Springer, 2006

Sylvester D, Agarwal K, Shaha S. Variability in nanometer CMOS: Impact, analysis, and minimization. Integrat VLSI J, 2008, 41: 319–339

Visweswariah C. Fear, uncertainty and statistics. In: Proceedings of International Symposium on Physical Design, Austin, Texas, USA, 2007. 169

Schlichtmann U, Schmidt M, Kinzelbach H, et al. Digital design at a crossroads-how to make statistical design industrially relevant. In: Proceedings of Design, Automation and Test in Europe, Nice, France, 2009. 1542–1547

Bounceur A, Mir S, Simeu E, et al. Estimation of Test Metrics for the Optimisation of Analogue Circuit Testing. J Electron Test Theory Appl, 2007, 23: 471–484

Devarayanadurg G, Goteti P, Soma M. Hierarchy based statistical fault simulation of mixed-signal ICs. In: Proceedings of IEEE International Test Conference, Washington DC, USA, 1996. 521–527

Gomes A V, Voorakaranam R, Chatterjee A. Modular fault simulation of mixed signal circuits with fault ranking by severity. In: Proceedings of International Symposium on Defect and Fault-Tolerance in VLSI Systems, Austin, TX, USA, 1998. 341–348

Khouas A, Derieux A. Fault simulation for analog circuits under parameter variations. J Electron Test Theory Appl, 2000, 16: 269–278

Liu F, Ozev S. Statistical test development for analog circuits under high process variations. IEEE Trans CAD Integr Circ Syst, 2007, 26: 1465–1477

Peralta J, Peretti G, Romero E, et al. A new performance characterization of transient analysis method. Int J Electron Commun Comput Engineer, 2009, 1: 12–19

Saab K, Ben-Hamida N, Kaminska B. Parametric fault simulation and test vector generation. In: Proceedings of Design, Automation and Test in Europe, Paris, France, 2000. 650–657

Spinks S J, Chalk C D, Bell I M, et al. Generation and verification of tests for analog circuits subject to process parameter deviations. J Electron Test Theory Appl, 2004, 20: 11–23

Liou J J, Krstic A, Jiang Y M, et al. Modeling, testing, and analysis for delay defects and noise effects in deep submicron devices. IEEE Trans CAD Integr Circ Syst, 2003, 22: 756–769

Yilmaz M, Chakrabarty K, Tehranipoor M. Interconnect-aware and layout-oriented test pattern selection for small-delay defects. In: Proceedings of IEEE International Test Conference, Santa Clara, CA, USA, 2008. Paper 28.3

Santos M B, Teixeira J P. Defect-oriented mixed-level fault simulation of digital systems-on-a-chip using HDL. In: Proceedings of Design, Automation and Test in Europe, Munich, Germany, 1999. 549–553

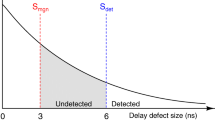

Sato Y, Hamada S, Maeda T, et al. Invisible delay quality-SDQM model lights up what could not be seen. In: Proceedings of IEEE International Test Conference, Austin, TX, USA, 2005. Paper 47.1

Pramanick A K, Reddy S M. On the detection of delay faults. In: Proceedings of IEEE International Test Conference, Washington DC, USA, 1988. 845–856

Zeng J, Abadir M S, Kolhatkar A, et al. On correlating structural tests with functional tests for speed binning of high performance design. In: Proceedings of IEEE International Test Conference, Charlotte, NC, USA, 2004. 31–37

Zolotov V, Visweswariah C, Xiong J. Voltage binning under process variation. In: Proceedings of International Conference on Computer-Aided Design, San Jose, CA, USA, 2009. 425–432

Straube B, Müller B, Vermeiren W, et al. Analogue fault simulation by aFSIM. In: Proceedings of Design, Automation and Test in Europe Conference and Exhibition-User Forum, Paris, France, 2000. 205–210

Nangate 45 nm Open Cell Library. http://www.nangate.com

Hillebrecht S, Polian I, Engelke P, et al. Extraction, simulation and test generation for interconnect open defects based on enhanced aggressor-victim model. In: Proceedings of IEEE International Test Conference, Santa Clara, CA, USA, 2008. Paper 33.3

Rodriguez-Montanes R, Pineda de Gyvez J, Volf P. Resistance characterization for weak open defects. IEEE Des Test Comput, 2002, 19: 18–26

Rodriguez-Montanes R, Bruls E M J G, Figueras J. Bridging defects resistance in the metal layer of a CMOS process. J Electron Test Theory Appl, 2006, 8: 35–46

Hirata A, Onodera H, Tamaru K. Estimation of propagation delay considering short-circuit current for static CMOS gates. IEEE Trans Circ Syst I Fund Theor Appl, 1998, 45: 1194–1198

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Hopsch, F., Becker, B., Hellebrand, S. et al. Variation-aware fault modeling. Sci. China Inf. Sci. 54, 1813–1826 (2011). https://doi.org/10.1007/s11432-011-4367-8

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11432-011-4367-8