Abstract

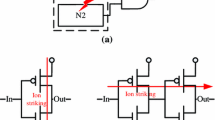

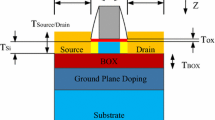

Single-event transient pulse quenching (Quenching effect) is employed to effectively mitigate W SET (SET pulse width). It enhanced along with the increased charge sharing which is norm for future advanced technologies. As technology scales, parameter variation is another serious issue that significantly affects circuit’s performance and single-event response. Monte Carlo simulations combined with TCAD (Technology Computer-Aided Design) simulations are conducted on a six-stage inverter chain to identify and quantify the impact of charge sharing and parameter variation on pulse quenching. Studies show that charge sharing induce a wider W SET spread range. The difference of W SET range between no quenching and quenching is smaller in NMOS (N-Channel Metal-Oxide-Semiconductor Field-Effect Transistor) simulation than that in PMOS’ (P-Channel Metal-Oxide-Semiconductor Field-Effect Transistor), so that from parameter variation view, quenching is beneficial in PMOS SET mitigation. The individual parameter analysis indicates that gate oxide thickness (TOXE) and channel length variation (XL) mostly affect SET response of combinational circuits. They bring 14.58% and 19.73% average W SET difference probabilities for no-quenching cases, and 105.56% and 123.32% for quenching cases.

Similar content being viewed by others

References

Amusan O A, Witulski A F, Massengill L W, et al. Charge collection and charge sharing in a 130 nm CMOS technology. IEEE Trans Nucl Sci, 2006, 53(6): 3253–3258

Giot D, Roche P, Gasiot G, et al. Heavy ion testing and 3D simulations of Multiple Cell Upset in 65nm standard SRAMs. IEEE RADECS 9th European Conference on, 2007. 1–6

Amusan O A, Massengill L W, Baze M P, et al. Single event upsets in Deep-Submicrometer technologies due to charge sharing. IEEE Trans Dev Mater Reliab, 2008, 8(3): 582–589

Lawrence R K, Kelly A T. Single event effect induced multiple-cell upsets in a commercial 90 nm CMOS digital technology. IEEE Trans Nucl Sci, 2008, 55(6): 3367–3374

Black J D, Ball D R, Robinson W H, et al. Characterizing SRAM single event upset in terms of single and multiple node charge collection. IEEE Trans Nucl Sci, 2008, 5(6): 2943–2947

Li D W, Qin J R, Chen S M. The supply voltage scaled dependency of the recovery of single event upset in advanced complementary metal oxide semiconductor static random-access memory cells. Chin Phys B, 2013, 22(2): 029402

Qin J R, Chen S M, Liang B, et al. Recovery of single event upset in advanced complementary metal oxide semiconductor static random access memory cells. Chin Phys B, 2012, 21(2): 029401

Qin J R, Li D W, Chen S M. A novel layout for single event upset mitigation in advanced CMOS SRAM cells. Sci China Tech Sci, 2013, 56: 143–147

Qin J R, Chen S M, Liu B W, et al. Research on single event transient pulse quenching effect in 90 nm CMOS technology. Sci China Tech Sci, 2011, 54: 3064–3069

Atkinson N M, Witulski A F, Holman W T, et al. Layout technique for single-event transient mitigation via pulse quenching. IEEE Trans Nucl Sci, 2011, 58(3): 885–890

Ahlbin J R, Massengill L W, Bhuva B L, et al. Single-event transient pulse quenching in advanced CMOS logic circuits. IEEE Trans Nucl Sci, 2009, 56(6): 3050–3056

Chen J J, Chen S M, Liang B, et al. Simulation study of the layout technique for P-hit Single-Event transient mitigation via the source isolation. IEEE Trans Dev Mater Reliab, 2012, 12(2): 501–509

Duvall S G. Statistical circuit modeling and optimization. In Proc 5th Int Workshop Statistical Metrology, 2000. 56–63

International Technology Roadmap for Semiconductors, 2006. [Online]. http://www.itrs.net/Links/2006Update/2006UpdateFinal.htm.

Stolk P A, Widdershoven F P, Klaassen D. B M. Modeling statistical dopant fluctuations in MOS transistors. IEEE Trans Elec Dev, 1998, 45(9): 1960–1971

Borkar S. Designing reliable systems from unreliable components: the challenges of transistor variability and degradation. IEEE Micro, 2005, 25(6): 10–16

Arora N D, Rios R, Cheng-Linag H. Modeling the polysilicon depletion effect and its impact on submicrometer CMOS circuit performance. IEEE Trans Elec Dev, 1995, 42(5): 935–943

Shyu J B, Temes G C, Krummenacher F. Random error effects in matched MOS capacitors and current sources. IEEE J Solid-State Circuits, 1984, 19(6): 948–956

Asenov A, Kaya S, Brown A R. Intrinsic parameter fluctuations in decananometer MOSFETs introduced by gate line edge roughness. IEEE Trans Elec Dev, 2003, 50(5): 1254–1260

Duvall S G. Statistical Circuit Modeling and Optimization. 5th International Workshop on Statistical Metrology, 2000. 56–63

Balasubramanian A, Fleming P R, Bhuva B L, et al. Effects of random dopant fluctuations (RDF) on the single event vulnerability of 90 and 65 nm CMOS technologies. IEEE Trans Nucl Sci, 2007, 54(6): 2400–2406

Balasubramanian A, Fleming P R, Bhuva B L. et al. Implications of dopant-fluctuation-induced vt variations on the radiation hardness of deep submicrometer CMOS SRAMs. IEEE Trans Dev Mater Reliab, 2008, 8(1): 135–144

Kauppila A V, Bhuva B L, Kauppila J S. et al. Impact of process variations on SRAM single event upsets. IEEE Trans Nucl Sci, 2011, 58(3): 834–839

Kauppila A V, Ball D R, Bhuva B L. et al. Impact of process variations on upset reversal in a 65 nm flip-flop. IEEE Trans Nucl Sci, 2012, 59(4): 886–892

Kauppila A V, Bhuva B L, Massengill L W. et al. Impact of process variations and charge sharing on the single-event-upset response of flip-flops. IEEE Trans Nucl Sci, 2011, 58(6): 2658–2663

Atkinson N M, Ahlbin J R, Witulski A F, et al. Effect of transistor density and charge sharing on single-event transients in 90-nm bulk CMOS. IEEE Trans Nucl Sci, 2011, 58(6): 2578–2584

Ahlbin J R, Gadlage M J, Ball D R, et al. The effect of layout topology on single-event transient pulse quenching in a 65 nm bulk CMOS process. IEEE Trans Nucl Sci, 2010, 57(6): 3380–3385

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Wang, T., Xiao, L., Zhou, B. et al. Analysis of process variations impact on the single-event transient quenching in 65 nm CMOS combinational circuits. Sci. China Technol. Sci. 57, 322–331 (2014). https://doi.org/10.1007/s11431-013-5441-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11431-013-5441-9