Abstract

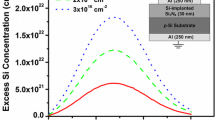

The combination of capacitance- and current-voltage (CV/IV) measurements is used to analyze trap generation in silicon-nanocrystal memory devices during Fowler-Nordheim (FN) programming/erasing cycling. CV and IV curves are measured after certain P/E cycles. The flatband voltage (V fb) and the threshold voltage (V th) are extracted from CV curves by solving one-dimensional Schrödinger and Poisson equations. Both hole and electron trappings are observed in the tunneling SiO2. They show up in the accumulation and the inversion, respectively. By fitting FN tunneling current, the area densities of cycling-induced electron traps in the blocking oxide and in the tunneling oxide are finally determined.

Similar content being viewed by others

References

Tiwari S, Rana F, Hanafi H, et al. A silicon nanocrystals based memory. Appl Phys Lett, 1996; 68: 1377–1379

Wang L, Sun H F, Zhou H H, et al. Preparation of NiFe binary alloy nanocrystals for nonvolatile memory applications. Sci China Tech Sci, 2010; 53: 2320–2322

Choi S, Choi H, Kim T, et al. High density silicon nanocrystal embedded in SiN prepared by low energy (<500 eV) SiH4 plasma immersion ion implantation for non-volatile memory applications. In: IEEE IEDM Tech Dig, San Francisco, 2005. 166–169

Ng C Y, Chen T P, Yang M. Impact of programming mechanisms on the performance and reliability of nonvolatile memory devices based on Si nanocrystals. IEEE Trans Electron Devices, 2006; 53: 663–667

Salvo B, Gerardi C, Schaijk R, et al. Performance and reliability features of advanced nonvolatile memories based on discrete traps (silicon nanocrystals, SONOS). IEEE Trans Device Mater Reliab, 2004; 4: 377–389

Yang X, Wang Y, Zhang M, et al. Analysis of trap generation during programming/erasing cycling in silicon nanocrystal memory devices. Semi Sci Tech, 2011; 26: 045011–045016

Ielmini D, Spinelli A S, Rigamonti M A, et al. Modeling of SILC based on electron and hole tunneling Part I: Transient effects. IEEE Trans Electron Devices, 2000; 47: 1258–1265

Wang Y, Yang X, Wang Q, et al. Optimization of silicon nanocrystals growth process by low pressure chemical vapor deposition for non-volatile memory application. Thin Solid Films, 2011; 519: 2146–2149

Hareland S A, Krishnamurthy S, Jallepalli S, et al. A computationally efficient model for inversion layer quantization effects in deep submicron N-channel mosfet’s. IEEE Trans Electron Devices, 1996; 43: 90–96

Hansch W, Vogelsang T, Kircher R, et al. Carrier transport near the Si/SiO2 interface of a mosfet. Solid State Electron, 1989; 32: 839–849

Weinberg Z A. On tunneling on metal-oxide-silicon structures. J App Phys, 1982; 53: 5052–5056

Ning T H, Osburn C M, Yu H N, et al. Emission probability of hot electrons from silicon into silicon dioxide. J App Phys, 1977; 48: 286–293

Mohammad S N, Fiorenza G, Acovic A, et al. Fowler-Nordheim tunneling of carriers in MOS transistors: Two-dimensional simulation of gate current employing FIELDAY. Solid-State Electron, 1995; 38: 807–814

Oh S J, Yeow Y T. Voltage shifts of Fowler-Nordheim tunneling J-V plots in thin gate oxide MOS structures due to trapped charges. Solid-State Electron, 1989; 32: 507–511

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Yang, X., Zhang, M., Wang, Y. et al. Analyzing trap generation in silicon-nanocrystal memory devices using capacitance and current measurement. Sci. China Technol. Sci. 55, 588–593 (2012). https://doi.org/10.1007/s11431-011-4694-4

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11431-011-4694-4