Abstract

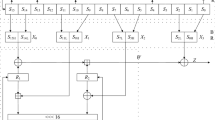

In the communication systems, GOLAY code is constantly playing an imperative part as a perfect linear error correcting code of the system. This code is utilized in the forward error correcting appliance for communication acquaintances. Accordingly, in this work, a GOLAY code technique is implemented by designing a novel compact IC (integrated chip) by the use of FFPPE (Flexible Floating Point Processing Element) which is the significant entity for multiplication, subtraction, addition, (ALU) method. Binary data architecture is employed on Cyclic-Redundancy Check methodology with the use of encoder and decoder. Further, the VHDL is used to verify the GCEA (GOLAY code encoder architecture) on FPGA (Field Programmable Gate Array) devices in Xilinx ISE 14.2. The security of the system is increased and the circuit’s complexity level is optimized through this designed architecture. It identifies various types of errors during the data transmission. The encoder and decoder is modified by adding the message bits in the GOLAY and extended GOLAY code techniques. Finally, the performance measures are estimated for the proposed scheme in terms of look up tables (LUT) optimization, area, power, speed, circuit complexity, power utilization, slice count, clock frequency. Comprehensive comparative analysis of the proposed and existing system promotes the understanding of the effectiveness of the proposed system. These parameters include the LUT count, synthesized frequency in MHZ, clock, area as well as speed. The results exhibited that the proposed methodology is efficient than the conventional techniques in enhancing the system security.

Similar content being viewed by others

Data Availability

https://doi.org/10.1109/mwc.001.1900494, https://doi.org/10.1109/tvt.2020.3007521, https://doi.org/10.15598/aeee.v16i4.2735, https://doi.org/10.1109/jsyst.2020.2981366, https://doi.org/10.1109/tvlsi.2016.2620998, https://doi.org/10.1109/tcomm.2020.3006212, https://doi.org/10.1109/tvlsi.2018.2837220, https://doi.org/10.1016/j.vlsi.2017.11.010, https://doi.org/10.1049/el.2017.1037, https://doi.org/10.1109/lcomm.2018.2850772, https://doi.org/10.1109/jbhi.2020.2988449, https://doi.org/10.1049/joe.2014.0055, https://doi.org/10.1109/tit.2020.2978383, https://doi.org/10.1007/978-981-10-7191-1_13, https://doi.org/10.1109/tvlsi.2015.2465846, https://doi.org/10.1109/siitme.2018.8599233, https://doi.org/10.5120/ijca2016912242, https://doi.org/10.1109/eiconcit.2018.8878513, https://doi.org/10.1109/54.922807, https://doi.org/10.1109/tc.2003.1234528, https://doi.org/10.1109/tvlsi.2014.2346712.

Code Availability

Not Applicable.

References

Wu, Y., Gao, X., Zhou, S., Yang, W., Polyanskiy, Y., & Caire, G. (2020). Massive access for future wireless communication systems. IEEE Wireless Communications, 27, 148–156.

Yang, L., Yang, J., Xie, W., Hasna, M. O., Tsiftsis, T., & Di Renzo, M. (2020). Secrecy performance analysis of RIS-aided wireless communication systems. IEEE Transactions on Vehicular Technology, 69, 12296–12300.

Nazeri, M., & Rezai, A. (2018). A novel and fast hardware implementation for Golay Code encoder. Advances in Electrical and Electronic Engineering, 16, 521–527.

Xiong, H., Bian, R., Li, Y., Du, Z., & Mai, Z. (2020). Fault-tolerant GNSS/SINS/DVL/CNS integrated navigation and positioning mechanism based on adaptive information sharing factors. IEEE Systems Journal, 14, 3744–3754.

Abbas, S. M., Fan, Y., Chen, J., & Tsui, C.-Y. (2017). High-throughput and energy-efficient belief propagation polar code decoder. IEEE Transactions on very large scale integration (VLSI) systems, 25, 1098–1111.

Bioglio, V., Gabry, F., Land, I., & Belfiore, J.-C. (2020). Multi-kernel polar codes: Concept and design principles. IEEE Transactions on Communications, 68, 5350–5362.

Gracia-Morán, J., Saiz-Adalid, L. J., Gil-Tomás, D., & Gil-Vicente, P. J. (2018). Improving error correction codes for multiple-cell upsets in space applications. IEEE Transactions systems on very large scale integration (VLSI). https://doi.org/10.1109/TVLSI.2018.2837220

Asif, S., Hossain, M. S., Kong, Y., & Abdul, W. (2018). A fully RNS based ECC processor. Integration, 61, 138–149.

Park, J., Kim, I., & Song, H.-Y. (2017). Construction of parity-check-concatenated polar codes based on minimum Hamming weight codewords. Electronics Letters, 53, 924–926.

Basha, A. N., & Srinivasa, R. T. (2018). Single and double-adjacent error correcting parallel decoder using Golay codes. International Journal for Innovative Engineering and Management Research (IJIEMR), 7, 73–76.

Vishala, P., & Kumar, B. R. (2018). Implementation of error correction using Golay code. International Journal for Innovative Engineering and Management Research (IJIEMR), 7, 200–204.

Elkelesh, A., Ebada, M., Cammerer, S., & ten Brink, S. (2018). Belief propagation list decoding of polar codes. IEEE Communications Letters, 22, 1536–1539.

Rahman, M. S., Khalil, I., & Yi, X. (2020). Reversible biosignal steganography approach for authenticating biosignals using extended binary Golay code. IEEE journal of biomedical and health informatics, 25, 35–46.

Jain, T., & Singh, S. (2016). A litrature review on Golay code encoder and decoder in digital communication. International Journal of Engineering and Management Research (IJEMR), 6, 470–473.

J. A. Briffa and S. Wesemeyer (2018) "SimCommSys: Taking the errors out of error-correcting code simulations," arXiv preprint arXiv:1802.08522.

A. S. Bhatia and A. Kumar (2018) "McEliece cryptosystem based on extended Golay code," arXiv preprint arXiv:1811.06246.

Athira, S. (2016). VLSI implementation of efficient and high speed Golay code encoder-decoder. International Journal of Engineering Science and Computing (IJESC), 6, 7769–7778.

Lin, S., Abdel-Ghaffar, K., Li, J., & Liu, K. (2020). A scheme for collective encoding and iterative soft-decision decoding of cyclic codes of prime lengths: Applications to Reed-Solomon, BCH, and quadratic residue codes. IEEE Transactions on Information Theory, 66, 5358–5378.

Patnaik, S., & Ravi, V. (2018). A built-in self-repair architecture for random access memories. Nanoelectronic materials and devices (pp. 133–146). Springer.

Reviriego, P., Liu, S., Xiao, L., & Maestro, J. A. (2016). An efficient single and double-adjacent error correcting parallel decoder for the (24, 12) extended golay code. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 24, 1603–1606.

I. I. Stoev, A. N. Borodzhieva, and V. A. Mutkov (2018) "FPGA-modelling and simulation of simple encoders for training purposes in the University of Ruse," In: 2018 IEEE 24th International Symposium for Design and Technology in Electronic Packaging (SIITME), pp. 94–98.

Shrivastava, A., & Abdullah, M. (2016). High speed design of FPGA based Golay encoder and decoder. International Journal of Computer Applications, 154, 36–42.

Deshpande, S. D., & Nagachandra, M. (2017). Error correcting code with reconfigurability for binary communication.International Journal of Electronics, Electrical and Computational System (IJEECS), 6, 154–157.

M. Nazeri, A. Rezai, and H. Azis (2018) "An efficient architecture for Golay code encoder," In: 2018 2nd East Indonesia Conference on Computer and Information Technology (EIConCIT), pp. 114–117.

Sprachmann, M. (2001). Automatic generation of parallel CRC circuits. IEEE Design & Test of Computers, 18, 108–114.

Campobello, G., Patane, G., & Russo, M. (2003). Parallel CRC realization. IEEE Transactions on Computers, 52, 1312–1319.

Sarangi, S., & Banerjee, S. (2014). Efficient hardware implementation of encoder and decoder for Golay code. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 23, 1965–1968.

Weng, M. I., & Lee, L. N. (1983). Weighted erasure codec for the (24, 12) extended Golay code. (ed.), Google Patents. US4397022A.

Funding

This research work was not funded by any organization/institute/agency.

Author information

Authors and Affiliations

Contributions

I am RKD hereby state that the manuscript title entitled “design of flexible floating point processing element (FFPPE) architecture based on GOLAY code strategy” submitted to wireless personal communications, i and my co-author NGN confirm that this work is original and has not been published elsewhere, nor is it currently under consideration for publication elsewhere. and i am assistant professor in Marri Laxman Reddy institute of technology & management, Hyderabad, India.

Corresponding author

Ethics declarations

Conflict of interest

I confirm that this work is original and has either not been published elsewhere, or is currently under consideration for publication elsewhere.

Consent to Participate

I confirm that any participants (or their guardians if unable to give informed consent, or next of kin, if deceased) who may be identifiable through the manuscript (such as a case report), have been given an opportunity to review the final manuscript and have provided written consent to publish.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Dhanavath, R.K., Sevyanaik, G.N. Design of Flexible Floating Point Processing Element (FFPPE) Architecture Based on Golay Code Strategy. Wireless Pers Commun 125, 1783–1800 (2022). https://doi.org/10.1007/s11277-022-09634-w

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11277-022-09634-w