Abstract

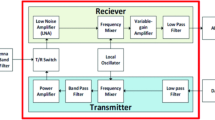

In this paper, an inverter based transconductor using double CMOS pair is proposed for implementation of a reconfigurable analog baseband block consisting of a variable gain amplifier (VGA) and a second order lowpass Gm-C filter. The centre frequency of the filter is varied using current steering DAC. Major contributions of this paper are: proposal for operating the transconductance (Gm) stage and current steering DAC in sub-threshold region in order to minimize the power dissipation, design of variable gain amplifier (VGA) using switched Gm cells with dummy stages, proposal for a digital tuning technique for the filter based on phase comparison method for compensation against process, voltage and temperature variations. The proposed analog baseband block is designed and implemented on TSMC-0.18 μm CMOS process with 1.8 V supply using gm/Id design methodology. The post layout simulation results demonstrate the tunability of the centre frequency from 100 KHz to 20 MHz which meets the requirements of zero IF receivers for SDR applications. The third order input intercept point (IIP3) is found to be 15 dBVp for an input signal of 100 mVp. The power dissipated by the baseband block is 1 mW and 5 mW at 100 KHz and 20 MHz respectively and it requires silicon area of 0.173 mm2. The SFDR over the entire bandwidth is 58 dB. The proposed approach guarantees the upper bound on THD to be-40 dB for 300 mVpp signal swing. The use of inverters with double CMOS pair results in 34 dB higher PSRR compared to those using push pull inverter.

Similar content being viewed by others

References

Giannini, V., Craninckx, J., & Baschirotto, A. (2008). Baseband Analog circuits for Software Defined Radio. New York: Springer. chapter 5.

Laugeois, M. (2004). Reconfigurability Approach on Hardware Design for MTS Terminal. Lausanne: MUMOR Project.

Workshop on Multi-Mode Multi-Band Re-Configurable Systems for 3rd Enhanced Generation Mobile Phones, MUMOR Project Leuven, Belgium, 2004.

Amico, S. D.’ et al. (2004). Low-power reconfigurable baseband block for UMTS/WLAN transmitters, Proc. Of NORCHIP, pp. 103–106, November 2004.

Amico, S. D., Giannini, V., & Baschirotto, A. (2006). A 4th-order active-Gm-RC reconfigurable (UMTS/WLAN) filter. IEEE J.Solid- State Circuits, 41, 1630–1637.

Giannini, V., Craninckx, J., Compiet, J., Come, B., Amico, S. D.’, & Baschirotto A. (2006). Flexible baseband Low-Pass Filter and Variable Gain Amplifier for Software Defined Radio Front End. Proc. Of ESSCIRC2006, pp. 203–206.

Chamla, D., Kaiser, A., Cathelin, A., & Belot, D. (2005). A Gm-C low-pass filter for zero-IF mobile applications with a very wide tuning range. IEEE J. Solid-State Circuits, 40(7), 1443–1450. doi:10.1109/JSSC.2005.847274.

Nauta, B. (1992). A CMOS transconductance-C filter technique for very high frequencies. IEEE J. Solid-State Circuits, 27, 142–153. doi:10.1109/4.127337.

Munoz, F., Torralba, A., Carvajal, R.G., Ramirez-Angulo, J.: “Two new VHF tunable CMOS low-voltage linear transconductors and their application to HF gm-C filter design”, in Proc. ISCAS, May 2000, pp.V-173–176.

Crombez, P., Craninckx, J., Wambacq, P., & Steyaert, M. (2008). A 100-KHz to 20-MHz reconfigurable power-linearity optimized Gm–C biquad in 0.13 m CMOS. IEEE Transactions on Circuits and Systems II: Express Briefs, 55(33), 224–228.

Park, C. S., & Schaumann, R. (1986). A high-frequency CMOS linear transconductance element. IEEE Trans. Circ. Syst, 33, 1132–1137. doi:10.1109/TCS.1986.1085859.

Ramasamy, S., Venkataramani, B., & Anbugeetha, K. (2008). VLSI Implementation of a digitally tunable Gm-C Filter with double CMOS pair 21 st International Conference on VLSI Design, pp. 317–322.

Pavan, S., Tsividis, Y. P., & Nagaraj, K. (2000). Widely programmable high frequency continuous time filters in digital cmos technology. IEEE Journal of Solid-State Circuits, 35, 503–511.

Zhang, F., & Kinget, P. (2005). “Low power programmable-gain CMOS Distributed LNA for ultra-wide-band applications,” in Dig. Of Tech. Papers. Symp. VLSI Circuits, pp. 78–81.

Tsividis, Y. (1995). Mixed Analog Digital VLSI Devices and Technology, p. 66. New York: McGraw-Hill.

Pelgrom, M. J. M., Duinmaijer, A. C. J., & Welbers, A. P. G. (1989). Matching properties of MOS transistors. IEEE J. Solid-State Circuits, 24, 1433–1440. doi:10.1109/JSSC.1989.572629.

Croon, J. A., Rosmeulen, M., Decoutere, S., Sansen, W., & Maes, H. E. (2002). An easy-to-use mismatch model for the MOS transistor. IEEE J. Solid- State Circuits, 37, 1056–64.

Gotarredona, T.S., & Barranco, B.L. (2003). CMOS transistor mismatch model valid from weak to strong inversion, IEEE European Solid-State Circuits Conference, pp. 627–30.

Sümesaglam, T., & Karsilayan, A. I. (2004). A digital automatic tuning technique for high-order continuous-time filters. IEEE Trans. On Circ. and Syst.-I, 51(10), 1975–1984.

Liang, C.-K., Yang, R.-J., & Liu, S.-I. (2008). An all-digital fast-locking programmable DLL-based clock generator. IEEE Trans. Circuits Syst. I Regul. Pap, 55, 361–369. doi:10.1109/TCSI.2007.913612.

Foty, D., Binkley, D., & Bucher, M. (2002). Starting over:Gm/Id-based MOSFET modeling as a basis for modernized analog design methodologies. Nanotech, 1(13), 682–685.

Silveira, F., Flandre, D., & Jespers, P. G. A. (1996). A Gm/ID Based methodology for the Design of CMOS Analog Circuits and Its Application to the Synthesis of a SOI Micro power OTA. IEEE Journal of Solid-State Circuits, 31(9).

Cortes, F. P., Fabris, E., & Bampi, S. (2003). Applying the Gm/ID Method in the analysis and design of Miller amplifier, comparator and Gm-C filter, Proceedings of IFIP VLSI- SoC2003.

Andreani, P., Mattisson, S., & Essink, B. (2000). A CMOS gm -C polyphase filter with high image band rejection, in Proc. ESSCIRC, pp. 244–247.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Ramasamy, S., Venkataramani, B. A Low Power Reconfigurable Analog Baseband Block for Software Defined Radio. J Sign Process Syst 62, 131–144 (2011). https://doi.org/10.1007/s11265-009-0357-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-009-0357-0