Abstract

Multicore processors are becoming ubiquitous, and it is becoming increasingly common to run multiple real-time systems on a shared multicore platform. While this trend helps to reduce cost and to increase performance, it also makes it more challenging to achieve timing guarantees and functional isolation. One approach to achieving functional isolation is to use virtualization. However, virtualization also introduces many challenges to the multicore timing analysis; for instance, the overhead due to cache misses becomes harder to predict, since it depends not only on the direct interference between tasks but also on the indirect interference between virtual processors and the tasks executing on them. In this paper, we present a cache-aware compositional analysis technique that can be used to ensure timing guarantees of components scheduled on a multicore virtualization platform. Our technique improves on previous multicore compositional analyses by accounting for the cache-related overhead in the components’ interfaces, and it addresses the new virtualization-specific challenges in the overhead analysis. To demonstrate the utility of our technique, we report results from an extensive evaluation based on randomly generated workloads.

Similar content being viewed by others

Notes

A preliminary version of this paper has appeared in the Real-Time Systems Symposium (RTSS’13) (Xu et al. 2013).

In this work, we assume that the cores either do not share a cache, or that the shared cache has been partitioned into cache sets that are each accessed exclusively by one core (Kim et al. 2012) We believe that an extension to shared caches is possible, and we plan to consider it in our future work.

We are aware that using a constant maximum value to bound the cache-miss overhead of a task may be conservative, and extensions to a finer granularity, e.g., using program analysis, may be possible. However, as the first step, we keep this assumption to simplify the analysis in this work, and we defer such extensions to our future work.

We say that a compositional analysis method is compatible with the underlying component’s schedulability test it uses if whenever a component \(C\) with a taskset \(\tau \) is deemed schedulable on \(m\) cores by the schedulability test, then \(C\) is also deemed schedulable under an interface with bandwidth no larger than \(m\) by the compositional analysis method.

Here, \(d_k\) and \(t\) refer to \(D_k\) and \(A_k + D_k\) in Easwaran et al. (2009), respectively.

Note that the number of full processors is always bounded from below by \(\lfloor U_i \rfloor \), where \(U_i\) is the total utilization of the tasks in \(\mathcal {D}_i\), and bounded from above by the number of tasks in \(\mathcal {D}_i\) or the number of physical platform (if given), whichever is smaller.

Note that we inflate only the tasks’ WCETs and not the VCPUs’ budgets, since \(\delta ^{\mathsf {crpmd}}_{\mathsf {\tau _k}}\) includes the overhead for reloading the useful cache content of a preempted VCPU when it resumes.

Recall that \(\mathsf {LP}(\tau _k) = \{\tau _i | d_i > d_k\}\).

We assume other factors are same when we discuss one factor’s impact on the cache-aware analysis.

We note that the interfaces given by the hybrid method and the baseline method are the same as the interfaces given by the cache-aware hybrid analysis method and task-centric analysis method proposed in the conference version (Xu et al. 2013), respectively.

References

Barham P, Dragovic B, Fraser K, Hand S, Harris T, Ho A, Neugebauer R, Pratt I, Warfield A (2003) Xen and the art of virtualization. In: SOSP

Baruah S, Baker T (2008) Schedulability analysis of global EDF. Real Time Syst 38(3):223–235

Baruah S, Fisher N (2009) Component-based design in multiprocessor real-time systems. In: ICESS

Bastoni A, Brandenburg BB, Anderson JH (2010) Cache-related preemption and migration delays: empirical approximation and impact on schedulability. In: Proceedings of OSPERT

Basumallick S, Nilsen K (1994) Cache issues in real-time systems. In: LCTES

Bini E, Bertogna M, Baruah S (2009) Virtual multiprocessor platforms: specification and use. In: RTSS

Brandenburg BB (2011) Scheduling and locking in multiprocessor real-time operating systems. PhD thesis, The University of North Carolina at Chapel Hill, Chapel Hill

Brandenburg BB, Leontyev H, Anderson JH (2011) An overview of interrupt accounting techniques for multiprocessor real-time systems. J Syst Archit 57(6):638–654

Bruns F, Traboulsi S, Szczesny D, Gonzalez E, Xu Y, Bilgic A (2010) An evaluation of microkernel-based virtualization for embedded real-time systems. In: ECRTS

Calandrino JM, Leontyev H, Block A, Devi UC, Anderson JH (2006) LITMUS RT: a testbed for empirically comparing real-time multiprocessor schedulers. In: RTSS

Crespo A, Ripoll I, Masmano M (2010) Partitioned embedded architecture based on hypervisor: the XtratuM approach. In: EDCC

Easwaran A, Anand M, Lee I (2007) Compositional analysis framework using EDP resource models. In: RTSS

Easwaran A, Shin I, Lee I (2009) Optimal virtual cluster-based multiprocessor scheduling. Real Time Syst 43(1):25–59

Guan N, Stigge M, Yi W, Yu G (2009) Cache-aware scheduling and analysis for multicores. In: EMSOFT

Hardy D, Piquet T, Puaut I (2009) Using bypass to tighten WCET estimates for multi-core processors with shared instruction caches. In: RTSS

Kim T, Peinado M, Mainar-Ruiz G (2012) System-level protection against cache-based side channel attacks in the cloud. In: USENIX security

Lee J, Phan LTX, Chen S, Sokolsky O, Lee I (2011) Improving resource utilization for compositional scheduling using DPRM interfaces. SIGBED Rev 8(1):38–45

Lee J, Xi S, Chen S, Phan LTX, Gill C, Lee I, Lu C, Sokolsky O (2012) Realizing compositional scheduling through virtualization. In: RTAS

Leontyev H, Anderson JH (2008) A hierarchical multiprocessor bandwidth reservation scheme with timing guarantees. In: ECRTS

Lipari G, Bini E (2010) A framework for hierarchical scheduling on multiprocessors: from application requirements to run-time allocation. In: RTSS

Phan LTX, Xu M, Lee J, Lee I, Sokolsky O (2013) Overhead-aware compositional analysis of real-time systems. In: RTAS

Sha L, Lehoczky JP, Rajkumar R (1986) Solutions for some practical problems in prioritized preemptive scheduling. In: RTSS

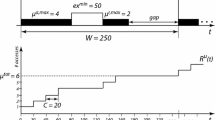

Shin I, Lee I (2003) Periodic resource model for compositional real-time guarantees. In: Proceedings of the 24th IEEE real-time systems symposium (RTSS), Cancun

Shin I, Easwaran A, Lee I (2008) Hierarchical scheduling framework for virtual clustering of multiprocessors. In: ECRTS

Xi S, Xu M, Lu C, Phan LTX, Gill C, Sokolsky O, Lee I (2014) Real-time multi-core virtual machine scheduling in Xen. In: EMSOFT

Xu M, Phan LTX, Lee I, Sokolsky O, Xi S, Lu C, Gill CD (2013) Cache-aware compositional analysis of real-time multicore virtualization platforms. In: RTSS

Acknowledgments

This research was supported in part by the ONR N000141310802, NSF CNS-1329984, NSF CNS-1117185, NSF ECCS-1135630, and The Ministry of Knowledge Economy (MKE), Korea, under the Global Collaborative R&D program supervised by the KIAT (M002300089).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Xu, M., Phan, L.T.X., Sokolsky, O. et al. Cache-aware compositional analysis of real-time multicore virtualization platforms. Real-Time Syst 51, 675–723 (2015). https://doi.org/10.1007/s11241-015-9223-2

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11241-015-9223-2