Abstract

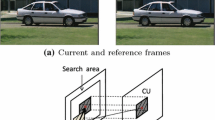

High-Efficiency Video Coding (HEVC) has become popular according to its excellent coding performance, in particular in the case of high-resolution video applications. However, the significant gain in performance is accompanied by a higher encoding complexity compared to the H.264/AVC standard. The motion estimation (ME) is the most time-consuming part that removes temporal redundancy. To reduce the motion estimation complexity, many fast algorithms have been developed in order to minimize search positions and speed up computation but they do not take into account how they can be effectively implemented by hardware. This paper presents a design for the fast ME algorithm with a variable block size of HEVC standard which is the “TZ search”. The design is described in VHDL language and synthesized to Altera Stratix III FPGA. The hardware architecture throughput reaches a processing rate up to 78 million pixels per second at 100 MHz. For the validation proposed design, an IP core is presented using the embedded video system on a programmable chip (SoPC). Finally, compared to other designs existing in the literature, the proposed architecture shows more efficiency in terms of hardware cost and improved performance. This design can be used in ultra-high-definition real-time TV coding (UHD) applications.

Similar content being viewed by others

References

Alcocer E, Gutierrez R, Lopez-Granado O, Malumbres MP (2016) Design and implementation of an efficient hardware integer-motion estimator for an HEVC video encoder. J Real-Time Image Proc. https://doi.org/10.1007/s11554-016-0572-4

Altera DE1-SOC Development Kit: https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=167&No=836

Bross B, Han W, Sullivan G, Ohm JR, Wiegand T (2012) "High efficiency video coding (HEVC) text specification draft 6," JCT VC-H I 003

Byun J, Jung Y, Kim J (2013) Design of integer motion estimator of HEVC for asymmetric motion-partitioning mode and 4K-UHD. Electron Lett 49(18):1142–1143

Cheung CH, Po LM (2002) A novel cross-Diamond search algorithm for fast block motion estimation. IEEE Trans On Circuits Syst Video Technol 12(12):1168–1177

Dinh C, Nguyen T, Pham C, Nguyen P, Duong D, Phung H, Pham T, Nguyen T (2017) ‘A novel parallel hardware architecture for inter motion estimation in HEVC’. J Telecommun Electron Comp Eng (UteM)

Dinh C, Nguyen T, Pham C, Nguyen P, Duong D, Phung H, Pham T, Nguyen T (2017) A novel parallel hardware architecture for inter motion estimation in HEVC. J Telecom Electronic Comput Eng 9:1

Felipe S, Sergio B, Mateus G, Luciano A, Julio M (2012) “Motion vectors merging: low complexity prediction unit decision heuristic for the inter-prediction of HEVC encoders”. In: IEEE Int Conference Multimed Expo, 657–662

Gallant M, Côté G, Kossentini F (1999) An efficient computation-constrained blockbased motion estimation algorithm for low bit rate video coding. IEEE Trans Image Process 8(12)

Hosur P, Ma K (1999) Motion vector field adaptive fast motion estimation. In: Second Int conference on information, communications and signal processing (ICICS), 7–10

Hyang-Mi Y, Jae-Won S (2013) “Fast coding unit decision algorithm based on inter and intra prediction unit termination for HEVC”. In: IEEE International Conference on Consumer Electronics (ICCE), 300–301

Jia L, Tsui C, Au OC, Jia K (2018) A low-power motion estimation architecture for HEVC based on a new sum of absolute difference computation. IEEE Trans Circ Syst Video Tech 1:1

Joginipelly AK, Charalampidis D (2019) Efficient separable convolution using field programmable gate arrays. Microprocess Microsyst 71:102852

Joginipelly AK, Charalampidis D (2020) An efficient circuit for error eduction in logarithmic multiplication for filtering applications. Int J Circ Theory Appl 48(5):809–815

Joint Collaborative Team on Video Coding (JCT-VC) (2017) High efficiency video coding (HEVC) test model 16 (HM 16)

Khemiri R, Kibeya H, Loukil H, Sayadi FE, Atri M, Masmoudi N (2018) Real-time motion estimation diamond search algorithm for the new high efficiency video coding on FPGA. Analog Integr Circ Signal Process 94(2):259–276

Kibeya H, Belghith F, Loukil H, Ben Ayed MA, Masmoudi N (2014) “TZSearch pattern search improvement for HEVC motion estimation modules”. The International Conference on Advanced Technologies for Signal and Frame Processing (ATSIP), Sousse

Kim TS, Rhee CE, Lee H (2019) Fast hardware-based IME with idle cycle and computational redundancy reduction. IEEE Trans Circ Syst Video Tech 1:1

Li X, Wang R, Wang W, Wang Z, Dong S (2014) Fast motion estimation methods for HEVC. In: Proc. IEEE Int Symp on broadband Mult Syst Broadcasting 1–4

Medhat A, Shalaby A, Sayed MS, Elsabrouty M, Mehdipour F (2014). A highly parallel SAD architecture for motion estimation in HEVC encoder. In IEEE Asia Pacific conference circuits system (APCCAS), Ishigaki (280–283). https://doi.org/10.1109/APCCAS.2014.7032774

Medhat A, Shalaby A, Sayed MS (2015) High throughput hardware implementation for motion estimation in HEVC encoder. In: Proc. IEEE 58th Int. Midwest Symp on Circuits and Sys (MWSCAS), 1–4

Mukherjee A (2021) “VLSI Architecture Design of Motion Estimation Block with Hexagon-Diamond Search Pattern for Real-Time Video Processing”, IEEE 18th India Council International Conference (INDICON), https://doi.org/10.1109/INDICON52576.2021.9691531

Nalluri P, Alves LN, Navarro A (2012). Fast motion estimation algorithm for HEVC. In IEEE Int Conf Consumer Electron Berlin, Germany (34–37). https://doi.org/10.1109/ICCE-Berlin.2012.6336494.

Nalluri P, Alves LN, Navarro A (2013). A Novel SAD architecture for variable block size motion estimation in HEVC video coding. In IEEE international symposium on system on chip (SoC) (1–4), Tampere

Nalluri P, Alves LN, Navarro A (2014). High speed SAD architectures for variable block sisze motion estimation in HEVC video coding. In IEEE international conference on image processing (ICIP), Paris (1233–1237)

Nguyen B, Ngo V-D, Nguyen V-T (2014) Asymmetric diamond search pattern for motion estimation in HEVC. In: Proc. IEEE Fifth international conference on communications and electronics (ICCE), 434–439

Nios II Integrated Development Environment: https://www.intel.com/content/www/us/en/products/programmable/processor/nios-ii/design-tools.html?wapkw=Nios%20II%20

Pakdaman F, Gabbouj M, Hashemi MR, Ghanbari M (2018) Fast motion estimation algorithm with efficient memory access for HEVC hardware encoders. In: Proc. 7th European workshop on visual information processing (EUVIP), 1–5

Po L-M, Ma W-C (1996) ‘A novel four-step search algorithm for fast block motion estimation’, IEEE Trans. Circuits and System for Video Tech 6(3):313–317

Richardson IE (2002) Full search motion estimation. In: Richardson IEG (ed) Video codec design. Wiley, New York, pp 99–101

Samet A, Souissi N, Zouch W, Ben Ayed MA, Masmoudi N (2006) New horizontal Diamond search motion estimation algorithm for H.264/AVC. Second Symposium on Communication, Control and Signal Processing, ISCCSP 2006, 13–15, Marrakech, Morocco

Singh K, Ahamed SR (2018) Low power motion estimation algorithm and architecture of HEVC/H.265 for consumer applications. IEEE Trans Consumer Electron 1:1

Sushanta G, Rangababu P (2021) “A hybrid hardware oriented motion estimation algorithm for HEVC/H.265”. J Real-Time Image Process 953–966 https://doi.org/10.1007/s11554-020-01056-w

Thang NV, Dac Tung V, Hoan ND (2017) An optimized hardware design of Integer Motion Estimation HEVC for encoding 8K video. In: Proc. 4th NAFOSTED Conference Info Comp Sci 319–324

Tourapis A (2002) Enhanced predictive zonal search for single and multiple frame motion estimation. Proceedings of visual communications and image processing (VCIP ), 1069–79

Tourapis AM, Au OC, Liou ML (2001) ‘Predictive Motion Vector Field Adaptive Search Technique (PMVFAST). Proc Visual Commun Frame Process

Tseng Y, Shen C (2019) The design and implementation of a highly efficient motion estimation engine for HEVC Systems. In: Proc. IEEE international symposium on circuits and systems (ISCAS), 1–5

Vidyalekshmi VG, Yagain D, Rao G (2014)”Motion estimation block for HEVC encoder on FPGA”. In Recent Advances and Innovations in Engineering (ICRAIE), 1–5

Werda I, Chaouch H, Samet A, Ben Ayed MA, Masmoudi N (2007) Optimal DSP-based motion estimation tools implementation for H.264/AVC Baseline Encoder. IJCSNS Int J Comp Sci Network Sec 7(5)

Ye X, Ding D, Yu L (2014) “A hardware-oriented IME algorithm and its implementation for HEVC,” In Visual Communications and Image Processing Conference, 2014 IEEE, 205–208

Yuan X, Jinsong L, Liwei G, Zhi Z, Teng RKF (2013). A high performance VLSI architecture for integer-motion estimation in HEVC. In IEEE 10th international conference ASIC (ASICON), Shenzhen (1–4)

Zeng R, Li B, Liou ML (1994) A new three-step search algorithm for block motion estimation. IEEE Trans Circuits Syst VideoTechnol 4:438–443

Zhu S, Ma K-K (2000) A new diamond search algorithm for fast block matching motion estimation. IEEE Trans Frame Process 9(2):287–290

Zhu C, Lin X, Chau LP (2022) ‘Hexagon-based search pattern for fast block motion estimation. IEEE Trans Circuits Syst Video Technol 12(5):349–355

Acknowledgements

The authors extend their appreciation to the Deanship of Scientific Research at King Khalid University for funding this work through large group Research Project under grant number RGP2/39/44.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Ethical approval

This work was supported by the Deanship of Scientific Research at King Khalid University (Grant numbers RGP2/39/44). The authors have no relevant financial or non-financial interests to disclose.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Loukil, H., Mayet, A.M. Hardware implementation and validation of the fast variable block size motion estimation architecture for HEVC Standard. Multimed Tools Appl 82, 46331–46349 (2023). https://doi.org/10.1007/s11042-023-15628-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11042-023-15628-y