Abstract

By using a superconducting transition edge sensor (TES) to measure the thermal energy of individual decay events with high energy resolution, decay energy spectrometry provides a unique fingerprint to identify each radionuclide in a sample. The proposed measurement requires optimizing the thermal parameters of the detector for use with 5 MeV scale energy deposited by alpha decay of the sample radionuclides. The thermal performance of deep-etched silicon TES chips is examined with the use of an onboard resistive heater. With known heater power and bath temperature, the thermal conductance, heat capacity, and frame temperature are calculated and compared to theory.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The decay energy spectrometry (DES) project at NIST is intended to provide a direct, absolute, and complete assay of small quantities of radionuclides, with applications in security, environment monitoring, medicine, and electronics [1]. By using a superconducting transition edge sensor (TES) to measure the thermal energy of individual decay events with high energy resolution (resolving power ≥ 1000 at 5 MeV), DES provides a unique fingerprint to identify each radionuclide in a sample. Here, a deep-etched silicon structure is used to form the thermal link between the TES-island sensing element and the TES-frame connected to the thermal bath. Compared to a thin membrane construction, this approach makes the chip easier to fabricate and more robust for handling [2]. The TES characterization is motivated by radiation sensing applications that require high stopping power. For decay energy measurements, we use an approximately 0.5 mm3 gold foil absorber containing embedded radionuclides. This foil is attached to the TES absorber pad, with an indium microsphere that is compressed to achieve thermal contact. The decay times of pulses from Am-241 sources collected with this system were longer than expected, suggesting low electro-thermal feedback, which may be caused by insufficient thermal link between TES-frame and bath. We believe that the high energy of DES pulses (≈ 1 pJ) compared to x-ray applications (< 0.02 pJ) contributes to the challenge. Achieving pulses faster than 50 ms with the higher energy absorbed in each pulse requires a higher thermal conductance from island to frame and a correspondingly higher TES bias power of a few hundred pW. If the thermal link between frame and bath is insufficient, the entire chip will heat up, and pulse height will be reduced in a similar manner as running a well-linked configuration at high bath temperature Tbath.

We use a TES-island heater and a secondary TES located on the TES-frame to measure the thermal resistance from the TES-island to the TES-frame, and from the TES-frame to the bath. We fit a heat flow model to our results, and from this we calculate the TES-frame temperature during device operation and the heat capacity of the TES-island. This characterization method may also be of interest for experiments that use arrays of lower particle energy TESs where the total bias power exceeds 100 pW.

2 Experimental Details

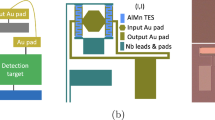

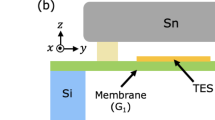

The TES has a Mo-Cu bilayer with Cu normal-metal bars, normal state resistance Rn ≈ 12 mΩ, and transition temperature Tc ≈ 100 mK. The TES is located on an island which is thermally linked to the bath via silicon deep-etched meander structures. The same silicon etch separated the wafer into individual 4.9 mm by 4.9 mm chips. On the TES-island there is an Au-coated Cu pad used for mounting samples, linked thermally to the TES with a trapezoidal shape Cu feature. In the characterization measurements presented below, a “blank” sample, of similar mechanical properties as our DES samples but without radioactive material, is attached. The chip is mounted on an Au-plated Cu surface in a solid Cu enclosure. Small BeCu spring clips placed on the TES-frame provide physical clamping, and gold wire bonds between TES-frame and Cu surface provide thermal connection. The TES-island contains a resistive heater (Cu) with resistance Rheat ≈ 70 mΩ. The TES-frame contains a TES of similar composition to the island TES, Rn ≈ 12 mΩ, and Tc ≈ 100 mK. Two TES chips were installed in a dilution refrigerator with base temperature of \(20\) mK.

As depicted in Fig. 1, TES1 has a higher thermal link conductivity from TES-island to TES-frame (Gif) compared to TES2. Conversely, the frame of TES2 has a higher thermal conductivity link to the bath compared to TES1. Therefore, we expect TES1 to operate at a higher TES-frame temperature Tframe than TES2.

We use a four-wire technique to measure Rheat and confirm it does not change (within 2 mΩ) over the temperature range of this experiment. Subsequently, we apply a constant current measured with a multimeter, and the heater power is calculated by \({P}_{{\text{heat}}}={I}_{{\text{heat}}}^{2}{R}_{{\text{heat}}}\).

A very low bias current (0.2 µA) is applied to either the island TES or frame TES, which is sufficient to measure the difference between the superconducting and normal state using our DC SQUID readout, without substantially affecting Tc by magnetic or self-heating effects [3]. Iheat is then raised until the transition is observed (sudden decrease in TES current). For a given bath temperature, Iheat to initiate the superconducting to normal transition is repeatable to under 0.5%, and the TES acts as a point thermometer indicating TTES = Tc. Because the TES is not generating heat while superconducting, it is assumed to be in equilibrium with the phonon temperature of the underlying silicon. This measurement is carried out at multiple Tbath. The points (Tbath, Pheat) are plotted and fit by a thermal conduction law (Eq. 1), with (n, k, Tc) being the fit parameters for each TES [4].

Tbath is varied from 35 to 92 mK, and Pheat to reach Tc is plotted in Fig. 2, along with the results of fitting Eq. (1) to the data. Next, we apply thermal power conservation Eq. (2) to solve for Tframe when the central TES is at Tc, with subscripts i and f referring to the (n, k, Tc) fits for the island and frame TESs, respectively. The results are shown in Fig. 3.

It is also possible to use the heater to determine C, the heat capacity of the TES-island and attached absorber. In this procedure, the (n, k, Tc) values are found as described above, the entire TES is cooled down to Tbath, then a constant Pheat is applied, and tf—the time required to reach Tc—is recorded. The experimental measurement point is (Pheat, tf) for each trial. The system of equations Eq. (3) to Eq. (8) is solved numerically to obtain a best fit for the electron and lattice heat capacity parameters \(\gamma\) and \(\alpha\) (\(\alpha\) is assumed to be zero in our temperature range). With a correct solution, the equations match the observed tf at various Pheat as illustrated in Fig. 4.

3 Discussion

It is observed that even with a nominally good thermal link (40 Au wire bonds at the TES-frame in addition to two BeCu clamps), Tframe may be significantly above Tbath. This suggests that the thermal conductance from TES-frame to bath needs to be considered when modeling TES response. From the TES-frame, thermal energy exits the chip through electron–phonon coupling to a gold pad on the TES-frame and then through electron-mediated conduction in gold wire bonds to the surrounding metal structure at Tbath (Fig. 5).

For the gold wire bonds, assuming the temperature of a 1 mm long, 25.4 µm diameter wire is 20 mK, gold resistivity at room temperature \({\rho }_{{\text{rt}}}=0.022\) m·µΩ, and residual resistance ratio (RRR) of 10, the Wiedemann–Franz law gives a thermal conductivity of \(1/{R}_{{\text{t}}}=\) 108 nW/K. With the sub-nW powers involved, even a single wire bond should remain within 2 mK of \({T}_{{\text{bath}}}\) (in turn supporting the assumption of a single temperature for the wire). The observed \({G}_{{\text{fb}}}\) from frame to bath at Tframe ≈ 100 mK was 90 nW/K and 200 nW/K for TES1 and TES2 respectively.

For the gold pads on the TES-frame, to which the gold wire bonds are attached, the electron–phonon coupling is given theoretically by Eq. (8), where \({\Sigma }_{{\text{Au}}}\) is the strength of electron–phonon thermal coupling in gold, \({T}_{{\text{f}}}\) is the phonon temperature of the silicon frame, and \({T}_{{\text{epad}}}\) is the electron temperature of the gold pad. For our TES chips, the deposited gold volume is \(V=5.67\times {10}^{5}\) µm3. For a constant power, the deviation of \({T}_{{\text{f}}}\) from \({T}_{{\text{epad}}}\approx {T}_{{\text{bath}}}\) is increased substantially at lower \({T}_{{\text{bath}}}\), due to the \({T}^{5}\) dependence.

We may expect \(T_{{{\text{epad}}}} \approx T_{{{\text{bath}}}}\) due to the high conductivity of the gold wires, and \({T}_{{\text{frame}}}\) has been calculated as illustrated in Fig. 3. Since \(P\) and \(V\) are also known, Eq. (8) is used to estimate \({\Sigma }_{{\text{Au}}}\) in our chips under the assumption that the entire temperature drop \({T}_{{\text{f}}}-{T}_{{\text{bath}}}\) occurs in the electron–phonon coupling. For TES1, \({\Sigma }_{{\text{Au}}}\approx 0.45\) nW·µm−3·K−5. For TES2, \({\Sigma }_{{\text{Au}}}\approx 1.1\) nW·µm−3·K−5. We do not expect large variations in \({\Sigma }_{{\text{Au}}}\) between chips, and the difference between the above two estimates may be attributed to the 40 wire bonds in TES2 contributing to the \(V\) term, increasing it beyond the nominal deposited volume. From the literature we may expect \({\Sigma }_{{\text{Au}}}\approx\) (1.4 to 3.8) nW·µm−3·K−5 [5, 6], which is higher than the estimated values for our chips. Two sources of thermal resistance that may contribute to this difference are conduction through the Si chip frame and acoustic mismatch. With 4 wire bonds in TES1, the thermal energy travels through up to 2.4 mm along the length of each gold pad (0.91 nW/K at 35 mK) and underlying Si (11.6 nW/K at 35 mK), since the gold bonds are in the corners of the frame; this effect is reduced when wire bonds are evenly spaced along the pad. The acoustic mismatch [7] between the Si substrate and Au pad adds another 99 nW/K at 35 mK. Other possible causes for the high frame temperature, such as inadequate thermal links further up the chain towards the dilution refrigerator mixing chamber, are being investigated.

References

R. Fitzgerald, B. Alpert, D. Becker, D. Bergeron, R. Essex, K. Morgan, S. Nour, G. O’Neil, D. Schmidt, G. Shaw, D. Swetz, R. Verkouteren, D. Yan, Toward a new primary standardization of radionuclide massic activity using microcalorimetry and quantitative milligram-scale samples. J. Res. Natl. Inst. Stan. (2021). https://doi.org/10.6028/jres.126.048

A.S. Hoover, E.M. Bond, M.P. Croce, T.G. Holesinger, G.J. Kunde, M.W. Rabin, L.E. Wolfsberg, D.A. Bennett, J.P. Hays-Wehle, D.R. Schmidt, D. Swetz, J.N. Ullom, Measurement of the 240 Pu/239 Pu mass ratio using a transition-edge-sensor microcalorimeter for total decay energy spectroscopy. Anal. Chem. 87(7), 3996–4000 (2015). https://doi.org/10.1021/acs.analchem.5b00195

Y. Nishinomiya, A. Kusaka, K. Kiuchi et al., Development of the characterization methods without electrothermal feedback for TES bolometers for CMB measurements. J. Low Temp. Phys. 209, 1079–1087 (2022). https://doi.org/10.1007/s10909-022-02864-z

M. D’Andrea, C. Macculi, G. Torrioli et al., The demonstration model of the ATHENA X-IFU cryogenic anticoincidence detector. J. Low Temp. Phys. 199, 65–72 (2020). https://doi.org/10.1007/s10909-019-02300-9

B. Calkins, A.E. Lita, A.E. Fox, S.W. Nam, Faster recovery time of a hot-electron transition-edge sensor by use of normal metal heat-sinks. Appl. Phys. Lett. 99(24), 241114 (2011). https://doi.org/10.1063/1.3659686

C.A. Kilbourne, J.S. Adams, R.P. Brekosky, J.A. Chervenak, M.P. Chiao, M.E. Eckart, E. Figueroa-Feliciano, M. Galeazzi, C. Grein, C.A. Jhabvala, D. Kelly, M.A. Leutenegger, F. Dan McCammon, S. Porter, A.E. Szymkowiak, T. Watanabe, J. Zhao, Design, implementation, and performance of the Astro-H SXS calorimeter array and anti-coincidence detector. J. Astron. Telesc. Instrum. Syst. 4(1), 011214 (2018). https://doi.org/10.1117/1.JATIS.4.1.011214

E.T. Swartz, R.O. Pohl, Thermal boundary resistance. Rev. Mod. Phys. 61, 605 (1989). https://doi.org/10.1103/RevModPhys.61.605

Author information

Authors and Affiliations

Contributions

M.C. carried out measurements and wrote the main manuscript text. R.F. and G.O. provided guidance on the experiment and theory. D.S. fabricated the TES chips. All authors reviewed the manuscript.

Corresponding author

Ethics declarations

Conflict of interests

The authors declare no competing interests.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Carlson, M., Fitzgerald, R., Schmidt, D. et al. Characterization of Transition Edge Sensors for Decay Energy Spectrometry. J Low Temp Phys (2024). https://doi.org/10.1007/s10909-024-03135-9

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s10909-024-03135-9