Abstract

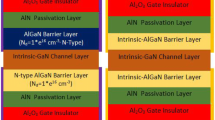

In this article, the impact of dual heterojunction in charge plasma TFET has been investigated in terms of DC, RF and linearity analysis. Using higher bandgap material on the drain side, the gate engineered Ge-GaAs-Al0.3Ga0.7As dual heterojunction charge plasma TFET (GE-DHJ-CPTFET) achieved \(\sim\) 104 times lower ambipolar current than the Ge-GaAs Heterojunction Charge Plasma TFET. In addition, the proposed design achieved excellent DC and RF/analog performance, resulting in an on-state current (Ion) of 2.85 \(\times\) 10−4 A/\(\mu\)m, subthreshold swing (SS) of 16.56 mV/decade, threshold voltage (Vth) of 0.295 V, Ion/Ioff of 3.53 \(\times\) 1013, maximum transconductance (gm) of 8.86 \(\times\)10−4 S/\(\mu\)m, peak cutoff frequency (ft) of 1.43 THz, and a peak gain bandwidth product (GBP) of 0.143 THz. The device linearity is corroborated by sustained performance in third-order transconductance (gm3), second-order voltage interception point (VIP2), third-order voltage interception point (VIP3), 3third-order input intercept point (IIP3) and third-order intermodulation distortion (IMD3). Superior ambipolar current reduction, along with its overall device performance, makes the GE-DHJ-CPTFET a viable alternative for high-frequency RF applications.

Similar content being viewed by others

Data availability

The data that support the findings of this study are not publicly available. However, data will be available from the corresponding author upon reasonable request.

Code availability

Not applicable.

References

S. Bangsaruntip, G.M. Cohen, A. Majumdar, J.W. Sleight, Universality of short-channel effects in undoped-body silicon nanowire mosfets. IEEE Electron Device Lett. 31, 903–905 (2010)

K. Young, Short-channel effect in fully depleted soi mosfets. IEEE Trans. Electron Devices 36, 399–402 (1989). https://doi.org/10.1109/16.19942

V. Narula, A. Saini, M. Agarwal, Correlation of core thickness and core doping with gate & spacer dielectric in rectangular core shell double gate junctionless transistor. IETE J. Res. 2021, 1–12 (2021)

W.Y. Choi, B.G. Park, J.D. Lee, T.J.K. Liu, Tunneling field-effect transistors (tfets) with subthreshold swing (ss) less than 60 mv/dec. IEEE Electron Device Lett. 28, 743–745 (2007). https://doi.org/10.1109/LED.2007.901273

S. Sahay, M.J. Kumar, Junctionless field-effect transistors: design, modeling and simulation (Wiley, Hoboken, 2019)

N. Damrongplasit, C. Shin, S.H. Kim, R.A. Vega, T.J.K. Liu, Study of random dopant fluctuation effects in germanium-source tunnel fets. IEEE Trans. Electron Devices 58, 3541–3548 (2011)

B. Ghosh, M.W. Akram, Junctionless tunnel field effect transistor. IEEE Electron Device Lett. 34, 584–586 (2013)

B. Rajasekharan, R.J. Hueting, C. Salm, T. Van Hemert, R.A. Wolters, J. Schmitz, Fabrication and characterization of the charge-plasma diode. IEEE Electron Device Lett. 31, 528–530 (2010)

M.R. Tripathy, A.K. Singh, A. Samad, S. Chander, K. Baral, P.K. Singh, S. Jit, Device and circuit-level assessment of gasb/si heterojunction vertical tunnel-fet for low-power applications. IEEE Trans. Electron Devices 67, 1285–1292 (2020)

J. Debnath, M.E.H. Sikder, S. Singha, Comparative analysis of gate-oxide engineering in charge plasma based nanowire transistor. Eng. Res. Exp. 5, 035028 (2023)

M.L. Fan, Y.N. Chen, P. Su, C.T. Chuang, Challenges and designs of tfet for digital applications. Tunn. Field Effect Trans. Technol. 2016, 89–109 (2016)

M. F. Jawad, T. Rahman, J. K. Saha, Performance enhancement of ge/gaas heterostructure tunnelling field effect transistor, in: 2020 IEEE 10th International Conference Nanomaterials: Applications & Properties (NAP), IEEE, pp. 01TPNS02–1 (2020)

S. Kumar, B. Raj, Analysis of i on and ambipolar current for dual-material gate-drain overlapped dg-tfet. J. Nanoelectron. Optoelectron. 11, 323–333 (2016)

M. Aslam, D. Sharma, S. Yadav, D. Soni, V. Bajaj, A new design approach for enhancement of dc/rf characteristics with improved ambipolar conduction of charge plasma tfet: proposal, and optimization. Appl. Phys. A 124, 342 (2018)

C. Rajan, D. Sharma, D.P. Samajdar, Implementation of physical unclonable functions using hetero junction based gaa tfet. Superlattices and microstructures 126, 72–82 (2019)

M. Abedini, S.A. Sedigh Ziabari, A. Eskandarian, Representation of heterostructure electrically doped nanoscale tunnel fet with gaussian-doping profile for high-performance low-power applications. Int. Nano Lett. 8, 277–286 (2018)

M. Vadizadeh, Digital performance assessment of the dual-material gate gaas/inas/ge junctionless tfet. IEEE Trans. Electron Devices 68, 1986–1991 (2021)

N. Oliva, J. Backman, L. Capua, M. Cavalieri, M. Luisier, A.M. Ionescu, Wse2/snse2 vdw heterojunction tunnel fet with subthermionic characteristic and mosfet co-integrated on same wse2 flake. npj 2D Mater. Appl. 4, 5 (2020)

C.A. Chang, A. Segmüller, L. Chang, L. Esaki, Ge-gaas superlattices by molecular beam epitaxy. Appl. Phys. Lett. 38, 912–914 (1981)

S.I. Kobayashi, M.L. Cheng, A. Kohlhase, T. Sato, J. Murota, N. Mikoshiba, Selective germanium epitaxial growth on silicon using cvd technology with ultra-pure gases. J. Cryst. Growth 99, 259–262 (1990)

M.L. Touraton, M. Martin, S. David, N. Bernier, N. Rochat, J. Moeyaert, V. Loup, F. Boeuf, C. Jany, D. Dutartre et al., Selective epitaxial growth of algaas/gaas heterostructures on 300 mm si (001) for red optical emission. Thin Solid Films 721, 138541 (2021)

R. Kumar, R. Kumar, D. Panda, B. Tongbram, S. Chakrabarti, in Quantum Dots and Nanostructures: Growth, Characterization, and Modeling XVI. Mbe-Grown Gaas/Algaas Multiple Quantum Wells on ge Substrate, Vol. 10929 (SPIE, 2019), p. 1092905

R.E. Camacho-Aguilera, Y. Cai, J.T. Bessette, L.C. Kimerling, J. Michel, High active carrier concentration in n-type, thin film ge using delta-doping. Opt. Mater. Exp. 2, 1462–1469 (2012)

D. Mao, S. Ke, S. Lai, Y. Ruan, D. Huang, S. Lin, S. Chen, C. Li, J. Wang, W. Huang, Innovative ge-sio2 bonding based on an intermediate ultra-thin silicon layer. J. Mater. Sci.: Mater. Electron. 28, 10262–10269 (2017)

C. Liu, T. Lin, S.-J. Chang, Gaas mos capacitors with photo-cvd sio2 insulator layers. Solid-State Electron. 49, 1077–1080 (2005)

D. Barba, C. Wang, A. Nélis, G. Terwagne, F. Rosei, Blocking germanium diffusion inside silicon dioxide using a co-implanted silicon barrier. J. Appl. Phys. 123, 161540 (2018)

C. Renard, M. Halbwax, D. Cammilleri, F. Fossard, V. Yam, D. Bouchier, Y. Zheng, Ge growth over thin sio2 by uhv-cvd for mosfet applications. Thin Solid Films 517, 401–403 (2008)

N. Gupta, R. Chaujar, Influence of gate metal engineering on small-signal and noise behaviour of silicon nanowire mosfet for low-noise amplifiers. Appl. Phys. A 122, 1–9 (2016)

W. Long, H. Ou, J.-M. Kuo, K.K. Chin, Dual-material gate (dmg) field effect transistor. IEEE Trans. Electron Devices 46, 865–870 (1999)

I. Polishchuk, P. Ranade, T.J. King, C. Hu, Dual work function metal gate cmos technology using metal interdiffusion. IEEE Electron Device Lett. 22, 444–446 (2001)

J. Liu, H. Wen, J. Lu, D.L. Kwong, Dual-work-function metal gates by full silicidation of poly-si with co-ni bi-layers. IEEE Electron Device Lett. 26, 228–230 (2005). https://doi.org/10.1109/LED.2005.844696

I. Silvaco, Atlas user’s manual device simulation software (Santa Clara, CA, 2010)

C. Shen, L.T. Yang, G. Samudra, Y.-C. Yeo, A new robust non-local algorithm for band-to-band tunneling simulation and its application to tunnel-fet. Solid-State Electron. 57, 23–30 (2011)

B. Rajamohanan, D. Mohata, A. Ali, S. Datta, Insight into the output characteristics of iii–v tunneling field effect transistors. Appl. Phys. Lett. 102, 10 (2013)

S. Adachi, Gaas, alas, and al x ga1- x as: Material parameters for use in research and device applications. J. Appl. Phys. 58, R1–R29 (1985)

S. Rewari, V. Nath, S. Haldar, S. Deswal, R. Gupta, Improved analog and ac performance with increased noise immunity using nanotube junctionless field effect transistor (njlfet). Appl. Phys. A 122, 1–10 (2016)

N. Jafar, N. Soin, in AIP Conference Proceedings. The Microwave Noise Behaviour of Dual Material Gate Silicon on Insulator, vol. 1136 (American Institute of Physics, 2009), pp. 820–824

A.K. Gupta, A. Raman, N. Kumar, Design and investigation of a novel charge plasma-based core-shell ring-tfet: analog and linearity analysis. IEEE Trans. Electron Devices 66, 3506–3512 (2019)

S. Hussain, N. Mustakim, J.K. Saha, Linearity performance and distortion analysis of carbon nanotube tunneling fet. J. Electron. Mater. 50, 1496–1505 (2021)

S. Hussain, N. Mustakim, M. Hasan, J.K. Saha, Performance enhancement of charge plasma-based junctionless tfet (jl-tfet) using stimulated n-pocket and heterogeneous gate dielectric. Nanotechnology 32, 335206 (2021)

M. Abedini, S.A. Sedigh Ziabari, A. Eskandarian, Representation of heterostructure electrically doped nanoscale tunnel fet with gaussian-doping profile for high-performance low-power applications. Int. Nano Lett. 8, 277–286 (2018)

M. Sotoodeh, A. Khalid, A. Rezazadeh, Empirical low-field mobility model for iii–v compounds applicable in device simulation codes. J. Appl. Phys. 87, 2890–2900 (2000)

S. Cho, I. Man Kang, T.I. Kamins, B.G. Park, J.S. Harris Jr., Silicon-compatible compound semiconductor tunneling field-effect transistor for high performance and low standby power operation. Appl. Phys. Lett. 99, 243505 (2011)

H. Xie, H. Liu, S. Wang, S. Chen, T. Han, W. Li, Improvement of electrical performance in heterostructure junctionless tfet based on dual material gate. Appl. Sci. 10, 126 (2019)

H. Liu, L.A. Yang, Y. Chen, Z. Jin, Y. Hao, Performance enhancement of the dual-metal gate in0.53ga0.47as dopingless tfet by using a platinum metal strip insertion. Jpn. J. Appl. Phys. 58, 104001 (2019)

M.R.U. Shaikh, S.A. Loan, Drain-engineered tfet with fully suppressed ambipolarity for high-frequency application. IEEE Trans. Electron Devices 66, 1628–1634 (2019)

H. Asai, T. Mori, T. Matsukawa, J. Hattori, K. Endo, K. Fukuda, Steep switching less than 15 mv dec- 1 in silicon-on-insulator tunnel fets by a trimmed-gate structure. Jpn. J. Appl. Phys. 58, 16 (2019)

S. Yadav, R. Madhukar, D. Sharma, M. Aslam, D. Soni, N. Sharma, A new structure of electrically doped tfet for improving electronic characteristics. Appl. Phys. A 124, 1–9 (2018)

D. Soni, D. Sharma, M. Aslam, S. Yadav, A novel approach for the improvement of electrostatic behaviour of physically doped tfet using plasma formation and shortening of gate electrode with hetero-gate dielectric. Appl. Phys. A 124, 1–10 (2018)

K. Nigam, S. Pandey, P. Kondekar, D. Sharma, in: 2016 12th Conference on Ph. D. Research in Microelectronics and Electronics (PRIME). Temperature Sensitivity Analysis of Polarity Controlled Electrically Doped Hetero-tfet, (IEEE, 2016), pp. 1–4

Funding

The authors declare that no funds, grants, or other support were received during the preparation of this manuscript.

Author information

Authors and Affiliations

Contributions

The authors MFJ and JD confirm responsibility for the following: modeling, simulation, formal analysis, and manuscript preparation. TR reviewed the results and proofread the final version of the manuscript. All the work was done under the supervision of JKS.

Corresponding author

Ethics declarations

Conflict of interest

The authors have no relevant financial or non-financial interests to disclose.

Ethical approval

Not applicable

Informed consent

Not applicable.

Consent for publication

Not applicable.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Jawad, M.F., Debnath, J., Rahman, T. et al. RF and linearity analysis of gate engineered dual heterojunction charge plasma TFET with improved ambipolarity. J Mater Sci: Mater Electron 35, 303 (2024). https://doi.org/10.1007/s10854-024-12013-9

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s10854-024-12013-9