Abstract

Complex dielectric (ε* = ε′ − jε″)/electric modulus (M* = M′ + jM″), loss tangent (tanδ), and ac conductivity (σac) properties of Au/(S-DLC)/p-Si structures were investigated by utilizing admittance/impedance measurements between 80 and 440 K at 0.1 and 0.5 MHz. Sulfur-doped diamond-like carbon (S:DLC) was used an interlayer at Au/p-Si interface utilizing electrodeposition method. The capacitance/conductance (C/G) or (ε' ~ C) and (ε″ ~ G) values found to be highly dependent on both frequency and temperature. The increase of them with temperatures was attributed to the thermal-activated electronic charges localized at interface states (Nss) and decrease in bandgap energy of semiconductor. The observed high ε′ and ε″ values at 0.1 MHz is the result of the space/dipole polarization and Nss. Because the charges are at low frequencies, dipoles have sufficient time to rotation yourself in the direction of electric field and Nss can easily follow the ac signal. Arrhenius plot (ln(σac) vs 1/T) shows two distinctive linear parts and activation energy (Ea) value was found as 5.78 and 189.41 from the slope; this plot at 0.5 MHz is corresponding to low temperature (80–230 K) and high temperature (260–440 K), respectively. The observed higher Ea and ε′ (~ 14 even at 100 kHz) show that hopping of electronic charges from traps to others is predominant charge transport mechanism and the prepared Au/(S:DLC)/p-Si structure can be used to store more energy.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Metal–interlayer–semiconductor (MIS)-type Schottky contacts (SCs) are important electronic device for electronic industry as they are used in many applications, such as power electronics [1], solar cells [2], photodiodes [3], capacitors, and transistors [4]. They have more beneficial properties over P/N contacts like low signal-to-noise ratio, high power capacity, high rectification ratio (RR), and high-speed switching elements [5]. However, performance of these contacts are limited by work function and interface properties of metal and semiconductor. Studies on these structures have gained momentum with the observation of natural or artificially formed interlayer at metal/semiconductor interface that leads to an important change in the electric/dielectric properties of metal/interlayer/semiconductor (MIS)-type SCs [6, 7]. In many studies, to change and control the barrier height (BH), the performance of metal–semiconductor (MS) structure is improved usually using an organic or insulator interlayer. In other words, especially high dielectric organic compounds [7], polymers [8], nitride layers [9], metal oxides [10], and diamond-like carbon films [11, 12] have been used as an interlayer to increase the MIS-type SDs and capacitors.

Among these type of materials, diamond-like carbon (DLC) films are an important class of coating materials which have superior properties depending on the proportion of sp2 and sp3 bonds. The deposition method and doping are also the most important parameters that determine the bond structure [13,14,15,16]. These films are mostly deposited by chemical vapor deposition (CVD) and physical vapor deposition (PVD) methods for a wide variety of applications, as high-quality films can be obtained by these methods [13, 17, 18]. Another deposition method is the electrochemical deposition method which is very easy when compared to the others [11]. Relatively lower-quality films are obtained by the electrodeposition for mechanic and tri-biological applications. However, recently, our group have used the electrodeposited DLC films to fabricate MIS-type SDs. Well and encouraging results have been obtained by DC characterization of these devices [11, 12, 19]. So, AC characterization, frequency, and voltage dependence of the fabricated device are also important and require investigation to determine the applicability of the obtained devices. Dielectric materials are widely used in MIS/MOS capacitors and MISFET/MOSFET field-effect transistors because of their charge storage capabilities. Also, they are often used to improve the performance of semiconductor devices. Dielectrics can be easily polarized by an external electric field [20, 21]. Thus, dielectric acquires a net dipole moment. This is known as polarizability.

Today, the basic scientific/technical problems of the MS and MIS-type SCs is relevant to improve the performance of these structures and reduce the cost using new interfacial layer. Dielectric properties and conductivity in MIS-type structures depend on many factors, such as cleaning surface of semiconductor, interfacial layer thickness and its dielectric value, applied voltage, frequency, temperature, series resistance (Rs), surface states (Nss) and their lifetimes (τ). In addition, for the analysis of their electric and dielectric measurements at only one frequency, temperature, voltage, or a narrow, these regimes cannot give more accuracy and reliable information to us on the basic electric/dielectric properties and conduction mechanisms.

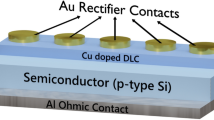

Therefore, in the present work, sulfur-doped DLC (S-DLC) interfacial layer was grown onto p-Si wafer by electrodeposition technique using methanol as carbon source and thiophene as sulfur source. The morphology and chemical composition of the film have been analyzed using scanning electron microscopy (SEM) and X-Ray photoelectron spectroscopy (XPS), respectively. The obtained film on p-Si wafer has been used to perform an Au/(S-DLC)/p-Si device. In addition, dielectric permittivity, ac conductivity, and electric modulus were evaluated using the measured admittance data at two frequencies and over a wide temperature range.

2 Experimental detail

The nanocomposite film was deposited onto p-Si wafer by utilizing two-electrode electrodeposition setup. The electrolyte was prepared by mixing 100-ml methanol and 100-µl thiofuran. Graphite plate and p-Si substrate were used as anode and cathode, respectively. The distance between the electrodes, the applied potential, and duration time were 4 mm, 500 V and 2 h, respectively. More details on the deposition system were given elsewhere [11, 12]. SEM images of the FEI FEG-Quanta 450 model were caught. A SPECS photoelectron spectrometer with a monochromatic-AlKa X-Ray (XR) was utilized to manage the XR photoelectron spectroscopy investigation. To measure the admittance of the Au/S-DLC/p-Si device, HP-4192A LF impedance analyzer was used. In order to perform the C–V–T and G/ω-V-T measurements, the prepared device was placed into VPF-475 cryostat and then they were carried out between 80 and 440 K at 0.1-MHz and 0.5-MHz frequencies.

3 Results and discussion

3.1 SEM analysis

The SEM spectra of the (S-DLC) interlayer is shown in Fig. 1. Figure 1 shows that the Si wafer is fully covered by a continuous, crack-free, and lumpy film. In this study by changing the deposition parameters crack-free film could be obtained.

3.2 XPS analysis

Figures 2a and b show the C 1s and S 2p XPS spectra of the S-DLC nanocomposite film. In Fig. 2a, C 1s spectrum was de-convoluted into three different peaks with different magnitude and binding energy which was attributed to C–S, C–C, and C–OOH, respectively [22]. Figure 2b shows that the S 2p spectrum appeared around 167.8 eV binding energy that was assigned to sulfide compounds (like C–S–C and H2S) [12]. As can be clearly seen from the XPS spectra, the S has been thoroughly doped into the DLC film.

3.3 Admittance measurements

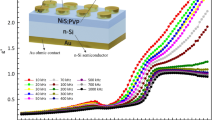

Admittance measurements of the fabricated Au/(S-doped DLC)/p-Si (MIS) are based on the voltage-dependent capacitance/conductance–voltage–temperature (C–V–T, G/ω–V–T) measurements of device for 01 and 0.5 MHz in a wide range of temperature (80–440 K) to obtain a detail information on the basic electric, dielectric, and conduction mechanism. Therefore, both the C–V and G/ω–V measurements type device/structure were carried out at between − 4 V and + 8 V as shown in Fig. 3a and b and Fig. 4a and b, respectively. As seen in these figures, as the temperature increases, the C value for all the frequencies increases. When the temperature changes, it causes changes in dielectric properties. Since capacitance is directly proportional to dielectric constant, the capacitance changes with temperature. The observed increase both in the C and G/ω with increasing temperature is the result of the excitation of many electronic charges from valence band or traps to the conductance band under temperature and external electric field effects [23,24,25,26]. It is well known that at absolute temperature and very low temperatures, almost all electrons are considered frozen and so they have not enough thermal energy to move from the valence band to conductance band or over the barrier height. However, very little conduction can only be achieved through traps located between the metal and the semiconductor and in the forbidden energy gap. When the temperature increases, many electrons gain sufficient thermal energy to over to barrier height. As a result, the conduction will increase with the temperature and bias voltage.

As shown in Fig. 3a and b and Fig. 4a and b, both the value of the C and G/ω decreased as the frequency increased. This frequency dependence of C and G results from the frequency response of the interface states or traps (Nss) depend on their lifetimes or relaxation times (τ) [20, 25,26,27,28]. At low frequencies, the period (T = 1/2πf) is higher than the τ of the Nss. In this situation, they can easy follow the ac signal. Therefore, the C value is high at low frequencies. At higher frequencies, the opposite of this situation occurs. On the other hand, while Nss may be dominated in inversion/depletion regimes at moderate frequencies, Rs of the device is particularly dominant only at the accumulation regime (G = 1/Rs) at enough high frequencies. Thus, the real value of Rs can be calculated from the strong accumulation zone using Nicollian–Brews method (Rs = G/(G2 + (ωC)2)) [20]. Figure 4a and b shows the (G/ω − V) curves as a function of voltage at different temperatures and for frequencies of 0.1 MHz and 0.5 MHz, respectively. As seen in these figures, the conductance increases with an increase in temperature due to the thermally activated conduction process. Because, more and more thermally generated electronic charges increase with increasing temperature. In addition, conductance with frequency exhibits similar behavior with capacitance.

Additionally, the temperature sensitivity (S = dV/dT) of the structure was analyzed using voltage–temperature (V–T)-dependent capacitance values. Figure 5a and b shows the variation of voltage with temperature (between 290 and 440 K) at different constant capacitance values for 100 kHz and 500 kHz, respectively. From Fig. 5a, the S values were found to be about -26 mV/K and – 28 mV/K for 6 nF and 7 nF, respectively. From Fig. 5b, the S values were found to be about – 21 mV/K and – 24 mV/K for 3 nF and 4 nF, respectively. The sensitivity value increases with increase in constant capacitance value. The obtained result is in agreement with similar studies in the literature [29,30,31]. It is clear that the structure demonstrates very high temperature sensitivity.

3.4 Dielectric properties

Using the dielectric spectroscopy method, the basic dielectric parameters and conductivity properties of a dielectric material can be measured depending on frequency, temperature, and applied bias voltage or electric field. The dielectric processes are usually depending on interlayer, its thickness and homogeneity, Nss and their τ, frequency, temperature, and applied external electric field [32]. The interlayer material can be easily polarized because of the electrons at surface states and dipoles may be easily restructured by reordering under electric field and temperature, especially at lower frequencies, but at higher frequencies, the dielectric value decreases due to shorter time available for the dipoles to align [33]. The observed decrease in ε′ and ε" at high frequency is the result of a decrease in the polarization and also Nss [6, 20]. In other words, the contribution of polarization and Nss at lower frequency is quite higher than high frequencies [34,35,36].

A dielectric material has very low conductivity at dc voltage. The complex dielectric (ε*) including the real (ε′) and imaginary (ε") parts is given as follows [37, 38]:

where Co is the capacitance of the empty capacitor and is given as follows [38]:

In Eqs. 1 and 2, the Cm and Gm are the measured C and G values, A is the Schottky contact area, and d is the interlayer thickness. While ε′ is the measure of the energy stored in the polarized dielectric material, ε" is the loss energy. The magnitude of ε′ and ε" is determined from Eq. 2. In addition, the dielectric loss tangent (tanδ) which is called as dissipation factor is defined as follows:

The temperature-dependent changes in ε′, ε″, and tanδ values are given in Fig. 6a–c, respectively. As shown in these figures, while their values increase with increasing temperature, they decrease with increasing frequency. Since the temperature becomes increased, dipole orientations become easy and hence orientation polarization increases. This behavior causes an increase in dielectric constant [25, 39,40,41,42,43,44,45]. Besides, the observed increase in ε′ value results from the contribution of the electronic charges to the polarization. In addition, the dielectric loss increases as the mobility of electronic charges increases with increase in temperature. As the frequency increases, ε′ and ε″ value decrease due to polarization effects [46,47,48,49]. Especially, at low frequencies, space charge polarization or interfacial polarization is effective and hence, the magnitude of ε′ becomes high at low frequency.

3.5 Electric modulus

Complex electric modulus (M* = M′ + jM″) is given as follows [41, 50,51,52,53]:

Figure 7a and b indicates a plot of M′ and M″ as a function of temperature for two frequencies. As seen in these figures, while M′ value decreases with increasing temperature, M″ value increases. Both M′ and M″ values have an almost constant value below room temperature.

3.6 Electrical ac Conductivity

The AC electrical conductivity (σac) is given as follows:

Figure 8 indicates the ac conductivity with temperature for two frequencies. As seen in this figure, the ac conductivity has an almost constant value below room temperature. Above room temperature, the ac conductivity increases rapidly by increasing temperature. Moreover, the value of σac increases with the increasing frequency. The increase of σac with temperature is due to the increase in thermally generated carriers [41, 53,54,55,56]. In other words, the increase of σac results from the increasing drift mobility of electronic charges through hopping conduction.

As shown in Fig. 8, the value σac increases with temperature and it was considerably high at enough high temperatures, but at low temperatures, it remains almost independent of temperature for both frequencies. Such behavior of it at high temperature is typical of semiconductor behavior. The conductivity is treated as temperature-activated hopping from center to center. There are many reports on the ac conductivity in the literature, to evaluate of activation energy (Ea) from the Arrhenius plot [41,42,43]:

In addition, the value of activation energy (Ea) of conductivity was estimated using the Arrhenius equation. Arrhenius equation is defined as follows [43, 57,58,59,60,61]:

where σo is an exponential factor and kB is the Boltzmann’s constant. As shown in Fig. 9, the σac vs T−1 plot has good straight line and the slope of this plot gives to us a direct Ea. It is clearly that the σac vs T−1 plot has two distinctive linear part which are called as Region-1 (80–230 K, and Region-2 (260–440 K), respectively. Such behavior of it can be explained in terms of the hopping of electrons between interface traps. The calculated Ea and σ0 values are given in Table 1. Both Ea and σ0 values increase with increase in temperature. Also, while these values decrease with increasing frequency at lower temperatures and then increase at high temperatures.

All these results are indicated that the C, G/ω, and σac values are very sensitive to temperature especially at and above room temperatures due to activated many electrons under temperature effect. This change in their values from voltage region to other or traps to traps is the result of thermal re-order/structure of the electronic charges under temperature and electric field effects.

4 Conclusion

In this study, (S:DLC) interfacial layer was sandwiched between metal (Au) and semiconductor (p-Si) using electrodeposition method using methanol as carbon source and thiophene as sulfur source. Firstly, the morphology and chemical composition of the film were analyzed by SEM and XPS spectroscopy method. Secondly, the “Admittance or conduction technique” which is including a set of frequency or temperature-dependent C and G/ω measurements of performed Au/S-DLC/p-Si device both at 100 kHz and 500 kHz in the frequency range of 80–440 K and voltage range of (− 4 V)−8 V. After that the real (ε′) and imaginary (ε") components of the complex dielectric (ε*) and (M′) and (M″) of the complex electric modulus (M*), tanδ, and ac conductivity (σac) values were calculated from these C and G data. The values of ε′, ε", and σac were usually increased with increasing temperature, but this change becomes more prominent especially at above room temperature. As the dielectric parameters decrease with increasing frequency, the ac conductivity increases. The Ea value of the Au/S-DLC/p-Si device was obtained from the slope of the straight line of the Arrhenius plot (ln(σac − 1000/T) for 100 kHz and 500 kHz. The observed two linear parts of Arrhenius plot show that there is two different conduction mechanisms at low and high temperatures, respectively. The observed higher values of Ea and ε′ (~ 14) even at 100 kHz indicated that hopping of electrons between traps is effective charge transport mechanism and so the prepared Au/(S:DLC)/p-Si/Au structure can be used to store more energy and temperature sensor.

Data availability

The datasets analyzed during the current study are available from the corresponding author on reasonable request.

References

M. Benlamri, B.D. Wiltshire, Y. Zhang, N. Mahdi, K. Shankar, D.W. Barlage, A.C.S. Appl, Electron. Mater. 1, 13–17 (2019)

S. Yavuz, C. Kuru, D. Choi, A. Kargar, S. Jin, P.R. Bandaru, Nanoscale 8, 6473–6478 (2016)

A.B. Yadav, A. Pandey, D. Somvanshi, S. Jit, IEEE Trans. Electron Devices 62, 1879–1884 (2015)

N.A. Al-Ahmadi, Mater. Res. Express 7, 032001 (2020)

I. Missoum, Y.S. Ocak, M. Benhaliliba, C.E. Benouis, A. Chaker, Synth. Met. 214, 76–81 (2016)

R. Marnadu, J. Chandrasekaran, M. Raja, M. Balaji, V. Balasubramani, J. Mater. Sci. Mater. Electron. 29, 2618–2627 (2018)

Ö. Güllü, Ş Aydoǧan, A. Türüt, Microelectron. Eng. 85, 1647–1651 (2008)

N. Basman, R. Uzun, I. Erol, G. Cankaya, O. Uzun, J. Microelectron. Electron. Components Mater. 46, 190–196 (2016)

M. Ambrico, M. Losurdo, P. Capezzuto, G. Bruno, T. Ligonzo, L. Schiavulli, I. Farella, V. Augelli, Solid State Electron. 49, 413–419 (2005)

S.O. Tan, H.U. Tecimer, O. Çiçek, H. Tecimer, I. Orak, Ş Altındal, J. Mater. Sci. 27, 8340–8347 (2016)

N. Basman, N. Aslan, O. Uzun, G. Cankaya, U. Kolemen, Microelectron. Eng. 140, 18–22 (2015)

N. Basman, S.F. Varol, J. Electron. Mater. 48, 7874–7881 (2019)

M. Jelinek, T. Kocourek, J. Zemek, J. Mikšovský, Š Kubinová, J. Remsa, J. Kopeček, K. Jurek, Mater. Sci. Eng. C 46, 381–386 (2015)

M.I. Khan, I. Rasheed, M.A. Naeem, S. Majeed, G.M. Mustafa, M. Fatima, A. Mahmood, W. Al-Masry, M. Iqbal, N.A. Kattan, A. Nazir, J. Mater. Res. Technol. 9, 8289–8295 (2020)

N. Ohtake, M. Hiratsuka, K. Kanda, H. Akasaka, M. Tsujioka, K. Hirakuri, A. Hirata, T. Ohana, H. Inaba, M. Kano, H. Saitoh, Materials (Basel) 14, 315 (2021)

R. Dey, S. Dolai, S. Hussain, R. Bhar, A.K. Pal, Diam. Relat. Mater. 82, 70–78 (2018)

B. Paramanik, D. Das, Appl. Surf. Sci. 579, 152132 (2022)

S. Saha, D. Das, Appl. Surf. Sci. 596, 153638 (2022)

N. Basman, R. Uzun, E. Gocer, E. Bacaksiz, U. Kolemen, Microsyst. Technol. 24, 2287–2294 (2018)

E.H. Nicollian, J.R. Brews, MOS Physics and Technology (Wiley, New York, 1982)

H. Bentarzi, Transport in Metal-Oxide-Semiconductor Structures (Springer, Berlin, 2011)

S. Wan, L. Wang, Q. Xue, Electrochem. Commun. 12, 61–65 (2010)

Y. Azizian-Kalandaragh, Y. Badali, M.A. Jamshidi-Ghozlu, F. Hanife, S. Ozçelik, Ş Altındal, G. Pirgholi-Givi, Physica B 650, 414495 (2023)

A. Buyukbas-Uluşan, S.A. Yerişkin, A. Tataroğlu, M. Balbaşı, Y.A. Kalandaragh, J. Mater. Sci. 29, 8234–8243 (2018)

S.M. Sze, Physics of Semiconductor Devices, 2nd edn. (Wiley, New York, 1981)

L. Kungumadevi, R. Sathyamoorthy, A. Subbarayan, Solid-State Electron. 54, 58–62 (2010)

F.Z. Acar, R.E. Uyar, A. Tataroglu, ECS J. Solid State Sci. Technol. 12, 033009 (2023)

Ph.N. Meitei, N.K. Singh, J. Alloys Compd. 941, 168900 (2023)

O. Çiçek, E. Arslan, S. Altındal, Y. Badali, E. Özbay, IEEE Sens. J. 22, 23699–23704 (2022)

O. Çiçek, S. Altındal, Y. Azizian-Kalandaragh, IEEE Sens. J. 20, 14081–14089 (2020)

X. Li, T. Pu, X. Li, L. Li, J.-P. Ao, IEEE Trans. Electron Dev. 67, 1171–1175 (2020)

P.S. Ho, E.S. Yang, H.L. Evans, X. Wu, Phys. Rev. Lett. 56, 177–180 (1986)

H.N. Chandrakala, B. Ramaraj, Shivakumaraiah, G.M. Madhu, Siddaramaiah, J. Mater. Sci. 47, 8076–8084 (2012).

M. Popescu, I. Bunget, Physics of Solid Dielectrics (Elsevier, Amsterdam, 1984)

A. Chelkowski, Dielectric Physics (Elsevier, Amsterdam, 1980)

A.A. Sattar, S.A. Rahman, Phys. Status Solidi (a) 200, 415–422 (2003)

G.G. Raju, Dielectrics in Electric Fields, 2nd edn. (CRC Press, Boca Raton, 2017)

K.C. Kao, Dielectric Phenomena in Solids (Elsevier, London, 2004)

A. Barkhordari, H. Mashayekhi, P. Amiri, Ş Altındal, Y. Azizian-Kalandaragh, Appl. Phys. A 129, 249 (2023)

A. Kumar, A. Kumar, K.K. Sharma, Int. J. Eng. Trans. A 35, 698–705 (2022)

F. Ahmad, A. Maqsood, Physica E 143, 115353 (2022)

A.S. Samsudin, M.I.N. Isa, J. Korean Phys. Soc. 65, 1441–1447 (2014)

E.G. El-Metwally, N.A. Hegab, M. Mostfa, J. Mater. Sci. 33, 12384–12396 (2022)

B. Gowtham, V. Balasubramani, S. Ramanathan, M. Ubaidullah, S.F. Shaikh, G. Sreedevi, J. Alloys Compd. 888, 161490 (2021)

L. Mohan, A.V. Avani, P. Kathirvel, R. Marnadu, R. Packiaraj, J.R. Joshua, N. Nallamuthu, M. Shkir, S. Saravanakumar, J. Alloys Compd. 882, 160670 (2021)

K. Rajasekar, A. Subbarayan, R. Sathyamoorthy, Sol. Energy Mater. Sol. Cells 90, 2515–2522 (2006)

S. Alptekin, A. Tataroğlu, Ş Altındal, J. Mater. Sci. 30, 6853–6859 (2019)

H.G. Cetinkaya, A.F. Vahid, N. Basman, S. Demirezen, Y.S. Asar, S. Altındal, J. Mater. Sci. 34, 822 (2023)

S. Türkay, A. Tataroğlu, J. Mater. Sci. 32, 11418–11425 (2021)

M.M. Ali, S.A. Abdelsalam, O.M. Hemeda, T. Sharshar, A.M.A. Henaish, Opt. Quantum Electron. 55, 95 (2023)

S. Demirezen, S.A. Yeriskin, J. Mater. Sci. 32, 25339–25349 (2021)

D.E. Yıldız, A. Tataroglu, J. Mater. Sci. 34, 1057 (2023)

N.K. Wally, E. Sheha, B.M. Kamal, A.M. Ali, A.M. Ali, M.M. El-Desoky, J. Non-Cryst, Solids 598, 121941 (2022)

M. Jebli, Ch. Rayssi, J. Dhahri, M.B. Henda, H. Belmabrouk, A. Bajahzar, RSC Adv. 11, 23664–23678 (2021)

N. Baraz, İ Yücedağ, Y. Azizian-Kalandaragh, Ş Altındal, J. Mater. Sci. 29, 12735–12743 (2018)

A.B. Hassen, F.I.H. Rhouma, M. Daoudi, J. Dhahri, M. Zaidi, N. Abdelmoula, RSC Adv. 9, 19285–19296 (2019)

N. Kumar, S. Chand, J. Alloys Compd. 817, 153294 (2020)

S.S. Fouad, B. Parditka, H.E. Atyia, E. Baradacs, A.E. Bekheet, Z. Erdelyi, Chin. J. Phys. 77, 73–80 (2022)

A. Hassan, A. Ashery, G. Khabiri, Physica B 618, 413204 (2021)

S. Samanta, B. Paramanik, D. Das, Ceram. Int. 48, 31370–31380 (2022)

Z.A. Alrowaili, A. Qasem, E.R. Shaaban, M. Ezzeldien, Physica B 612, 412975 (2021)

Funding

Open access funding provided by the Scientific and Technological Research Council of Türkiye (TÜBİTAK). The authors declare that no funds, grants, or other support were received during the preparation of this manuscript.

Author information

Authors and Affiliations

Contributions

The manuscript was written with the contributions of all authors. All authors have approved the final version of the manuscript. AT contributed to investigation, data curing, and writing, reviewing, and editing of the manuscript. HD contributed to investigation, measurements, and reviewing and editing of the manuscript. AFV contributed to sample preparation, measurements, and reviewing and editing of the manuscript. BA contributed to sample preparation, measurements, review and editing of the manuscript, and supervision. SA contributed to investigation, writing, reviewing, and editing of the manuscript, and supervision.

Corresponding author

Ethics declarations

Conflict of interest

There are no conflicts to declare.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Tataroglu, A., Durmuş, H., Vahid, A.F. et al. High-temperature sensitivity complex dielectric/electric modulus, loss tangent, and AC conductivity in Au/(S:DLC)/p-Si (MIS) structures. J Mater Sci: Mater Electron 35, 227 (2024). https://doi.org/10.1007/s10854-024-12007-7

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s10854-024-12007-7