Abstract

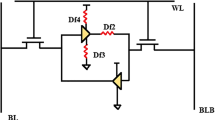

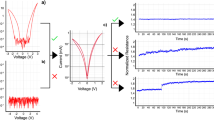

This paper presents a method for operational testing of a memristor-based look-up table (LUT) memory block. In the proposed method the deterioration of the memristors (as storage elements of a LUT), is modeled based on the reduction of the resistance range, a phenomenon well known as reported in the technical literature. A quiescent current technique is used to diagnose the memristors when deterioration results in a change of state, thus leading to a fault. In addition to testing, the proposed method can be utilized also for continuous monitoring of the memristor deterioration in the LUT. The deterioration of the memristors is modeled using a simple yet accurate equivalent circuit. The proposed method is simulated using LTSPICE and extensive simulation results are presented for operational deterioration with respect to different features such as LUT dimension, range of memristance and MOSFET feature size. These results show that the proposed test method is highly efficient for testing and monitoring a LUT in the presence of deteriorating multiple memristors.

Similar content being viewed by others

References

“Xilinx SpartanTM-3AN FPGAs.” http://www.xilinx.com

“Xilinx Spartan Data sheet”, http://www.xilinx.com

Almurib HAF, Kumar TN, Lombardi F (2014) A memristor-based LUT for FPGAs. In Proc. of 9th IEEE International Conference on Nano/Micro Engineered and Molecular System IEEE-NEMS, pp 448–453

Almurib HAF, Kumar TN, Lombardi F (2014) Scalable application-dependent diagnosis of interconnects of SRAM-based FPGAs. IEEE Trans Comput 63(6):1540–1550

Biolek Z, Biolek D, Biolova V (2009) SPICE model of memristor with nonlinear Dopant drift. Radioengineering 18(2):210–214

Chua LO (1971) Memristor - the missing circuit element. IEEE Trans Circuit Theory ct-18(5):507–519

Feng W, Lombardi F, Almurib HAF, Kumar TN (2013) Testing a nano crossbar for multiple fault detection. IEEE Trans Nanotechnol 12(4):477–485

Haron NZ, Hamdioui S (2011) On defect oriented testing for hybrid CMOS/memristor memory. In the Proc. of ATS, pp 353–358

Kumar TN, Almurib HAF, Lombardi F (2014) A novel design of a memristor-based Look-Up Table (LUT) for FPGA. IEEE Asia Pacific Conference on Circuits & Systems

Kumar TN, Almurib HAF, Lombardi F (2015) Operational fault detection and monitoring of a memristor-based LUT. Proc. Design Automation and Test in Europe (DATE), Grenoble, March, pp. 429–434

Nickel J (2011) Memristor materials engineering: from flash replacement towards a universal memory. Proceedings of the IEEE IEDM Advanced Memory Technology Workshop, December

Predictive Technology Model (PTM) website, http://ptm.asu.edu/

Sun F, Zhang T (2007) Defect and transient fault-tolerant system design for hybrid CMOS/Nanodevice digital memories. IEEE Trans Nanotechnol 6(3)

Tang X, Pun KP (2009) High-performance CMOS current comparator. Electron Lett 45(20):1007–1009

Xu C, Dong X, Jouppi NP, Xie Y (2011) “Design implications of memristor-based RRAM cross-point structures” in the Proc of Design, Automation and Test in Europe, pp. 1–6

Yang JJ, Pickett MD, Li X, Ohlberg DAA, Stewart DR, Williams RS (2008) Memristive switching mechanism for metal/oxide/metal nanodevices. Nat Nanotechnol 3:429–433

Yang JJ, Zhang M-X, Strachan JP, Miao F, Pickett MD et al (2010) High switching endurance in TaOx memristive devices. Appl Phys Lett 97

Zhao L, Walker DMH, Lombardi F (1998) Iddq testing of bridging faults in reconfigurable FPGAs. IEEE Trans Comput C47(10):1136–1152

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: S. Hamdioui

This manuscript is an extended version of [10] by the same authors

Rights and permissions

About this article

Cite this article

Kumar, T.N., Almurib, H.A.F. & Lombardi, F. Current-Based Testing, Modeling and Monitoring for Operational Deterioration of a Memristor-Based LUT. J Electron Test 32, 587–599 (2016). https://doi.org/10.1007/s10836-016-5611-3

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-016-5611-3