Abstract

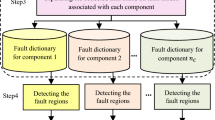

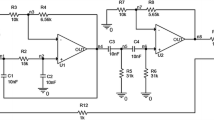

A new method to select an optimum test point set in analog fault diagnosis is proposed in this paper. As the probability density of the circuit output approximately satisfies the normal distribution, an accurate way for determining the fault ambiguity gap is used to calculate the isolation probability of the faults. The proposed fault-pair isolation table derived from the mean and standard deviation values of node voltage can exactly represent the fault-pair isolation capability of the test points. The special test points that can uniquely isolate some particular fault pairs are selected first. This step can help to save the total cost of the computation time and even find the final solution directly. After removing the isolated fault pairs (rows) and the selected test points (columns), the size of the fault-pair isolation table could reduce dramatically. If more optimum test points are needed, the normalized fault-pair isolation probability values in the table are used to select the right test point that has the largest fault-pair isolation capability among all the candidate test points. Analog circuits’ examples and the statistical experiments are given to demonstrate the feasibility and effectiveness of the proposed algorithm. The other reported algorithms are also used to do the comparison. The results indicate that the proposed algorithm has excellent performance in minimizing the size of the test point set. Therefore, it is a good solution and applicable to actual circuits and engineering practice.

Similar content being viewed by others

References

Bandler JW, Salama AE (1981) Fault diagnosis of analog circuits. Proc IEEE 73:1279–1325

Bandler JW, Salama AE (1985) Fault diagnosis of analog circuits. Proc IEEE 73(8):1279–1325

Devarakond SK, Sen S, Bhattacharya S, Chatterjee A (2012) Concurrent device/specification cause-effect monitoring for yield diagnosis using alternate diagnostic signatures. IEEE Des Test Comput 29(1):48–58

Duhamal P, Rault JC (1979) Automatic tests generation techniques for analog circuits and systems: A review. IEEE Trans Circ Syst I CAS-26:411–440

Golonek T, Rutkowski J (2007) Genetic-algorithm-based method for optimal analog test points selection. IEEE Trans Circ Syst II Exp Brief 54(2):117–121

Halder A, Chatterjee A (2005) Test generation for specification test of analog circuits using efficient test response observation methods. Microelectron J 36(9):820–832

Hochwald W, Bastian JD (1979) A dc approach for analog fault dictionary determination. IEEE Trans Circ Syst CAS-26:523–529

Huang K, Stratigopoulos H-G, Mir S, Hora C, Xing Y, Kruseman B (2012) Diagnosis of local spot defects in analog circuits. IEEE Trans Instrum Meas (TIM) 61(10):2701–2712

Huang K, Stratigopoulos H-G, Mir S (2010) Fault Diagnosis of Analog Circuits Based on Machine Learning, in Proc. of Design, Automation and Test in Europe conference (DATE), pp. 1761–1766

Lin PM, Elcherif YS (1985) Analogue circuits fault dictionary—new approaches and implementation. Int J Circ Theory Appl 13(2):149–172

Luo H, Wang Y, Lin H, Jiang Y (2012) A new optimal test node selection method for analog circuit. J Electron Test 28(3):279–290

Milor L, Visvanathan V (1989) Detection of catastrophic faults in analog integrated circuits. IEEE Trans Comput-Aided Des Integr Circ Syst 8(2):114–130

Pinjala KK, Bruce CK (2003) An approach for selection of test points for analog fault diagnosis. Proceedings of the 18th IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems, 287–294

Prasad VC, Babu NSC (2000) Selection of test nodes for analog fault diagnosis in dictionary approach. IEEE Trans Instrum Meas 49(6):1289–1297

Skowron A, Stepaniuk J (1991) Toward an approximation theory of discrete problems: Part I. Fundam Informaticae 15(2):187–208

Spaandonk J, Kevenaar T (1996) Iterative test point selection for analog circuits. In Proc. of the 14th VLSI Test Symp, Princeton, NJ, USA, 66–71

Starzyk JA, Liu D, Liu Z-H, Nelson DE, Rutkowski JO (2004) Entropy-based optimum test nodes selection for analog fault dictionary techniques. IEEE Trans Instrum Meas 53:754–761

Stenbakken GN, Souders TM (1987) Test point selection and testability measure via QR factorization of linear models. IEEE Trans Instrum Meas IM-36(6):406–410

Stratigopoulos H-GD, Makris Y (2005) Nonlinear decision boundaries for testing analog circuits, computer-aided design of integrated circuits and systems. IEEE Trans 24(11):1760–1773

Varaprasad KSVL, Patnaik LM, Jamadagni HS, Agrawal VK (2007) A new ATPG technique (ExpoTan) for testing analog circuits. IEEE Trans Comput-Aided Des Integr Circ Syst 26(1):189–196

Varghese X, Williams JH, Towill DR (1978) Computer aided feature selection for enhanced analogue system fault location. Patterns Recog 10(4):265–280

Yang CL, Tian SL, Long B, Chen F (2010) A novel test point selection method for analog fault dictionary techniques. J Electron Test 26(5):523–534

Yang CL, Tian SL, Long B (2009) Application of heuristic graph search to test point selection for analog fault dictionary techniques. IEEE Trans Instrum Meas 58(7):2145–2158

Yang CL, Tian SL, Long B (2009) Test points selection for analog fault dictionary techniques. J Electron Test 25(2–3):157–168

Zhang C-j, He G, Liang S-h (2008) Test point selection of analog circuits based on fuzzy theory and ant colony algorithm, Proceedings of IEEE AUTOTESTCON 2008: Systems Readiness Technology Conference, Salt Lake City, USA, 2008, pp.164–168

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: K. Chakrabarty

Rights and permissions

About this article

Cite this article

Zhao, D., He, Y. A New Test Point Selection Method for Analog Circuit. J Electron Test 31, 53–66 (2015). https://doi.org/10.1007/s10836-015-5506-8

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-015-5506-8