Abstract

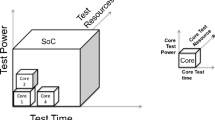

High temperature has become a major problem for system-on-chip testing. In order to reduce the test application time while keeping the temperatures of the cores under test within safe ranges, a thermal-aware test scheduling technique is required. This paper presents an approach to minimize the test application time and, at the same time, prevent the temperatures of cores under test going beyond given limits. We employ test set partitioning to divide test sets into shorter test sequences, and add cooling periods between test sequences so that overheating can be avoided. Moreover, test sequences from different test sets are interleaved, such that the cooling periods and the bandwidth of the test bus can be utilized for test data transportation, and hence the test application time can be reduced. The test scheduling problem is formulated as a combinatorial optimization problem, and we use the constraint logic programming (CLP) to build the optimization model and find the optimal solution. As the optimization time of the CLP-based approach increases exponentially with the problem size, we also propose a heuristic which generates longer test schedules but requires substantially shorter optimization time. Experimental results have shown the efficiency of the proposed approach.

Similar content being viewed by others

Notes

We assume that the CUT is at the ambient temperature when the first test sequence starts. We also assume that the first test sequence is partitioned such that it can be continuously applied until the core temperature reaches the temperature limit.

References

Aerts J, Marinissen EJ (1998) Scan chain design for test time reduction in core-based ICs. Proceedings of the International Test Conference, pp 448–457

Baker BS, Coffman EG Jr, Rivest RL (1980) Orthogonal packings in two dimensions. SIAM J Comput 9(4) 846–855 (Nov)

Borkar S (1999) Design challenges of technology scaling. IEEE Micro 19(4) 23–29 (Jul)

Chakrabarty K (2000) Design of system-on-a-chip test access architectures under place-and-route and power constraints. Proceedings of the IEEE/ACM Design Automation Conference, pp 432–437

Chou R, Saluja K, Agrawal V (1997) Scheduling tests for VLSI systems under power constraints. IEEE Transactions on Very Large Scale Integration (VLSI) Systems 5(2):175–184 (Jun)

Dincbas, M, Van Hentenryck P, Simonis H, Aggoun A, Graf T,Berthier F (1988) The constraint logic programming language CHIP. Proceedings of the International Conference on Fifth Generation Computer Systems, pp 693–702

Flynn D (1997) AMBA: enabling reusable on-chip designs. IEEE Micro 17(4):20–27 (Jul/Aug)

Goel SK, Marinissen EJ (2003) Control-aware test architecture design for modular SoC testing. Proceedings of the IEEE European Test Workshop, pp 57–62

Gunther SH, Binns F, Carmean DM, Hall JC (2001) Managing the impact of increasing microprocessor power consumption. Intel Technol J 5(1): 1–9 Feb. [online]. Available: ftp://download.intel.com/technology/itj/q12001/pdf/art_4.pdf

He Z, Peng Z, Eles P (2006) Power constrained and defect-probability driven SoC test scheduling with test set partitioning. Proceedings of the IEEE Design, Automation and Test in Europe, pp 291–296

Huang Y, Cheng W-T, Tsai C-C, Mukherjee N, Samman O, Zaidan Y, Reddy SM (2001) Resource allocation and test scheduling for concurrent test of core-based SoC design. Proceedings of the IEEE Asian Test Symposium, pp 265–270

Huang W, Stan MR, Skadron K, Sankaranarayanan K, Ghosh S, Velusamy S (2004) Compact thermal modeling for temperature-aware design. Proceedings of the ACM/IEEE Design Automation Conference, pp 878–883

Huang W, Ghosh S, Sankaranarayanan K, Skadron K, Stan MR (2006) HotSpot: a compact thermal modeling methodology for early-state VLSI design. IEEE Transactions Very Large Scale Integration (VLSI) Systems 14(5):501–513 (May)

Iyengar V, Chakrabarty K (2002) “System-on-a-chip test with precedence relationships, preemption and power constraints. IEEE Trans Comput-Aided Des Integr Circuits Syst 21(9):1088–1094 (Sep)

Iyengar V, Chakrabarty K, Marinissen EJ (2001) Test wrapper and test access mechanism co-optimization for system-on-chip. Proceedings of the International Test Conference, pp 1023–1032

Iyengar V, Chakrabarty K, Marinissen EJ (2003) Test access mechanism optimization, test scheduling, and test data volume reduction for system-on-chip. IEEE Trans Comput 52(12):1619–1632 (Dec)

Jaffar J, Lassez J-L (1987) Constraint logic programming. Proceedings of the ACM SIGACT-SIGPLAN Symposium on Principles of Programming Languages, pp 111–119

Larsson E, Peng Z (2002) An integrated framework for the design and optimization of SoC test solutions. J Electron Test Theor Appl 18(4/5):385–400 (Aug)

Lesh N, Marks J, McMahon A, Mitzenmacher M (2004) Exhaustive approaches to 2D rectangular perfect packings. Inf Process Lett 90(1):7–14 (Apr)

Liu C, Veeraraghavant K, Iyengar V (2005) Thermal-aware test scheduling and hot spot temperature minimization for core-based systems. Proceedings of the IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems, pp 552–560

Mahajan R (2002) Thermal management of CPUs: a perspective on trends, needs and opportunities. Keynote presentation in the 8th International Workshop on THERMal INvestigations of ICs and Systems, Oct 2002. [Online] available: http://tima.imag.fr/Conferences/therminic/Therminic02/Posters/Rmahajan.pdf

Muresan V, Wang X, Vladutiu M (2000) A comparison of classical scheduling approaches in power-constrained block-test scheduling. Proceedings of the International Test Conference, pp 882–891

Murray BT, Hayes JP (1996) Testing ICs: getting to the core of the problem. IEEE Comput 29(11):32–38 (Nov)

Pouya B, Crouch A (2000) Optimization trade-offs for vector volume and test power. Proceedings of the International Test Conference, pp 873–881

Ravikumar CP, Chandra G, Verma A (2000) Simultaneous module selection and scheduling for power-constrained testing of core based systems. Proceedigs of the International Conference on VLSI Design, pp 462–467

Rosinger P, Al-Hashimi BM, Chakrabarty K (2006) Thermal-safe test scheduling for core-based system-on-Chip integrated circuits. IEEE Trans Comput Aided Des Integr Circuits Syst 25(11):2502–2512 (Nov)

Samii S, Larsson E, Chakrabarty K, Peng Z (2006) Cycle-accurate test power modeling and its application to SoC test scheduling. Proceedings of the International Test Conference, pp 1–10

Shi C, Kapur R (2004) How power-aware test improves reliability and yield. EETimes, Sep. 15, 2004. [Online] available http://www.eetimes.com/showArticle.jhtml?articleID=47208594

Skadron K, Stan MR, Huang W, Velusamy S, Sankaranarayanan K, Tarjan D (2003) Temperature-aware microarchitecture. Proceedings of the IEEE International Symposium on Computer Architecture, pp 2–13

Skadron K, Stan MR, Sankaranarayanan K, Huang W, Velusamy S, Tarjan D (2004) Temperature-aware microarchitecture: modeling and implementation. ACM Transactions on Architecture and Code Optimization 1(1):94–125 (Mar)

Van Hentenryck P (1991) The CLP language CHIP: constraint solving and applications. Proceedings of the IEEE Computer Society International Conference, pp 382–387

Varma P, Bhatia B (1998) A structured test re-use methodology for core-based system chips. Proceedings of the International Test Conference, pp 294–302

Zorian Y, Marinissen EJ, Dey S (1998) Testing embedded-core based system chips. Proceedings of the International Test Conference, pp 130–143

Acknowledgment

This work is partially supported by the Swedish Foundation for Strategic Research (SSF) under the Strategic Integrated Electronic Systems Research (STRINGENT) program through grants to Zhiyuan He, Zebo Peng, and Petru Eles. Funded in part by the EPSRC (UK) grants GR/S05557 and GR/S95770 to Paul Rosinger and Bashir M. Al-Hashimi.

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: N. A. Touba

Rights and permissions

About this article

Cite this article

He, Z., Peng, Z., Eles, P. et al. Thermal-Aware SoC Test Scheduling with Test Set Partitioning and Interleaving. J Electron Test 24, 247–257 (2008). https://doi.org/10.1007/s10836-007-5030-6

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-007-5030-6