Abstract

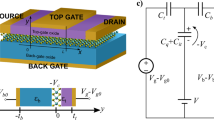

This paper presents a review on the development of parasitic-capacitance modeling for metal–oxide–semiconductor field-effect transistors (MOSFETs), covering models developed for the simple parallel-plate capacitance and the nonplanar and coplanar plate capacitances required for the intrinsic and extrinsic part of such devices. A comparative study of various extrinsic capacitance models with respect to a reference model is used to analyze the benefits of the various approaches. Capacitance models for basic MOSFETs and advance multigate FETs with two-dimensional (2D) and three-dimensional (3D) structures are reviewed. It is found that the elliptical field lines between the gate electrodes and source/drain region are modeled very well, while deviations of \(\pm 2 \%\) in the orthogonal plate capacitance are observed when the gate electrode thickness is varied from 5 to 20 nm .

Similar content being viewed by others

References

Parvais, B., Dehan, M., Subramanian, V., Mercha, A., Tamer San, K., Jurczak, M.: Analysis of the FinFET parasitics for improved RF performances. In: Proceedings of IEEE International SOI Conference, Indian Wells, CA, USA, pp. 37–38 (2007)

Tinoco, J.C., Salas, S., Martinez-Lopez, A.G., Alvarado, J., Raskin, J.P.: Impact of extrinsic capacitances on FinFET RF performance. IEEE Trans. Microw. Theory Tech. 61(2), 833–840 (2013)

Subramanian, V., Mercha, A., Parvais, B., Dehan, M., Groeseneken, G., Sansen, W., Decoutere, S.: Identifying the bottlenecks to the RF performance of FinFETs. In: Proceedings of 23rd International Conference on VLSI Design, pp. 111–116. India, Jan, Bangalore (2010)

Hashemi, S.A., Beigi, K., Jit, S.: Modeling of fringing capacitances of ion-implanted double-gate junctionless FETs using conformal mapping. IEEE Trans. Electron Devices 66, 4126–4133 (2019)

Sharma, Savitesh Madhulika, Dasgupta, S., Kartikeyan, M.V.: Successive conformal mapping technique to extract inner fringe capacitance of Underlap DG-FinFET and its variations with geometrical parameters. IEEE Trans. Electron Devices 64(2), 258–265 (2017)

Wu, W., Chan, M.: Analysis of geometry-dependent parasitics in multifin double gate FinFETs. IEEE Trans. Electron Devices 54(4), 692–698 (2007)

Reuhli, A.E., Brennan, P.A.: Capacitance models for integrated circuit metallization wires. IEEE Solid State Circuits Soc. SC–10, 530–536 (1975)

Kamchouchi, H., Zaky, A.: A direct method for the edge capacitance of thick electrodes. J. Phys. D Appl. Phys. 8(12), 1365–1371 (1975)

Elsmary, M.I.: Capacitance calculations in MOSFET VLSI. IEEE Electron Devices Lett. EDL–3(1), 6–7 (1982)

Sakurai, T., Tamaru, K.: Simple formulas for to dimensional capacitances. IEEE Trans. Electron Devices ED–30, 183–185 (1983)

Shrivastava, R., Fitzpatrick, K.: A simple model for the overlap capacitance of VLSI MOS devices. IEEE Trans. Electron Devices ED–29(12), 1870–1875 (1982)

Greeneich, E.W.: An analytical method for the gate capacitance of small geometry MOS structures. IEEE Trans. Electron Devices ED–30(12), 1838–1839 (1983)

Suzuki, K.: Parasitic capacitance of submicrometer MOSFET’s. IEEE Trans. Electron Devices 46(9), 1895–1900 (1999)

Liu, W.: MOSFET Models for SPICE Simulation Including BSIM3v3 and BSIM4. Wiley, New York (2001)

Hiblot, G., Rafhay, Q., Boeuf, F.: Refined conformal mapping model for MOSFET parasitic capacitances based on elliptic integrals. IEEE Trans. Electron Devices 62(3), 972–979 (2015)

Mohapatra, N.R., Desai, M.P., Narendra, S.G., Rao, V.R.: Modeling of parasitic capacitances in deep submicrometer conventional and high-K dielectric MOS transistors. IEEE Trans. Electron Devices 50(4), 959–966 (2003)

Bansal, A., Paul, B.C., Roy, K.: Modeling and optimization of fringe capacitance of nanoscale DGMOS devices. IEEE Trans. Electron Devices 52(2), 256–262 (2005)

Bansal, A., Paul, B.C., Roy, K.: An analytical fringe capacitance model for interconnects using conformal mapping. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 25(12), 2765–2774 (2006)

Plonsey, R., Collins, R.E.: Principles and Applications of Electromagnetic Fields. McGraw-Hill, New York (1961)

Xiong, S., King, T., Bokor, J.: Study of the extrinsic parasitics in nano-scale transistors. Semicond. Sci. Technol. 20, 652–657 (2005)

Roy, A., Enz, C.C., Sallese, J.M.: Compact modeling of gate sidewall capacitance of DG-MOSFET. IEEE Trans. Electron Devices 53(10), 2655–2657 (2006)

Ji, F., Xua, J.P., Lai, P.T., Guand, J.G.: A fringing-capacitance model for deep-submicron MOSFET with high-k gate dielectric. Microelectron. Reliab. 48(5), 693–697 (2008)

Ghione, G., Naldi, C.U.: Coplanar waveguides for MMIC applications: effects of upper shielding, conductor backing, finite-extent ground planes, and line-to-line coupling. IEEE Trans. Microw. Theory Tech. 35(3), 260–267 (1987)

Liu, X., Jin, X., Lee, J.: A compact model of fringing field induced parasitic capacitance for deep sub-micrometer MOSFETs. Solid State Electron. 53(9), 1041–1045 (2009)

Lacord, J., Boeuf, F.: Comprehensive and accurate parasitic capacitance models for two- and three dimensional CMOS device structures. IEEE Trans. Electron Devices 59(5), 1332–1344 (2012)

Lee, K., An, T., Joo, S., Kwon, K., Kim, S.: Modeling of parasitic fringing capacitance in multifin trigate FinFETs. IEEE Trans. Electron Devices 60(5), 1786–1789 (2013)

Anderson, J.D.: Fundamentals of Aerodynamics, 2nd edn, p. 719. McGraw Hill, New York (1991)

Rodriguez, S.S., Tinoco, J.C., Martinez-Lopez, A.G., Alvarado, J., Raskin, J.P.: Parasitic gate capacitance model for triple-gate FinFETs. IEEE Trans. Electron Devices 60(11), 3710–3717 (2013)

An, T., Choe, K., Kwon, K., Kim, S.: Performance optimization study of FinFETs considering parasitic capacitance and resistance. J. Semicond. Technol. Sci. 14(5), 525–536 (2014)

Kim, S.H., Fossum, J.G., Yang, J.W.: Modeling and significance of fringe capacitance in non-classical CMOS devices with gate-source/drain underlap. IEEE Trans. Electron Devices 53(9), 2143–2149 (2006)

Acknowledgements

The authors would like to thank the Department of Electronics and Communication Engineering, IIT Roorkee, for their valuable support in carrying out this research work.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Sharma, S.M., Singh, A., Dasgupta, S. et al. A review on the compact modeling of parasitic capacitance: from basic to advanced FETs. J Comput Electron 19, 1116–1125 (2020). https://doi.org/10.1007/s10825-020-01515-4

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-020-01515-4