Abstract

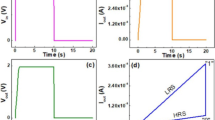

Memristive crossbar arrays are believed to be the future of high-density nonvolatile memory and neuromorphic systems. However, significant challenges related to the passive crossbar architecture, for example, the sneak current issue, impose limitations on their performance. One of the well-known ways to overcome this problem is to use a one-transistor one-memristor (1T1M) scheme. Nevertheless, for a sufficiently large crossbar, even with a 1T1M architecture, problems appear not only with sneak currents but also with leakage through the gates of the transistors and the discharge of their capacitances. These effects are analyzed herein by simulations and analytically to determine their influence on the performance of a 1T1M crossbar, depending on its dimensions. Numerical results are presented for the examples of \(\mathrm{(CoFeB)}_x(\mathrm{LiNbO}_3)_{100-x}\) nanocomposite and \(\mathrm{ZrO}_2\)(Y)-based memristive structures. The results reveal that the sneak, discharge, and (to a lesser extent) leakage currents can severely degrade the performance of even a not very large (\(<\,10^3\times 10^3\)) 1T1M crossbar. Finally, analytical estimates are used to reveal how a well-known, simple special scheme for switching and reading can fix these negative effects, even for a 1T1M memristive crossbar with rather large dimensions (\(\sim \,10^6\times 10^6\)), taking into account its plausible geometrical size and the scaling dependence of its constituent elements.

Similar content being viewed by others

References

He, K., Zhang, X., Ren, S., Sun, J.: Deep residual learning for image recognition. In: Proceedings of the IEEE Conference on Computer Vision and Pattern Recognition, Las Vegas, NV, USA. 27–30, pp. 770–778 (June 2016)

Krizhevsky, A., Sutskever, I., Hinton, G.E.: Imagenet classification with deep convolutional neural networks. In: Pereira, F., Burges, C.J.C., Bottou, L., Weinberger, K.Q. (eds.) Advances in Neural Information Processing Systems. Neural Information Processing Systems Foundation, Inc., Vancouver, BC, Canada, pp. 1097–1105 (2012)

Xu, H., Gao, Y., Yu, F., Darrell, T.: End-to-end learning of driving models from large-scale video datasets. In: CVPR (2017)

Bojarski, M., Testa, D.D., Dworakowski, D., Firner, B., Flepp, B., Goyal, P., Jackel, L.D., Monfort, M., Muller, U., Zhang, J., Zhang, X., Zhao, J., Zieba, K.: End to end learning for self-driving cars. CoRR arxiv:abs/1604.07316 (2016)

Hundelshausen, F., Himmelsbach, M., Hecker, F., Mueller, A., Wuensche, H.J.: Driving with tentacles—integral structures for sensing and motion. In: Buehler, M., Iagnemma, K., Singh, S. (eds.) The DARPA Urban Challenge. Springer Tracts in Advanced Robotics, vol. 56. Springer, Berlin (2009)

Akopyan, F., et al.: TrueNorth: design and tool flow of a 65 mW 1 million neuron programmable neurosynaptic chip. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 34(10), 1537–1557 (2015)

Sharp, T., Galluppi, F., et al.: Power-efficient simulation of detailed cortical microcircuits on SpiNNaker. J. Neurosci. Methods 1, 110–118 (2015)

Benjamin, B.V., Gao, P., McQuinn, E.: Neurogrid: a mixed-analog-digital multichip system for large-scale neural simulations. Proc. IEEE 102, 699–716 (2014)

Meier, K.: A mixed-signal universal neuromorphic computing system. In: 2015 IEEE International Electron Devices Meeting (IEDM), pp. 4.6.1–4.6.4 (Dec 2015)

Davies, M., Srinivasa, N., Lin, T., Chinya, G., Cao, Y., Choday, S.H., Dimou, G., Joshi, P., Imam, N., Jain, S., Liao, Y., Lin, C., Lines, A., Liu, R., Mathaikutty, D., McCoy, S., Paul, A., Tse, J., Venkataramanan, G., Weng, Y., Wild, A., Yang, Y., Wang, H.: Loihi: a neuromorphic manycore processor with on-chip learning. IEEE Micro 38(1), 82–99 (2018)

Prezioso, M., Merrikh-Bayat, F., Hoskins, B.D., Adam, G.C., Likharev, K.K., Strukov, D.B.: Training and operation of an integrated neuromorphic network based on metal-oxide memristors. Nature 521, 61–64 (2015)

Jiang, H., Han, L., Lin, P., Wang, Z., Jang, M.H., Wu, Q., et al.: Sub-10 nm Ta channel responsible for superior performance of a HfO\(_2\) memristor. Sci. Rep. 6, 28525 (2016)

Minnekhanov, A.A., Emelyanov, A.V., Lapkin, D.A., Nikiruy, K.E., Shvetsov, B.S., Nesmelov, A.A., Rylkov, V.V., Demin, V.A., Erokhin, V.V.: Parylene based memristive devices with multilevel resistive switching for neuromorphic applications. Sci. Rep. 9, 10800 (2019)

Li, C., Belkin, D., Li, Y., Yan, P., Hu, M., Ge, N., et al.: Efficient and self-adaptive in-situ learning in multilayer memristor neural networks. Nat. Commun. 9(1), 2385 (2018)

Cai, F., et al.: A fully integrated reprogrammable memristor–CMOS system for efficient multiply–accumulate operations. Nat. Electron. 2(7), 290–299 (2019)

Emelyanov, A.V., Lapkin, D.A., Demin, V.A., Erokhin, V.V., Battistoni, S., Baldi, G., et al.: First steps towards the realization of a double layer perceptron based on organic memristive devices. AIP Adv. 6(11), 111301 (2016)

Kim, K.-H., Gaba, S., et al.: A Functional hybrid memristor crossbar-array/CMOS system for data storage and neuromorphic applications. Nano Lett. 12(1), 389–395 (2012)

Zidan, M.A., Fahmy, H.A.H., Hussain, M.M., Salama, K.N.: Memristor-based memory: the sneak paths problem and solutions. Microelectron. J. 44, 176–183 (2013)

Srinivasan, V., Chopra, S., et al.: Punchthrough-diode-based bipolar RRAM selector by Si epitaxy. IEEE Electron Device Lett. 33(10), 1396–1398 (2012)

Kim, S., et al.: Performance of threshold switching in chalcogenide glass for 3D stackable selector. In: Proceedings of Symposium on VLSIT, pp. T240–T241 (June 2013)

Lee, W., et al.: Varistor-type bidirectional switch (JMAX > 107A/cm2, selectivity~104) for 3D bipolar resistive memory arrays. In: Proceedings of Symposium on VLSIT, pp. 37–38 (June 2012)

Gi, S., Yeo, I., Chu, M., Kim, S., Lee, B.: Fundamental issues of implementing hardware neural networks using memristor. In: International SoC Design Conference (ISOCC), pp. 215–216. IEEE (2015)

Yakopcic, C., Taha, T.M., et al.: Analysis of a memristor based 1T1M crossbar architecture. In: International Joint Conference on Neural Networks (2012)

Li, C., Joshua Yang, J., Xia, Q., et al.: Analogue signal and image processing with large memristor crossbars. Nat. Electron. 1, 52–59 (2018)

Yao, P., et al.: Face classification using electronic synapses. Nat. Commun. 8, 15199 (2017)

Yao, P., Wu, H., Gao, B., et al.: Fully hardware-implemented memristor convolutional neural network. Nature 577, 641–646 (2020)

Danilin, S.N., Shchanikov, S.A., Bordanov, I.A., Zuev, A.D.: Using simulation to define the tolerances for the information and physical parameters of memristors-based artificial neural networks. J. Phys.: Conf. Ser. 1333, 062026 (2019)

Querlioz, D., Bichler, O., Dollfus, P., Gamrat, C.: Immunity to device variations in a spiking neural network with memristive nanodevices. IEEE Trans. Nanotechnol. 12, 288–295 (2013). https://doi.org/10.1109/TNANO.2013.2250995

Shahrabi, E., Attarimashalkoubeh, B., Sandrini, J., Leblebici, Y.: Towards chip-level reram-cmos co-integration. In: International Conference on Memristive Materials, Devices and Systems (MEMRYSIS) (2017). https://doi.org/10.1109/PRIME.2016.7519497

Aziza, H., Canet, P., Postel-Pellerin, J., Moreau, M., Portal, J.M., Bocquet, M.: ReRAM ON/OFF resistance ratio degradation due to line resistance combined with device variability in 28 nm FDSOI technology. In: Ultimate Integration on Silicon (EUROSOI-ULIS) (2017). https://doi.org/10.1109/ULIS.2017.7962594

Nikiruy, K.E., et al.: Dopamine-like STDP modulation in nanocomposite memristors. AIP Adv. 9, 065116 (2019)

Rylkov, V.V., Sitnikov, A.V., Nikolaev, S.N., Demin, V.A.: Transport, magnetic and memristive properties of nanograined composite (CoFeB)\(_x\)(LiNbO\(_3\))\(_{100-x}\). JETP 153(3), 424–441 (2018). https://doi.org/10.7868/S0044451018030094

Rylkov, V.V., Sitnikov, A.V., Nikolaev, S.N., Demin, V.A.: Properties of nanogranular (CoFeB)\(_x\)(AlO\(_y\))\(_{100-x}\) and (CoFeB)\(_x\)(LiNbO\(_y\))\(_{100-x}\) nanocomposites: manifestation of superferromagnetic ordering effects. J. Magn. Magn. Mater. (2017). https://doi.org/10.1016/j.jmmm.2017.11.022

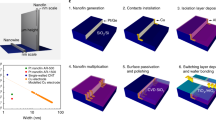

Emelyanov, A.V., Nikiruy, K.E., Serenko, A.V., Sitnikov, A.V., Yu Presnyakov, M., Rybka, R.B., Sboev, A.G., Rylkov, V.V., Kashkarov, P.K., Kovalchuk, M.V., Demin, V.A.: Self-adaptive STDP-based learning of a spiking neuron with nanocomposite memristive weights. Nanotechnology 31, 045201 (2020). https://doi.org/10.1088/1361-6528/ab4a6d

Mikhaylov, A.N., et al.: Field- and irradiation-induced phenomena in memristive nanomaterials. Phys. Status Solidi C 3, 870–881 (2016)

Emelyanov, A.V., et al.: Yttria-stabilized zirconia cross-point memristive devices for neuromorphic applications. Microelectron. Eng. 215, 110988 (2019)

Kim, S., Chen, J., Chen, Y.C., Kim, M.H., Kim, H., Kwon, M.W., et al.: Neuronal dynamics in HfO x/AlO y-based homeothermic synaptic memristors with low-power and homogeneous resistive switching. Nanoscale 11(1), 237–245 (2019)

Yun, M.J., Kim, S., Kim, S., Kim, H.D.: Memory state protected from leakage current in Ti/SiN/NiN/Pt bilayer resistive random-access memory devices for array applications. Semicond. Sci. Technol. 34(7), 075030 (2019)

Kvatinsky, S., Friedman, E.G., Kolodny, A., Weiser, U.C.: Team: threshold adaptive memristor model. IEEE Trans. Circuits Syst. I Regul. Pap. 60(1), 211–221 (2013)

Kvatinsky, S., et al.: VTEAM—a general model for voltage controlled memristors. IEEE Trans. Circuits Syst.—II: Express Briefs 62(8), 786–790 (2015)

Mladenov, V., Kirilov, S.: A memristor model with a modified window function and activation thresholds. In: 2018 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1–5. IEEE (2018)

Amer, S., Sayyaparaju, S., Rose, G.S., Beckmann, K., Cady, N.C.: A practical hafnium-oxide memristor model suitable for circuit design and simulation. In: 2017 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1–4. IEEE (2017)

Berdan, R., Lim, C., Khiat, A., Papavassiliou, C., Prodromakis, T.: A memristor spice model accounting for volatile characteristics of practical ReRAM. IEEE Electron Device Lett. 35(1), 135–137 (2014)

Biolek, Z., Biolek, D., Biolkova, V.: SPICE model of memristor with nonlinear dopant drift. Radioengineering 18(2), 210–214 (2009)

Chang, T., Jo, S.H., Kim, K.H., Sheridan, P., Gaba, S., Lu, W.: Synaptic behaviors and modeling of a metal oxide memristive device. Appl. Phys. A 102(4), 857–863 (2011)

García-Redondo, F., Gowers, R.P., Crespo-Yepes, A., López-Vallejo, M., Jiang, L.: Spice compact modeling of bipolar/unipolar memristor switching governed by electrical thresholds. IEEE Trans. Circuits Syst. I Regul. Pap. 63(8), 1255–1264 (2016)

Yakopcic, C., Taha, T.M., Subramanyam, G., Pino, R.E.: Generalized memristive device spice model and its application in circuit design. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 32(8), 1201–1214 (2013)

Siemon, A., Ferch, S., Heittmann, A., Waser, R., Wouters, D.J., Menzel, S.: Analyses of a 1-layer neuromorphic network using memristive devices with non-continuous resistance levels. APL Mater. 7, 091110 (2019)

BSIMSOIv4.4 MOSFET MODEL Users “Manual”. BSIM GROUP (2010)

Yang, J.Joshua, Xia, Qiangfei, et al.: Long short-term memory networks in memristor crossbar arrays. Nat. Mach. Intell. 1, 49–57 (2019)

Yoo, Hyeonjoong, Pimmel, Russell L.: The effect of weight precision and range on neural network classifier performance. Neurocomputing 6, 541–549 (1994)

Shevgoor, M., et al.: Improving memristor memory with sneak current sharing. In: 33rd IEEE International Conference on Computer Design (ICCD) (2015)

Kataeva, I. et al.: Towards the development of analog neuromorphic chip prototype with 2.4 M integrated memristors. 2019 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1–5. IEEE (2019)

Merrikh-Bayat, F., Merrikh-Bayat, F., Shouraki, S.B.: The neuro-fuzzy computing system with the capacity of implementation on a memristor crossbar and optimization-free hardware training. IEEE Trans. Fuzzy Syst. 22(5), 1272–1287 (2014)

Sun, Sheng-Yang, Li, Z., Li, J., Liu, H., Liua, H., Li, Q.: A memristor-based convolutional neural network with full parallelization architecture. IEICE Electron. Express 16(3), 1–12 (2019)

Acknowledgements

This work was supported by a research project of the NRC “Kurchatov” Institute NBICS Center.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Demin, V.A., Surazhevsky, I.A., Emelyanov, A.V. et al. Sneak, discharge, and leakage current issues in a high-dimensional 1T1M memristive crossbar. J Comput Electron 19, 565–575 (2020). https://doi.org/10.1007/s10825-020-01470-0

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-020-01470-0