Abstract

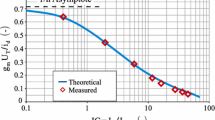

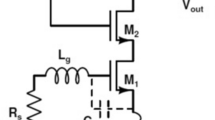

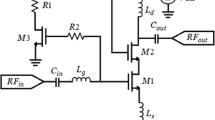

The design of a low-power, high-gain, highly linear complementary metal–oxide–semiconductor (CMOS) cascode low-noise amplifier (LNA) with an inductive source degeneration circuit for use at 5.5 GHz frequency is optimized using a flower pollination algorithm (FPA) as an evolutionary technique. The FPA is applied to optimize the noise figure (NF) while validating all the design constraints, e.g., on the gain, power dissipation, linearity, stability, and input and output matching. Optimal sizing of the MOS transistors present in the LNA circuit is achieved by using the FPA. Moreover, the FPA helps to estimate the optimal values of the other elements in the LNA circuit. The FPA-based optimal design parameters are used to implement the CMOS LNA circuit in CADENCE IC 6.1.6 software at the UMC 180-nm technology node with a supply voltage of 1.8 V. The designed LNA achieves an input third-order intercept point (IIP3) of 1.77 dBm, power dissipation of 4.29 mW, NF of 0.686 dB, and gain of 24.42 dB at 5.5 GHz. The FPA-based optimal design for the CMOS cascode LNA yields remarkably improved results compared with those in previous literature in terms of the gain, noise figure, power dissipation, and area.

Similar content being viewed by others

References

Lee, T.H., Samavati, H., Rategh, H.R.: 5-GHz CMOS wireless LANs. IEEE Trans. Microw. Theory Tech. 50(1), 268–280 (2002). https://doi.org/10.1109/22.981280

Shams, M., Rashedi, E., Hakimi, A.: Clustered-gravitational search algorithm and its application in parameter optimization of a low noise amplifier. Appl. Math. Comput. 258, 436–453 (2015). https://doi.org/10.1016/j.amc.2015.02.020

Kumar, R., Rajan, A., Talukdar, F.A., Dey, N., Santhi, V., Balas, V.E.: Optimization of 5.5-GHz CMOS LNA parameters using firefly algorithm. Neural Comput. Appl. 28(12), 3765–3779 (2017). https://doi.org/10.1007/s00521-016-2267-y

Mallick, S., Akhil, J.R., Dasgupta, A., Kar, R., Mandal, D., Ghoshal, S.P.: Optimal design of 5.5 GHz CMOS LNA using hybrid fitness based adaptive DE with PSO. In: 5th International Electrical Engineering Congress (iEECON), pp. 1–4 (2017). https://doi.org/10.1109/IEECON.2017.8075890

Kumar, R., Talukdar, F.A., Rajan, A., Devi, A., Raja, R.: Parameter optimization of 5.5 GHz low noise amplifier using multi-objective Firefly Algorithm. Microsyst. Technol. (2018). https://doi.org/10.1007/s00542-018-4034-8

Li, Y.: A simulation-based evolutionary approach to LNA circuit design optimization. Appl. Math. Comput. 209(1), 57–67 (2009). https://doi.org/10.1016/j.amc.2008.06.015

Pandey, S., Gawande, T., Pathak, A., Kondekar, P.N.: A 0.9-V, 4.4-mW CMOS LNA with wideband input match and high gain for UWB applications. Int. J. Lett. 6(3), 329–337 (2018). https://doi.org/10.1080/21681724.2017.1378373

Oh, N.J.: A low-power switchable dual-band CMOS LNA for 802.11 a/b/g WLAN applications. IETE J. Res. 57(6), 563–567 (2011). https://doi.org/10.4103/0377-2063.92273

Lee, M., Kwon, I.: A 3–10 GHz noise-cancelling CMOS LNA using gm—boosting technique. IET Circuits Devices Syst. 12(1), 12–16 (2018). https://doi.org/10.1049/iet-cds.2017.0094

Khurram, M., SMR, S.M.R.: A 3–5 GHz current-reuse gm-boosted CG LNA for ultrawideband in 130 nm CMOS. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 20(3), 400–409 (2012). https://doi.org/10.1109/TVLSI.2011.2106229

Chang, C.P., Chen, J.H., Wang, Y.H.: A fully integrated 5 GHz low-voltage LNA using forward body bias technology. IEEE Microw. Wirel. Compon. Lett. 19(3), 176–178 (2009)

Liu, B., Wang, C., Ma, M., Guo, S.: An ultra-low-voltage and ultra-low-power 2.4 GHz LNA design. Radioengineering 18(4), 527–531 (2009)

Jafarnejad, R., Jannesari, A., Nabavi, A., Sahafi, A.: A low power low noise amplifier employing negative feedback and current reuse techniques. Microelectron. J. 49, 49–56 (2016). https://doi.org/10.1016/j.mejo.2015.12.011

Wan, Q., Wang, C.: Design of 3.1–10.6 GHz ultra-wideband CMOS low noise amplifier with current-reuse technique. Int. J. Electron. Commun. (AEÜ) 65(12), 1006–1011 (2011). https://doi.org/10.1016/j.aeue.2011.03.016

Hayati, M., Cheraghaliei, S., Zarghami, S.: Design of UWB low noise amplifier using noise-cancelling and current-reused techniques. Integr. VLSI J. 60, 232–239 (2018). https://doi.org/10.1016/j.vlsi.2017.10.002

Kumar, R., Devi, A., Sarkar, A., Talukdar, F.A.: Design of 5.5 GHz linear low noise amplifier using the post-distortion technique with body biasing. Microsyst. Technol. 22(11), 2681–2690 (2016). https://doi.org/10.1007/s00542-015-2556-x

Zokaei, A., Amirabadi, A.: A 65 nm linear broad-band differential low noise amplifier using the post-distortion technique. Microelectron. J. 74, 24–33 (2018). https://doi.org/10.1016/j.mejo.2018.01.007

Chang, C., Chen, J., Hung, S., Su, C., Wang, Y.: A novel post-linearization technique for fully integrated 5.5 GHz high-linearity LNA. In: 2009 Fourth International Conference on Innovative Computing, Information and Control (ICICIC), pp. 577–580 (2009). https://doi.org/10.1109/ICICIC.2009.40

Seyedhosseinzadeh, N., Nabavi, A.: A highly linear CMOS low noise amplifier for K-band applications. Int. J. Electron. 101(12), 1607–1620 (2014). https://doi.org/10.1080/00207217.2014.888775

Jafarnejad, R., Jannesari, A., Sobhi, J.: A linear ultra wide band low noise amplifier using pre-distortion technique. Int. J. Electron. Commun. (AEÜ) 79, 172–183 (2017)

Jafarnejad, R., Jannesari, A., Sobhi, J.: Pre-distortion technique to improve linearity of low noise amplifier. Microelectron. J. 61, 95–105 (2017)

Jadhav, V.P., Mali, M.B.: A 2.4 GHz low power, high gain CMOS RF LNA in 90 nm technology. Int. J. Eng. Res. Technol. 3, 581–583 (2014)

Lee, T.H.: The Design of CMOS Radio-Frequency Integrated Circuits, 2nd edn. Cambridge University Press, Cambridge (2004)

Andreani, P., Sjoland, H.: Noise optimization of an inductively degenerated CMOS low noise amplifier. IEEE Trans. Circuits Syst. II Analog Digit. Signal Process. 48(9), 835–841 (2001). https://doi.org/10.1109/82.964996

Ziel, A.V.: Noise in solid-state devices and lasers. Proc. IEEE 58(8), 1178–1206 (1970)

Hoe, D.H.K., Jin, X.: The design of low noise amplifiers in deep submicron CMOS processes: a convex optimization approach. VLSI Des. (2015). https://doi.org/10.1155/2015/312639

Wang, S., Huang, B.Z.: A high-gain CMOS LNA for 2.4/5.2-GHz WLAN applications. Prog. Electromagn. Res. 21, 155–167 (2011)

Mahata, S., Saha, S.K., Kar, R., Mandal, D.: Optimal design of fractional-order digital differentiator using flower pollination algorithm. J. Circuits Syst. Comput. 27(8), 1850129-1–1850129-35 (2018). https://doi.org/10.1142/S0218126618501293

Ram, G., Kar, R., Mandal, D., Ghoshal, S.P.: Optimal design of linear antenna arrays of dipole elements using flower pollination algorithm. IETE J. Res. (2018). https://doi.org/10.1080/03772063.2018.1452639

Mahata, S., Saha, S.K., Kar, R., Mandal, D.: Optimal design of wideband digital integrators and differentiators using hybrid flower pollination algorithm. Soft. Comput. 22(11), 3757–3783 (2018). https://doi.org/10.1007/s00500-017-2595-6

Yang, X.S.: Flower pollination algorithm for global optimization. Unconventional computation and natural computation. In: Durand-Lose, J., Jonoska, N. (eds) Unconventional Computation and Natural Computation. UCNC 2012. Lecture Notes in Computer Science, vol. 7445, pp. 240–249. Springer, Berlin (2012). https://doi.org/10.1007/978-3-642-32894-7_27

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Ghosh, S., De, B.P., Kar, R. et al. Optimal design of a 5.5-GHz low-power high-gain CMOS LNA using the flower pollination algorithm. J Comput Electron 18, 737–747 (2019). https://doi.org/10.1007/s10825-019-01322-6

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-019-01322-6