Abstract

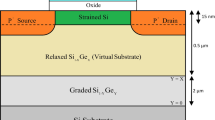

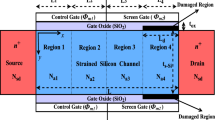

Negative Bias Temperature Instability (NBTI) in p-MOSFETs is a serious reliability concern for digital and analog CMOS circuit applications. Strain in the channel region affects negative bias temperature instabilities, low frequency noise, radiation hardness, gate oxide quality and hot carrier performance. The understanding of these phenomena in strain-engineered p-MOSFETs from fundamental physics is essential. In this paper, technology CAD (TCAD) has been used to study the effects of strain on the negative bias temperature instabilities in p-MOSFETs. A quasi two dimensional (quasi-2D) physics-based Coulomb scattering mobility model for strained-Si has been developed and implemented in Synopsys Sentaurus Device tool for device simulation to understand NBTI in strain-engineered p-MOSFETs.

Similar content being viewed by others

References

Maiti, C.K., Chattopadhyay, S., Bera, L.K.: Strained-Si Heterostructure Field Effect Devices. CRC Press, Boca Raton (2007)

Thompson, S.E., et al.: A 90-nm logic technology featuring strained-Silicon. IEEE Trans. Electron Devices 51, 1790 (2004)

Liu, C.-H., Pan, T.-M.: Hot carrier and negative-bias temperature instability reliabilities of strained-Si MOSFETs. IEEE Trans. Electron Devices 54, 1799 (2007)

Dalapati, G.K., et al.: Impact of strained-Si thickness and Ge out-diffusion on gate oxide quality for strained-Si surface channel n-MOSFETs. IEEE Trans. Electron Devices 53(5), 1142 (2006)

Synopsys, Inc. Mountain View, California: Sentaurus Process User Manual, Version A-2007.12. March 2008

Synopsys, Inc. Mountain View, California: Sentaurus Device User Manual, Version A-2007.12. March 2008

Ghani, T., et al.: A 90 nm high volume manufacturing logic technology featuring novel 45 nm gate length strained silicon CMOS transistors. IEDM Tech. Dig. 978 (2003)

Stern, F., Howard, W.E.: Properties of semiconductor surface inversion layers in the electric quantum limit. Phys. Rev. 163, 816 (1967)

Inoue, K., et al.: Electron mobilities in modulation-doped Al x Ga1−x As/GaAs and pseudomorphic Al x Ga1−x As/In y Ga1−y As quantum-well structures. Phys. Rev. B Condens. Matter 47, 3771 (1993)

Schiff, L.I.: Quantum Mechanics. McGraw-Hill, New York (1968)

Alam, M.A., Mahapatra, S.: A comprehensive model of PMOS NBTI degradation. Microelectron. Reliab. 45, 71 (2005)

Kaczer, B., Arkhipov, V., Jurczak, M., Groeseneken, G.: Negative Bias Temperature Instability (NBTI) in SiO2 and SiON gate dielectrics understood through disorder-controlled kinetics. Microelectron. Eng. 80, 122 (2005)

Agostinelli, M., Lau, S., Pae, S., Marzolf, P., Muthali, H., Jacobs, S.: PMOS NBTI-induced circuit mismatch in advanced technologies. Microelectron. Reliab. 46, 63 (2006)

Kufluoglu, H., Alam, M.A.: A geometrical unification of the theories of NBTI and HCI time-exponents and its implications for ultra-scaled planar and surround gate MOSFETs. IEDM Tech. Dig. 113 (2004)

Kufluoglu, H., Alam, M.A.: A generalized reaction-diffusion model with explicit H-H2 dynamics for negative-bias temperature-instability (NBTI) degradation. IEEE Trans. Electron Devices 54, 1101 (2007)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Maiti, T.K., Mahato, S.S., Chakraborty, P. et al. Negative bias temperature instability in strain-engineered p-MOSFETs: a simulation study. J Comput Electron 9, 1–7 (2010). https://doi.org/10.1007/s10825-009-0270-6

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-009-0270-6