Abstract

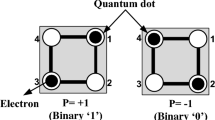

Quantum-dot Cell Automata (QCA) technology is a promising alternative technology for CMOS technology. In this technology, the ultra-dense and low-latency digital circuits are designed. One of the important digital circuits is Full Adder (FA). In this paper, a new and efficient multilayer QCA full adder circuit is designed and evaluated. In the designed full adder circuit, sum and carry output are designed in separated layers. Then, a novel and efficient 4-bit Ripple Carry Adder (RCA) circuit is designed based on this new FA circuit. The proposed QCA circuits are simulated using QCADesigner tool version 2.0.3. The simulation results show that the proposed 4-bit QCA RCA requires 135 QCA cells, 0.06 μm2 area and 5 clock phases. The comparison shows that the proposed QCA circuits have advantages compared to other QCA circuits in terms of area, latency, and cost.

Similar content being viewed by others

References

Karimi, A., Rezai, A.: A design methodology to optimize the device performance in CNTFET. ECS J. Solid State Sci. Technol. 6(8), M97–M102 (2017)

Zareiee, M.: A novel high performance nano-scale MOSFET by inserting Si3N4 layer in the channel. Superlattice. Microst. 88, 254–261 (2015)

Zareiee, M.: Modifying buried layers in nano-MOSFET for achieving reliable electrical characteristics. ECS J. Solid State Sci. Technol. 5(10), M113–M117 (2016)

Zareiee, M.: High performance Nano device with reduced Short Channel effects in high temperature applications. ECS J. Solid State Sci. Technol. 6(7), M75–M78 (2017)

Zareiee, M., Mehrad, M.: A reliable Nano device with appropriate performance in high temperatures. ECS J. Solid State Sci. Technol. 6(4), M50–M54 (2017)

Zareiee, M., Orouji, A.A.: Superior electrical characteristics of novel nanoscale MOSFET with embedded tunnel diode. Superlattice. Microst. 101, 57–67 (2017)

Mehrad, M.: Reducing floating body and Short Channel effects in Nano scale transistor: inserted P+ region SOI-MOSFET. ECS J. Solid State Sci. Technol. 5(9), M88–M92 (2016)

Mehrad, M.: Application of N+ buried layer in reducing lattice temperature of Nano-scale MOSFET. ECS J. Solid State Sci. Technol. 5(12), M158–M162 (2016)

Cho, G., Kim, Y.-B., Lombardi, F.: Assessment of CNTFET based circuit performance and robustness to PVT variations. In: Circuits and Systems, 2009. MWSCAS'09. 52nd IEEE International Midwest Symposium on 2009, pp. 1106–1109. IEEE (2009)

Shafizadeh, M., Rezai, A.: Improved device performance in a CNTFET using La2O3 high-κ dielectrics. J. Comput. Electron. 16(2), 221–227 (2017)

Karimi, A., Rezai, A.: Improved device performance in CNTFET using genetic algorithm. ECS J. Solid State Sci. Technol. 6(1), M9–M12 (2017)

Naderi, A., Tahne, B.A.: T-CNTFET with gate-drain overlap and two different gate metals: a novel structure with increased saturation current. ECS J. Solid State Sci. Technol. 5(8), M3032–M3036 (2016)

Naderi, A., Ahmadmiri, S.A.: Attributes in the performance and design considerations of asymmetric drain and source regions in carbon Nanotube field effect transistors: quantum simulation study. ECS J. Solid State Sci. Technol. 5(7), M63–M68 (2016)

Seminario, J.M., Derosa, P.A., Cordova, L.E., Bozard, B.H.: A molecular device operating at terahertz frequencies: theoretical simulations. IEEE Trans. Nanotechnol. 3(1), 215–218 (2004)

Abu El-Seoud, A., El-Banna, M., Hakim, M.: On modelling and characterization of single electron transistor. Int. J. Electron. 94(6), 573–585 (2007)

Meng, H., Wang, J., Wang, J.-P.: A spintronics full adder for magnetic CPU. IEEE electr. Dev. lett. 26(6), 360–362 (2005)

Balali, M., Rezai, A., Balali, H., Rabiei, F., Emadi, S.: A novel design of 5-input majority gate in quantum-dot cellular automata technology. In: Computer Applications & Industrial Electronics (ISCAIE), 2017 IEEE Symposium on 2017, pp. 13–16. IEEE

Kim, K., Wu, K., Karri, R.: Towards designing robust QCA architectures in the presence of sneak noise paths. In: Proceedings of the conference on Design, Automation and Test in Europe-Volume 2 2005, pp. 1214–1219. IEEE Computer Society (2005)

Kim, K., Wu, K., Karri, R.: Quantum-dot cellular automata design guideline. IEICE Trans. Fundam. Electron. Commun. Comput. Sci. 89(6), 1607–1614 (2006)

Niemier, M.T.: Designing digital systems in quantum cellular automata. University of Notre Dame (2000)

Balali, M., Rezai, A., Balali, H., Rabiei, F., Emadi, S.: Towards coplanar quantum-dot cellular automata adders based on efficient three-input XOR gate. Results Phys. 7, 1389–1395 (2017)

Navi, K., Farazkish, R., Sayedsalehi, S., Azghadi, M.R.: A new quantum-dot cellular automata full-adder. Microelectron. J. 41(12), 820–826 (2010)

Swartzlander, E.E., Cho, H., Kong, I., Kim, S.-W.: Computer arithmetic implemented with QCA: A progress report. In: Signals, Systems and Computers (ASILOMAR), 2010 Conference Record of the Forty Fourth Asilomar Conference on 2010, pp. 1392–1398. IEEE (2010)

Liu, W., Lu, L., O'Neill, M., Swartzlander, E.E.: Design rules for quantum-dot cellular automata. In: Circuits and Systems (ISCAS), 2011 IEEE International Symposium on 2011, pp. 2361–2364. IEEE (2011)

Sabbaghi-Nadooshan, R., Kianpour, M.: A novel QCA implementation of MUX-based universal shift register. J. Comput. Electron. 13(1), 198–210 (2014)

Mustafa, M., Beigh, M.: Novel Linear Feedback Shift Register Design in Quantum-Dot Cellular Automata. (2014)

Perri, S., Corsonello, P., Cocorullo, G.: Design of efficient binary comparators in quantum-dot cellular automata. IEEE Trans. Nanotechnol. 13(2), 192–202 (2014)

Hayati, M., Rezaei, A.: Design and optimization of full comparator based on quantum-dot cellular automata. ETRI J. 34(2), 284–287 (2012)

Rashidi, H., Rezai, A., Soltany, S.: High-performance multiplexer architecture for quantum-dot cellular automata. J. Comput. Electron. 15(3), 968–981 (2016)

Rashidi, H., Rezai, A.: Design of Novel Efficient Multiplexer Architecture for quantum-dot cellular automata. J. Nano Electron. Phys. 9(1), 1012–1011 (2017)

Waje, M.G., Dakhole, P.: Analysis of various approaches used for the implementation of QCA based full adder circuit. In: Electrical, Electronics, and Optimization Techniques (ICEEOT), International Conference on 2016, pp. 2424–2428. IEEE (2016)

Singh, G.: Design and performance analysis of a new efficient coplanar quantum-dot cellular automata adder. Indian Journal of Pure & Applied Physics (IJPAP). 55(2), 97–103 (2017)

Abedi, D., Jaberipur, G., Sangsefidi, M.: Coplanar full adder in quantum-dot cellular automata via clock-zone-based crossover. IEEE Trans. Nanotechnol. 14(3), 497–504 (2015)

Ramesh, B., Rani, M.A.: Design of an Optimal Decimal Adder in quantum dot cellular automata. Int. J. Nanotechnol. Appl. 11(2), 197–211 (2017)

Mokhtari, D., Rezai, A., Rashidi, H., Rabiei, F., Emadi, S., Karimi, A.: Design of novel efficient full adder architecture for quantum-dot cellular automata technology. Facta Univ. Ser. Electron. Energ. 31(2), 279–285 (2018)

Rashidi, H., Rezai, A.: High-performance full adder architecture in quantum-dot cellular automata. J. Eng. 2017(7), 394–402 (2017)

Sen, B., Sahu, Y., Mukherjee, R., Nath, R.K., Sikdar, B.K.: On the reliability of majority logic structure in quantum-dot cellular automata. Microelectron. J. 47, 7–18 (2016)

Kianpour, M., Sabbaghi-Nadooshan, R., Navi, K.: A novel design of 8-bit adder/subtractor by quantum-dot cellular automata. J. Comput. Syst. Sci. 80(7), 1404–1414 (2014)

Mostafaee, A., Rezaei, A., Karkhanehchi, M.M., Jamshidi, S.M.: Design of QCA full adders without wire crossing. Boson J. Modern Phys. 2(2), 90–96 (2015)

Sonare, N., Meena, S.: A robust design of coplanar full adder and 4-bit Ripple Carry adder using qunatum-dot cellular automata. In: Recent Trends in Electronics, Information & Communication Technology (RTEICT), IEEE International Conference on 2016, pp. 1860–1863. IEEE (2016)

Pudi, V., Sridharan, K.: Low complexity design of ripple carry and Brent–kung adders in QCA. IEEE Trans. Nanotechnol. 11(1), 105–119 (2012)

Mohammadi, M., Mohammadi, M., Gorgin, S.: An efficient design of full adder in quantum-dot cellular automata (QCA) technology. Microelectron. J. 50, 35–43 (2016)

Bishnoi, B., Giridhar, M., Ghosh, B., Nagaraju, M.: Ripple carry adder using five input majority gates. In: Electron Devices and Solid State Circuit (EDSSC), 2012 IEEE International Conference on 2012, pp. 1–4. IEEE (2012)

De, D., Das, J.C.: Design of novel carry save adder using quantum dot-cellular automata. J. Comput. Sci. 22, 54–68 (2017)

Hashemi, S., Navi, K.: A novel robust QCA full-adder. Proc. Mater. Sci. 11, 376–380 (2015)

Jaiswal, R., Sasamal, T.N.: Efficient design of full adder and subtractor using 5-input majority gate in QCA. In: Contemporary Computing (IC3), 2017 Tenth International Conference on 2017, pp. 1–6. IEEE (2017)

Kassa, S.R., Nagaria, R.: A novel design of quantum dot cellular automata 5-input majority gate with some physical proofs. J. Comput. Electron. 15(1), 324–334 (2016)

Labrado, C., Thapliyal, H.: Design of adder and subtractor circuits in majority logic-based field-coupled QCA nanocomputing. Electron. Lett. 52(6), 464–466 (2016)

Sasamal, T.N., Singh, A.K., Mohan, A.: An optimal design of full adder based on 5-input majority gate in coplanar quantum-dot cellular automata. Optik-Int. J. Light Electron Opt. 127(20), 8576–8591 (2016)

Sasamal, T.N., Singh, A.K., Mohan, A.: An efficient design of quantum-dot cellular automata based 5-input majority gate with power analysis. Microprocess. Microsyst. (2018)

Hashemi, S., Tehrani, M., Navi, K.: An efficient quantum-dot cellular automata full-adder. Sci. Res. Essays. 7(2), 177–189 (2012)

Navi, K., Sayedsalehi, S., Farazkish, R., Azghadi, M.R.: Five-input majority gate, a new device for quantum-dot cellular automata. J. Comput. Theor. Nanosci. 7(8), 1546–1553 (2010)

Roohi, A., Khademolhosseini, H., Sayedsalehi, S., Navi, K.: A symmetric quantum-dot cellular automata design for 5-input majority gate. J. Comput. Electron. 13(3), 701–708 (2014)

Sen, B., Rajoria, A., Sikdar, B.K.: Design of efficient full adder in quantum-dot cellular automata. Sci. World J. 2013, 250802 (2013)

Seyedi, S., Navimipour, N.J.: An optimized design of full adder based on nanoscale quantum-dot cellular automata. Optik-Int. J. Light Electron Opt. 158, 243–256 (2018)

Ahmad, F., Bhat, G.M., Khademolhosseini, H., Azimi, S., Angizi, S., Navi, K.: Towards single layer quantum-dot cellular automata adders based on explicit interaction of cells. J. Comput. Sci. 16, 8–15 (2016)

Goswami, M., Mohit, K., Sen, B.: Cost effective realization of XOR logic in QCA. In: Embedded Computing and System Design (ISED), 2017 7th International Symposium on 2017, pp. 1–5. IEEE (2017)

Balali, M., Rezai, A.: Design of low-complexity and high-speed coplanar four-bit ripple carry adder in QCA technology. Int. J. Theor. Phys. 57(7), 1948–1960 (2018)

Safoev, N., Jeon, J.-C.: Full adder based on quantum-dot cellular automata. In proc. Manila Int. Conf. Trends Eng. Technol. (MTET-17), 83–86 (2017)

Safoev, N., Jeon, J.-C.: Compact RCA based on multilayer quantum-dot cellular automata. In: Information Systems Design and Intelligent Applications. pp. 515–524. Springer (2018)

Walus, K., Dysart, T.J., Jullien, G.A., Budiman, R.A.: QCADesigner: a rapid design and simulation tool for quantum-dot cellular automata. IEEE Trans. Nanotechnol. 3(1), 26–31 (2004)

Lent, C.S., Tougaw, P.D., Porod, W., Bernstein, G.H.: Quantum cellular automata. Nanotechnology. 4(1), 49 (1993)

Niknezhad Divshali, M., Rezai, A., Karimi, A.: Towards multilayer QCA SISO shift register based on efficient D-FF circuits. Int. J. Theor. Phys. 57(11), 3326–3339 (2018)

Lent, C.S., Tougaw, P.D.: A device architecture for computing with quantum dots. Proc. IEEE. 85(4), 541–557 (1997)

Pudi, V., Sridharan, K.: Efficient design of a hybrid adder in quantum-dot cellular automata. IEEE trans. Very Large Scale Integ. (VLSI) Syst. 19(9), 1535–1548 (2011)

Hanninen, I., Takala, J.: Robust adders based on quantum-dot cellular automata. In: Application-specific Systems, Architectures and Processors, 2007. ASAP. IEEE International Conf. on 2007, pp. 391–396. IEEE (2017)

Roohi, A., DeMara, R.F., Khoshavi, N.: Design and evaluation of an ultra-area-efficient fault-tolerant QCA full adder. Microelectron. J. 46(6), 531–542 (2015)

Arani, I.E., Rezai, A.: Novel circuit design of serial–parallel multiplier in quantum-dot cellular automata technology. J. Comput. Electron. 1–9 (2018)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Adelnia, Y., Rezai, A. A Novel Adder Circuit Design in Quantum-Dot Cellular Automata Technology. Int J Theor Phys 58, 184–200 (2019). https://doi.org/10.1007/s10773-018-3922-0

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10773-018-3922-0