Abstract

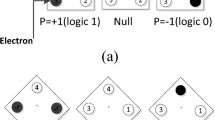

The quantum-dot cellular automata (QCA) can be replaced to overcome the limitation of CMOS technology. An arithmetic logic unit (ALU) is a basic structure of any computer devices. In this paper, design of improved single-bit arithmetic logic unit in quantum dot cellular automata is presented. The proposed structure for ALU has AND, OR, XOR and ADD operations. A unique 2:1 multiplexer, an ultra-efficient two-input XOR and a low complexity full adder are used in the proposed structure. Also, an extended design of this structure is provided for two-bit ALU in this paper. The proposed structure of ALU is simulated by QCADesigner and simulation result is evaluated. Evaluation results show that the proposed design has best performance in terms of area, complexity and delay compared to the previous designs.

Similar content being viewed by others

References

Sen, B., et al.: On the reliability of majority logic structure in quantum-dot cellular automata. Microelectron. J. 47, 7–18 (2016)

Wilson, M., et al.: Nanotechnology: basic science and emerging technologies. CRC Press, Boca Raton (2002)

Gargini, P.: The international technology roadmap for semiconductors (ITRS): “Past, present and future”. In: GaAs IC Symposium, 2000. 22nd Annual. IEEE (2000)

Mohammadi, M., Mohammadi, M., Gorgin, S.: An efficient design of full adder in quantum-dot cellular automata (QCA) technology. Microelectron. J. 50, 35–43 (2016)

Tougaw, P.D., Lent, C.S.: Logical devices implemented using quantum cellular automata. J. Appl. Phys. 75(3), 1818–1825 (1994)

Kumar, D., Mitra, D.: Design of a practical fault-tolerant adder in QCA. Microelectron. J. 53, 90–104 (2016)

Kyosun, K., Kaijie, W., Karri, R.: Quantum-dot cellular automata design guideline. IEICE Trans. Fundam. Electron. Commun. Comput. Sci. 89(6), 1607–1614 (2006)

Abutaleb, M.: Robust and efficient quantum-dot cellular automata synchronous counters. Microelectron. J. 61, 6–14 (2017)

Krause, P.G., et al.: An alternative geometry for quantum cellular automata. VLSI Des. 8(1–4), 549–553 (1998)

Abedi, D., Jaberipur, G., Sangsefidi, M.: Coplanar full adder in quantum-dot cellular automata via clock-zone-based crossover. IEEE Trans. Nanotechnol. 14(3), 497–504 (2015)

Goswami, M., et al.: Design of testable adder in quantum-dot cellular automata with fault secure logic. Microelectron. J. 60, 1–12 (2017)

Pandey, R.: Design and implementation of 16-bit arithmetic logic unit using quantum dot cellular automata (QCA) technique. Int. J. Eng. Res. Appl. 1(4), 10–16 (2014)

Sen, B., et al.: Design of fault tolerant reversible arithmetic logic unit in QCA. In: International Symposium on Electronic System Design (ISED). IEEE (2012)

Liu, W., et al.: A first step toward cost functions for quantum-dot cellular automata designs. IEEE Trans. Nanotechnol. 13(3), 476–487 (2014)

Ganesh, E.: Implementation and simulation of arithmetic logic unit, shifter and multiplier in Quantum cellular automata technology. Int. J. Comput. Sci. Eng. 2(5), 2010 (1824)

Waje, M.G., Dakhole, P.: Design and implementation of 4-bit arithmetic logic unit using Quantum Dot Cellular Automata. In: 2013 IEEE 3rd International Advance Computing Conference (IACC). IEEE (2013)

Sen, B., et al.: Realizing reversible computing in QCA framework resulting in efficient design of testable ALU. ACM J. Emerg. Technol. Comput. Syst. (JETC) 1(2), 30 (2014)

Gupta, N., Choudhary, K., Katiyal, S.: Two Bit Arithmetic Logic Unit (ALU) in QCA. Int. J. Recent Trends Eng. Technol. 8(2), 35 (2013)

Asfestani, M.N., Heikalabad, S.R.: A unique structure for the multiplexer in quantum-dot cellular automata to create a revolution in design of nanostructures. Phys. B Condens. Matter 512, 91–99 (2017)

Chabi, A.M., et al.: Towards ultra-efficient QCA reversible circuits. Microprocess. Microsyst. 49, 127–138 (2017)

Ahmad, F., et al.: Towards single layer quantum-dot cellular automata adders based on explicit interaction of cells. J. Comput. Sci. 16, 8–15 (2016)

Roohi, A., DeMara, R.F., Khoshavi, N.: Design and evaluation of an ultra-area-efficient fault-tolerant QCA full adder. Microelectron. J. 46(6), 531–542 (2015)

Walus, K., et al.: QCADesigner: a rapid design and simulation tool for quantum-dot cellular automata. IEEE Trans. Nanotechnol. 3(1), 26–31 (2004)

Heikalabad, S.R., Navin, A.H., Hosseinzadeh, M.: Midpoint memory: a special memory structure for data-oriented models implementation. J. Circ. Syst. Comput. 24(5) (2015)

Heikalabad, S.R., Navin, A.H., Hosseinzadeh, M.: Content addressable memory cell in quantum-dot cellular automata. Microelectron. Eng. 163, 140–150 (2016)

Karkaj, E.T., Heikalabad, S.R.: Binary to gray and gray to binary converter in quantum-dot cellular automata. Opt. - Int. J. Light Electron Opt. 130 (2017). https://doi.org/10.1016/j.ijleo.2016.11.087

Karkaj, E.T., Heikalabad, S.R.: A testable parity conservative gate in quantum-dot cellular automata. Superlattices Microstruct (2016). https://doi.org/10.1016/j.spmi.2016.08.054

Asfestani, M.N., Heikalabad, S.R.: A novel multiplexer-based structure for random access memory cell in quantum-dot cellular automata. Phys. B Condens. Matter 521, 162–167 (2017)

Gadim, M. R., Navimipour, N. J.: A new three-level fault tolerance arithmetic and logic unit based on quantum dot cellular automata. Microsyst. Technol (2017). https://doi.org/10.1007/s00542-017-3502-x

Heikalabad, S.R., Asfestani, M.N., Hosseinzadeh, M.: A full adder structure without cross-wiring in quantum-dot cellular automata with energy dissipation analysis. J. Supercomput (2017). https://doi.org/10.1007/s11227-017-2206-4

Barughi, Y.Z., Heikalabad, S.R.: A three-layer full adder/subtractor structure in quantum-dot cellular automata. Int. J. Theor. Phys. 56, 2848 (2017). https://doi.org/10.1007/s10773-017-3453-0

Rad, S.K., Heikalabad, S.R.: Reversible flip-flops in quantum-dot cellular automata. Int. J. Theor. Phys. 56, 2990 (2017). https://doi.org/10.1007/s10773-017-3466-8

Hosseinzadeh, H., Heikalabad, S.R.: A novel fault tolerant majority gate in quantum-dot cellular automata to create a revolution in design of fault tolerant nanostructures, with physical verification. Microelectron. Eng. 192, 52–60 (2018). https://doi.org/10.1016/j.mee.2018.01.019

Sadoghifar, A., Heikalabad, S.R.: A Content-Addressable Memory structure using quantum cells in nanotechnology with energy dissipation analysis. Phys. B Condens. Matter 537, 202–206 (2018). https://doi.org/10.1016/j.physb.2018.02.024

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Heikalabad, S.R., Gadim, M.R. Design of Improved Arithmetic Logic Unit in Quantum-Dot Cellular Automata. Int J Theor Phys 57, 1733–1747 (2018). https://doi.org/10.1007/s10773-018-3699-1

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10773-018-3699-1