Abstract

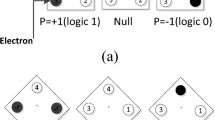

The quantum-dot cellular automata (QCA) is a novel technology with greater potential to provide circuits with small size and high speed compared with complementary metal–oxide–semiconductor (CMOS) technology. This paper presents and evaluates a novel serial–parallel QCA multiplier circuit based on a designed efficient full-adder circuit. The designed circuits are simulated using QCADesigner version 2.0.3. The results demonstrate that the proposed circuits have advantages in comparison with other QCA circuits in terms of cell count, area, and cost.

Similar content being viewed by others

References

Rairigh, D.: Limits of CMOS Technology Scaling and Technologies Beyond-CMOS. Institute of Electrical and Electronics Engineers, Inc, Piscataway (2005)

Shafizadeh, M., Rezai, A.: Improved device performance in a CNTFET using La2O3 high-κ dielectrics. J. Comput. Electron. 16(2), 221–227 (2017)

Karimi, A., Rezai, A.: A design methodology to optimize the device performance in CNTFET. ECS J. Solid State Sci. Technol. 6(8), M97–M102 (2017)

Zareiee, M., Mehrad, M.: A reliable nano device with appropriate performance in high temperatures. ECS J. Solid State Sci. Technol. 6(4), M50–M54 (2017)

Zareiee, M.: Modifying buried layers in nano-MOSFET for achieving reliable electrical characteristics. ECS J. Solid State Sci. Technol. 5(10), M113–M117 (2016)

Zareiee, M.: High performance nano device with reduced short channel effects in high temperature applications. ECS J. Solid State Sci. Technol. 6(7), M75–M78 (2017)

Mehrad, M.: Reducing floating body and short channel effects in nano scale transistor: inserted P+ region SOI-MOSFET. ECS J. Solid State Sci. Technol. 5(9), M88–M92 (2016)

Kummamuru, R.K., Orlov, A.O., Ramasubramaniam, R., Lent, C.S., Bernstein, G.H., Snider, G.L.: Operation of a quantum-dot cellular automata (QCA) shift register and analysis of errors. IEEE Trans. Electron Devices 50(9), 1906–1913 (2003)

Sen, B., Dutta, M., Mukherjee, R., Nath, R.K., Sinha, A.P., Sikdar, B.K.: Towards the design of hybrid QCA tiles targeting high fault tolerance. J. Comput. Electron. 15(2), 429–445 (2016)

Rashidi, H., Rezai, A., Soltany, S.: High-performance multiplexer architecture for quantum-dot cellular automata. J. Comput. Electron. 15(3), 968–981 (2016)

Rashidi, H., Rezai, A.: Design of novel efficient multiplexer architecture for quantum-dot cellular automata. J. Nano Electron. Phys. 9(1), 1011–1012 (2017)

Porod, W.: Quantum-dot devices and quantum-dot cellular automata. J. Frankl. Inst. 334(5–6), 1147–1175 (1997)

Balali, M., Rezai, A., Balali, H., Rabiei, F., Emadi, S.: A novel design of 5-input majority gate in quantum-dot cellular automata technology. In: 2017 IEEE Symposium on Computer Applications & Industrial Electronics (ISCAIE), pp. 13–16. IEEE (2017)

Cho, H., Swartzlander, E.E.: Adder designs and analyses for quantum-dot cellular automata. IEEE Trans. Nanotechnol. 6(3), 374–383 (2007)

Pudi, V., Sridharan, K.: Efficient design of a hybrid adder in quantum-dot cellular automata. IEEE Trans. Very Large Scale Integr. VLSI Syst. 19(9), 1535–1548 (2011)

Cho, H., Swartzlander, E.E.: Modular design of conditional sum adders using quantum-dot cellular automata. In: Sixth IEEE Conference on Nanotechnology, 2006. IEEE-NANO 2006, pp. 363–366. IEEE (2006)

Cho, H., Swartzlander, E.: Pipelined carry lookahead adder design in quantum-dot cellular automata. In: Conference Record of the Thirty-Ninth Asilomar Conference on Signals, Systems and Computers, pp. 1191–1195. IEEE (2005)

Rashidi, H., Rezai, A.: High-performance full adder architecture in quantum-dot cellular automata. J. Eng. 2017(7), 394–402 (2017)

Balali, M., Rezai, A., Balali, H., Rabiei, F., Emadi, S.: Towards coplanar quantum-dot cellular automata adders based on efficient three-input XOR gate. Results Phys. 7, 1389–1395 (2017)

Mokhtari, D., Rezai, A., Rashidi, H., Rabiei, F., Emadi, S., Karimi, A.: Design of novel efficient full adder architecture for quantum-dot cellular automata technology. Facta Univ. Ser. Electron. Energ. 31(2), 279–285 (2018)

Sen, B., Goswami, M., Mazumdar, S., Sikdar, B.K.: Towards modular design of reliable quantum-dot cellular automata logic circuit using multiplexers. Comput. Electr. Eng. 45, 42–54 (2015)

Cocorullo, G., Corsonello, P., Frustaci, F., Perri, S.: Design of efficient QCA multiplexers. Int. J. Circuit Theory Appl. 44(3), 602–615 (2016)

Cho, H., Swartzlander Jr., E.E.: Adder and multiplier design in quantum-dot cellular automata. IEEE Trans. Comput. 58(6), 721–727 (2009)

Abedi, D., Jaberipur, G.: Coplanar QCA serial adder and multiplier via clock-zone based crossover. In: 2015 18th CSI International Symposium on Computer Architecture and Digital Systems (CADS), pp. 1–4. IEEE (2015)

Pudi, V., Sridharan, K.: Efficient design of Baugh-Wooley multiplier in quantum-dot cellular automata. In: 2013 13th IEEE Conference on Nanotechnology (IEEE-NANO), pp. 702–706. IEEE (2013)

Kim, S.-W., Swartzlander, E.E.: Parallel multipliers for quantum-dot cellular automata. In: Nanotechnology Materials and Devices Conference, 2009. NMDC’09, pp. 68–72. IEEE (2009)

Chudasama, A., Sasamal, T.N.: Implementation of 4 × 4 vedic multiplier using carry save adder in quantum-dot cellular automata. In: 2016 International Conference on Communication and Signal Processing (ICCSP), pp. 1260–1264. IEEE (2016)

Ahmad, F., Bhat, G.M., Khademolhosseini, H., Azimi, S., Angizi, S., Navi, K.: Towards single layer quantum-dot cellular automata adders based on explicit interaction of cells. J. Comput. Sci. 16, 8–15 (2016)

Tougaw, P.D., Lent, C.S.: Dynamic behavior of quantum cellular automata. J. Appl. Phys. 80(8), 4722–4736 (1996)

Vankamamidi, V., Ottavi, M., Lombardi, F.: Two-dimensional schemes for clocking/timing of QCA circuits. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 27(1), 34–44 (2008)

Kim, K., Wu, K., Karri, R.: The robust QCA adder designs using composable QCA building blocks. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 26(1), 176–183 (2007)

Angizi, S., Alkaldy, E., Bagherzadeh, N., Navi, K.: Novel robust single layer wire crossing approach for exclusive or sum of products logic design with quantum-dot cellular automata. J. Low Power Electron. 10(2), 259–271 (2014)

Abedi, D., Jaberipur, G., Sangsefidi, M.: Coplanar full adder in quantum-dot cellular automata via clock-zone-based crossover. IEEE Trans. Nanotechnol. 14(3), 497–504 (2015)

Sasamal, T.N., Singh, A.K., Mohan, A.: An optimal design of full adder based on 5-input majority gate in coplanar quantum-dot cellular automata. Opt. Int. J. Light Electron Opt. 127(20), 8576–8591 (2016)

Kassa, S.R., Nagaria, R.: A novel design of quantum dot cellular automata 5-input majority gate with some physical proofs. J. Comput. Electron. 15(1), 324–334 (2016)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Edrisi Arani, I., Rezai, A. Novel circuit design of serial–parallel multiplier in quantum-dot cellular automata technology. J Comput Electron 17, 1771–1779 (2018). https://doi.org/10.1007/s10825-018-1220-y

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-018-1220-y