Abstract

In this paper the design of power management integrated circuits for the energy harvesting of ultrasound waves in implanted biomedical devices is addressed. In particular, the paper focuses on the main building block of the power conversion stage which is represented by the AC/DC converter. After an in-depth analytical description of cross-coupled passive and active rectifiers, a detailed design procedure for the common-gate comparator is introduced. Then a comparison between the different discussed topologies is carried through simulation results using a 28-nm standard CMOS technology. The results provide useful design guidelines in choosing the best topology according to the design specifications.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

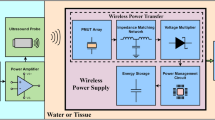

The relentless advancements in the technology fabrication of nanometer-scale active devices faced in the last decade have given birth to the rapid development of the paradigm of the Internet-of-Things (IoT) [1]. Among always-connected wireless sensors nodes (WSN), it is relevant to mention wireless body-area-networks (WBANs), intended as un-tethered wearable or implantable medical devices (IMDs) embedding sensors and actuators [2]. The increasing diffusion of IMDs is due to their ability to improve the accuracy of disease detection and improve the quality of life of patients. Indeed, the possibility to collect and communicate human-body data and parameters without the intervention of a conventional medical equipment revealed itself as the next-generation therapy for disease management and prevention [3,4,5,6,7,8,9]. On the other side, most of the commercial devices have the battery as the only energy source carrying out two main drawbacks: the first one, relieves on the invasiveness of bulky batteries for IMDs; the second one is related to the necessity of a medical surgery to replace the battery once discharged. Hence, the necessity of long-term living and energy-autonomous devices is arising.

A promising solution to such issue is provided by the energy harvesting, which allows an internal power generation that makes unnecessary the use of the batteries, thus reducing the overall volume and invasiveness of these devices. An external energy source coupled to the millimeter-sized energy harvester implanted inside the body is the most common solution adopted in literature. The external power can be provided through radio-frequency (RF), electromagnetic (EM) induction or Ultrasound (US) waves [10,11,12,13,14,15,16]. Among these power transfer systems, only US waves have the capacity of enabling simultaneous power and data transfer in deep-implanted (>2 cm) millimeter-sized devices, as shown in [7]. Moreover, US waves are not as susceptible to EM interference nor do they significantly affect the EM fields of the surroundings. Finally, US waves have smaller wavelengths in tissue (e.g., 1.5 mm at 1 MHz) and low tissue attenuation (0.5 dB/cm/MHz), thus allowing highly directive focusing down to millimeter spots at great depths and high acoustic-electrical efficiency with sub-millimeter-sized receivers [14, 17]. Furthermore, the possibility to provide to millimeter-sized deeply-implanted circuits a relevant power level (100 \(\mu\)W-1 mW) opens the road to medical applications as sensing, stimulation and drug-delivery [4, 12, 18, 19].

For the above-mentioned reasons, the main performance parameters of power management integrated circuits (PMICs) for IMDs are related to the area occupation, the available input power budget and the power conversion efficiency (PCE) of the PMIC. Under this scenario, in this paper we analyze the design of the main building block of the PMIC which is represented by the AC/DC converter [11,12,13, 17, 20,21,22,23,24]. The paper is structured as follows. The second section introduces the experimental characterization of the US-power link. Sections 3 and 4 discuss the passive and active rectification circuits, respectively. Section 5 a sizing procedure for common-gate comparators (CGCs), first introduced in [21], is discussed. Finally, in sect. 6 a comparison on passive and active rectifiers is carried out through simulations with a 28-nm Bulk CMOS technology provided by TMSC. Finally, in sect. 7 conclusion are drawn.

2 Experimental characterization of the US-power link

The system analyzed in this work comprises two piezoelectric devices. The first one is the power transmitting piezo (TX PIEZO) to be placed out of the body, while the second one (RX PIEZO) is implanted together with the entire IC and is responsible of the received power, as indicated in Fig. 1. The devices are selected among the ones commercially available, trying to carry out the best trade-off between dimensions, operating frequency and the transferred power. Thus, the operating frequency under resonance condition is selected for both piezoelectric devices equals to \(f_0\sim 2\) MHz and the thickness, t, of the receiving piezo is thus equal to about 0.4\(-\)0.5 mm.

In order to emulate the acoustic impedance of the tissues, oil or ballistic gel can be used. In particular, ballistic gel was investigated as a tissue-mimicking material in an anthropomorphic cardiac phantom for ultrasound imaging. The gel was tested for its acoustic properties and its compatibility with conventional plastics molding techniques [25]. Speed of sound and attenuation were evaluated in the range 2–12 MHz. The speed of sound was \(1537 \pm 39 \,\hbox {m/s}\), close to typical values for cardiac tissue (\(\sim 1576\, \hbox {m/s}\)). The attenuation coefficient was \(1.07 \,\hbox {dB/cm}\cdot \hbox {MHz}\), within the range of values previously reported for cardiac tissue (0.81\(-\)1.81 dB/cm\(\cdot\)MHz) [26].

Considering as a target application the power delivery to IMD in the cerebral cortex, the distance between the piezo devices should be in the order of d=1\(-\)1.5 cm. Therefore, both the devices are encapsulated in ballistic gel keeping such distance. Considering now the definition of wavelength as \(\lambda =v/f\), when \(f=f_0=2\,\hbox {MHz}\) and \(v\sim 1540\,\hbox {m/s}\), it follows \(\lambda =0.77\,\hbox {mm}\); it means that the distance \(d=1-1.5\,\hbox {cm}\) is quite large compared to the US-wavelength in tissues, so the waves propagates in far-field region.

Indeed, the ultrasonic near-field area can be calculated by the following equation [9]:

where D is the diameter of the material and A its area (as for now assumed lower than \(9\,\hbox {mm}^2\)), while \(\lambda\) is the US-wavelength in tissues. As for the materials selection, the TX-PIEZO is the PRY+0111 provided by PI Ceramics. It is made up by a disk of PIC255 with a diameter equal to 8 mm, with a radial resonant frequency equals to 250 kHz and the electrical resonance frequency equals to 2 MHz. As for the RX-PIEZO, it is the 000,065,944 provided by the same PI Ceramics. It is a thin layer of PIC255, with square area equals to \(9\,\hbox {mm}^2\) and thickness, \(t=0.5\,\hbox {mm}\); its radial resonance frequency is placed at 500 kHz while its electrical resonant frequency is about 2 MHz.

The values of the components of the Butterworth Van Dyke (BVD) equivalent model of the piezo devices in Fig. 2b were carried out using a VNA (E5061B provided by Keysight Technologies). Furthermore, resonance doublets were depicted by using two parallel RLC series circuits, although the electrical resonance frequency is given by one of them (as indicated in grey box in Fig. 2b).

As it can be observed in Fig. 2c, the Thévenin equivalent model deals with the concept of resonance for RLC series circuit; indeed, the piezo devices, under the electrical resonance condition, exhibit a finite impedance (in the order of magnitude of 0.1–1 k\(\Omega\)), as also shown in Figs. 3 and 4, where \(R_{PZT}\) is almost equal to 500 \(\Omega\) and 100 \(\Omega\) for RX-piezo and TX-piezo, respectively. Moreover, both the devices have been characterized once packed in the ballistic gel, as in Figs. 5 and 6, and both of them present an electric resonance frequency \(f_1\sim 2\,\hbox {MHz}\). The electrical behaviour of the device in the nearby of this frequency is capacitive, since the current leads the voltage. The extracted BVD model parameters for the TX- and RX-PZT are summarized in Tables 1 and 2, respectively. Moreover, Table 3 reports the measured received power levels for the RX-PZT modeled with Thévenin equivalent circuit, with \(R_{PZT}=1\,\hbox {k}\Omega\). The TX-PZT was stimulated with a sine wave with an amplitude of \(20\,V_{pp}\) and both piezo are taken under electrical resonance condition with \(f_0=2\,\hbox {MHz}\).

TX-PZT and RX-PZT encapsulated in ballistic gel at a distance of about 1.0 cm [25]

RX-PZT device compared to a 10 cents coin. The overall dimensions, including the two-layers PCB, are lower than the showed coin [25]

3 Cross-coupled rectifier

The Cross-Coupled (CC) rectifier is among the most used passive rectifier. It is made up by two cross-connected CMOS inverters, in which the inputs and the outputs are represented by \(V_{AC1,2}\) as reported in Fig. 7a. Assuming that \(V_{tn}\) and \(V_{tp}\) are the threshold voltages of NMOS and PMOS transistors, respectively, the working principle is then summarized. When \(V_{AC2}>V_{tn}\), M1 is on (M2 off) and, in the meanwhile, if \(V_{AC1}<V_{tp}\), M3 is on (M4 is off), as ideal switches reported in Fig. 7b. The circuit establishes a conductive path to the load capacitance thanks to PMOS transistors, M2 and M3. Indeed, M2 shorts \(V_{DC}\) to \(V_{AC1}\) and M3 shorts the same DC output voltage to \(V_{AC2}\). On the other side, the NMOS transistors short the input voltages to ground. Moreover, assuming that \(V_{DC}\) has already reached a steady-state condition, all the transistors work in triode region.

As regards the maximum achievable DC output voltage value, it is given by the forward voltage drop of the drain-bulk P+/Nwell junction in PMOS transistors, also shown in Fig. 7b as anti-parallel diodes. Indeed, supposing that the system is in the start-up phase (i.e., \(V_{DC}=0\) V) and the load capacitor is charging up. If \(V_{AC2}>0\) and \(V_{AC1}<0\), the PMOS transistor M3 has its source and its bulk voltages \(V_{S3}=V_{B3}=V_{DC}=V_{AC2}\), while the drain voltage is equal to \(V_{D3}=V_{AC1}\). If, now, \(V_{DB3}\) overcomes the forward voltage of the same drain-bulk junction (\(V_{j,DB}\sim 0.7\) V), the parasitic diode is forward biased and it will work as a clamping diode on the negative phases of the AC input voltages. This undesired effect carries out a current leakage that is given by the current equation for the diode

From the previous reasons, it is possible to understand that the maximum DC output voltage from the CC rectifier will be about \(V_{DC}\approx 700\,\hbox {mV}\) when the current passing in the circuit is in the order of magnitude of hundreds of \(\mu \hbox {A}\) up to mA.

Furthermore, it is possible to size the transistors of the topology represented in Fig. 7a to reduce as maximum as possible their on-resistance. In particular, assuming that the lower voltage between \(V_{AC1}\) and \(V_{AC2}\) are nearby zero and that all the active components of the same type have aspect ratios equal to \(\left( \frac{W}{L}\right) _N=\frac{240\,\mu m}{0.15\,\mu m}\) and \(\left( \frac{W}{L}\right) _P=\frac{3\cdot 240\,\mu m}{0.15\,\mu m}\), on-state resistances can be found as

Suppose, now, that \(V_{DC}=(V_P-V_D)-(V_R/2)\), where \(V_P\) is the peak valueFootnote 1 of the input voltage, \(V_{AC}\), \(V_D\) is the voltage drop across transistors and \(V_R\) is the ripple that depends on both \(C_L\) and \(R_L\). Starting from it, the DC output voltage can be also expressed as follows from [27]

because of \(V_R=(V_P-V_D)/(2f_0C_LR_L)\). Moreover, \(R_{ON}=R_{ON,NMOS}+R_{ON,PMOS}\), found out in Eq. (4), since the input current simultaneously passes through both transistors. If \(R_L\gg R_{ON}\), we can neglect the on-state resistance in (5). Moreover, also \(V_D\approx 0\) simplifying the (5) as below

The Fig. 8 and 9 represent the transient analysis of signals for the CC rectifier when a \(V_{AC}=1.8\,\hbox {V}\) and a \(V_{AC}=0.6\,\hbox {V}\) has been applied to circuit using a Norton equivalent source. A sine current with frequency \(f_0=2\,\hbox {MHz}\) and amplitude \(I_{source}=1\,\hbox {mA}\) together with a parallel resistance \(R_S=1.8\,\hbox {k}\Omega\) and, for the second case, \(R_S=600\,\Omega\) was used for the simulation. The load is represented by a resistance \(R_L=10\,\hbox {k}\Omega\) and the capacitor \(C_L=1\,\hbox {nF}\). Parasitic components associated to the load capacitor as the equivalent series resistance, \(\hbox {ESR}=50\,\hbox {m}\Omega\) and equivalent series inductance \(\hbox {ESL}=1\,\hbox {nH}\) were used for this simulation.

The following considerations were carried out:

-

Signals \(V_{AC1}\) and \(V_{AC2}\) present their lower value equal to 0 V due to the short-circuit connection to ground by means of NMOS transistors used as switches;

-

Both positive and negative phases of \(V_{AC}\) were clamped at about \(V_{j,DB}\sim 0.7\,\hbox {V}\) giving a DC output voltage equal to \(V_{DC}\sim 0.7\,\hbox {V}\) in Figs. 8 while in 9 this does not occurFootnote 2. This undesired clamping effect reduces the power conversion efficiency, due to a higher value of leakage current;

-

There is a current passing in the drain-bulk junctions that is quite high (Fig. 8); as said, the drain-bulk junctions work as anti-parallel diode when the current could not pass through PMOS transistors. This condition is related to their gate voltages; indeed, while \(V_{AC2}\) increases turning off M2, \(V_{AC1}\) has not already reached the lower value, so neither between M2 and M3 can conduct the current that is coming out from the source. This current will pass through the junction diode indicated in Fig. 7b. This issue does not arise when the input AC voltage is quite low as depicted in Fig. 9, due to \(V_{AC1,2}\) values lower than PMOS threshold voltages. It is worth noting that this currents through the junctions of PMOS transistors does not lead to a huge leakage as the one seen with the clamping effect depicted above. The positive currents are counterbalanced by negative peaking current passing through the opposite transistor’s drain-bulk junction (M3 in the case presented in Fig. 8 with \(V_{AC1}\) that goes down and \(V_{AC2}\) that goes up).

4 Active rectifiers

Active rectifiers present almost the same structure of passive full-wave rectifiers but they exploit the properties of active diodes. Indeed, for those applications in which the power level rises up to hundreds of \(\mu\)W, the passive solutions presented before could be extremely inefficient. Active diodes, on the other side, are essentially comparator-controlled MOSFETs used to replace passive diodes (or diode-connected MOSFETs) in passive rectifiers topologies. They have a lower forward voltage drop compared to passive ones and this implies lower losses. Moreover, although an active rectifier should embed other sub-circuits (i.e., comparators, drivers, biasing circuits...) they could be entirely integrated reducing the number of discrete components and the overall cost of the system.

Figure 10c) indicates the most important sub-blocks of an active rectifier and it comprises two comparators (COMP1,2), two buffers (BUFF1,2) and a core rectifier (CR) circuit. In particular this last one is made up by two upside PMOS transistors \(M_{P1,2}\); indeed, during the start-up of the circuit they allow to charge up the load capacitor, \(C_L\), thanks to the negative phases of input AC voltages indicated as \(V_{AC1,2}\). This process makes the output DC voltage, \(V_{DC}\), to increase until it reaches about the NMOS transistors’ threshold voltages, \(V_{tn}\), enabling the active diodes, \(M_{N1,2}\), or, as usual defined, NMOS power switches.

Their working principle is here summarized and explained thanks the use of the transient simulation results shown in Figs. 11 and 12. Let us assume that \(V_{AC1}\) goes down while \(V_{AC2}\) goes up. The comparator COMP1 produces a high output voltage, turning on the power NMOS switch \(M_{N1}\) which short-circuits the drain voltage, \(V_{AC1}\), to the ground. In the meanwhile, the PMOS transistor \(M_{P2}\) is turned on short-circuiting \(V_{DC}\) to \(V_{AC2}\) that is maintained high for ideally half a period of the input AC voltage. This condition is preserved until \(V_{SG2}=V_{AC2}-V_{AC1}>|V_{tp}|\). Once the previous condition is not verified anymore, the second rectification phase starts with \(V_{AC1}\) that swings above ground voltage and the \(M_{N1}\) that is turned off. During the next half of the AC input cycle, the other diagonal of the rectification circuit will conduct in a similar fashion as described above. Active rectifiers with power switches driven by comparators increases the output DC voltage value. Indeed, naming \(V_{\gamma }\) the switch threshold voltage, the forward voltage drop is reduced from \(2V_{\gamma }\) to \(2V_{DS}\), where this drain-source voltage is strictly linked to the on-resistance of the switches and, hence, it could be strongly reduced.

However, when operating at a high frequency, such as tens or hundreds of MHz, the comparator delay and the gate-drive buffer delay could adversely affect the switching operation, reducing the efficiency of the rectifier. In particular, an high reverse current (i.e, a current flowing from the output of the rectifier to, at the least, one of the inputs) will occur if the large power switches are not turned off immediately, when \(V_{AC1}\) or \(V_{AC2}\) is higher than the ground voltage. Now, in this architecture, the main losses include the conduction loss and the switching loss of the power transistors, and the static power loss of the comparator. In terms of power loss and PCE, the extra-loss caused by the reverse current is already included in the above-mentioned conduction loss, as the energy goes from the DC to the AC input is recycled. But in terms of energy extraction from the source, the reverse current obviously reduces the maximum power that can be extracted from the source. From both perspectives, the reverse current should be eliminated [22].

Being the active diode basic scheme consolidated, the differences in the active rectifier schemes mainly regard the implementation of the comparators, the compensation of the delay, in the case of high frequency operations (from tens up to hundreds of MHz) and the control of the reverse currents [28]. Some examples of comparators from the state-of-the-art will be presented in the following subsections and, finally, some strategies and techniques to increase the PCE will be also described starting from [20].

4.1 Energy harvesting source and clamping circuit

Regarding the US-Energy Source, the RX-PZT is supposed to work under the electrical resonance frequency conditions, so with a Thévenin equivalent model and a series resistance, \(R_{PZT}\in [1-2]\,k\Omega\) that better fits with the experimental measurements of input power levels reported in Tab. 3. In order to protect the active rectifier from any possible input over-voltage, a clamping circuit is often implemented and connected between the input pins and the input of the rectifier. As for this last block, it is based on 4 diode-connected PMOS transistors (with bulks short-circuited with their sources), with aspect ratio equals to \(\left( 20/1\right)\) and dimensions expressed in microns. It will serve as AC input voltage amplitude limiting system, cutting the edges of \(V_{AC}\) at about 1.7 V, being 1.8 V the maximum allowable voltage for the thick-oxide transistors of the adopted technology. It is important to notice that higher will be the received AC voltage level, higher will be the power consumption of the clamping circuit, thus reducing the overall PCE.(Tables 4, 5)

4.2 Active body biasing (ABB)

The CR of the solution taken as an example includes an Active Body-Biasing (ABB) circuit. This block was previously used in [28, 29]. In conventional body-bias structures of the DC powerless systems (rectifier is power supplied by AC power source), SBB (self-body-biasing) is a popular and simple solution to solve the bulk problems, indeed it is necessarily employed to ensure that the bulk voltage is always the highest in this system [10, 11, 30, 31]. The SBB was previously adopted for passive rectifier, while, in recent studies, it was also used for high efficiency active rectifiers. Nevertheless, this structure also couples the AC amplitude through the parasitic capacitance of the SBB transistors especially for frequency higher than 10 MHz (13.56 MHz, as presented in [29]), that makes the body voltage could be higher than the peak voltage of the input source (\(V_{AC1,2}\)). This undesired effect is in charge of a reduction of the overall PCE of the system; indeed, when the bulk voltage is quite higher than the source voltage, the body-effect arises increasing the threshold voltages of the cross-connected power PMOS transistors belonging to CR, thus reducing the maximum available current at the output. Moreover, by using the SBB, it is not ensured that the body potential will be lower than the maximum allowable for a given process [29]. In view of this, the proposed solution embeds an ABB structure to eliminate the body-effect on the power transistors. Moreover, the same body-biasing block will be used also for the CGC-DIP as shown in Figs. 10 and 14.

The proposed active-body-biasing (ABB) circuit is shown in Fig. 13a). Assume \(V_{AC1}\) is high and \(V_{AC2}\) is low, so that \(V_{AC2}\) turns on MB1 and MB3. The bulk voltage \(V_{BB}\) would given by the voltage divider between \(V_{AC1}\) and \(V_{DC}\). Thus, the coupled AC signal would be shared to \(V_{DC}\). This architecture ensures the body voltage slightly lower or equal than the input source, but still higher than the output voltage. Moreover, considering that all the transistors of this block will work in triode region, in order to reduce the leakage of current from \(V_{DC}\) to the bodies of \(M_{P1,2}\), the lengths of \(M_{B3,4}\) are doubled.

4.3 Common-gate comparator with push-pull differential-input (CGC-DIP)

Differently from [24], the proposed CGC shown in Fig. 14 presents a body-biasing input for all the PMOS transistors. The voltage \(V_{BB}\) is the output of the ABB block (Fig. 7) used in [20] and it serves to bias p-channel transistors’ bulks to the highest potential of the circuit without increasing their threshold voltages. As for the bias of COMP1, it is provided through transistors M1, M2 when \(V_{AC2}>0\), \(V_{AC1}<0\) (vice-versa for COMP2) and \(V_{DC}\) is higher than \(|V_{tp}|+V_{OV1,2}\) making them working in saturation region. When \(V_{AC1}\) (\(V_{AC2}\)) swings below 0 V, M5 provides a larger current than M6, while, as for M8 diode-connected transistor, its gate drops with \(V_{AC1}\) (\(V_{AC2}\)), and reduces \(V_{GS7}\). M5 biases the current mirror M3-M4, causing M4 to have a larger current than M7. Consequently, the output node is driven high, the signal level is restored by CMOS buffers, enabling transistor \(M_{N1} (M_{N2})\) turns on. It is important to notice that transistors M5 and M8 are built on a deep n-well in order to connect their source and their isolated bulk terminals to \(V_{AC1}\,(V_{AC2})\); in this, way the p-substrate of the entire silicon block is connected to the ground potential.

5 Common-gate comparator design strategy based on \(g_m/I_D\) parameter

The proposed procedure considers the maximization of the PCE of the rectifier (i.e., minimization of the static power consumption of the CGC) and maximization of the slew-rate (SR) of the CGC.

The CGC-DIP is designed to work in sub-threshold region, except for the biasing transistors M1-M2. It was used the equation for the transconductance under sub-threshold region as \(g_m=\frac{I_D}{nV_T}\), where \(I_{D}\) is the variable bias current depending on the source voltage, \(V_S\), \(n\in [1.3-1.5]\) is the sub-threshold slope and \(V_T\) is the thermal voltage, equals to 26 mV at room temperature. Furthermore, the lengths for all the transistors, except for M1-M2 that serve for current biasing, were fixed to \(L_{n,p}=0.6\,\mu m\); in this way, the channel length modulation coefficient is reduced by exploiting the following equation

where \({\epsilon _s}\) is the silicon electrical permittivity, the \(N_{AB}\) is the acceptor concentration of the p-bulk and \(\phi _F\) is the Fermi’s potential.Footnote 3 Then, the current-mirroring mismatch due to channel length modulation is, hence, reduced. In addition, the increment of the lengths of the transistors allows to minimize the process mismatch, especially on the transistors’ threshold voltages as indicated by Pelgrom et al. in [32] in 1989 and reported as follows

where \(\Delta V_{TH0}\) is the threshold mismatch between two adjacent transistors and \(A_{VTH0}\) is a constant that depends only on the process.

As for the optimization procedure based on \(g_m/I_D\) parameter shown in Fig. 15, it was reported for the first time in literature by Authors in [21]. It is resumed in the flow chart reported in Fig. 16. For the sake of conciseness, the procedure is reported for the comparator in Fig. 14, but it can be easily extended to any other comparator topology, since the methodology has a general validity and can be applied irrespectively of the specific adopted technology

-

1.

Use \(g_m/I_D\) curves in Fig. 15 to choose the largest, while robust, dynamic range for a given operating region for all the transistors, both NMOS and PMOS. Example: sub-treshold working region \(\rightarrow {{\overline{\Gamma }}}=\overline{(g_m/I_D)}=27\,V^{-1}\rightarrow V_{OV}\in [-150; -100]\,mV\);

-

2.

Evaluate the maximum allowed static power consumption for the comparator, \(I_{COMP}^{MAX}\), as a percentage of the minimum available AC current given by the source, \(I_{S}^{MIN}=min\,{|I_{AC}|}\) in Fig. 10. Example: \(I_{S}^{MIN}=750\,\mu A\) and \(I_{COMP}^{MAX}=2\%\,I_{S}^{MIN}=15\,\mu A\) \(\rightarrow I_{B}^{MAX}= 3.75\,\mu A\)Footnote 4;

-

3.

Find out the first aspect ratio step, \((W/L)_B^{(1)}\) for biasing transistor (M1-M2 in Fig. 14) taking into account the proper working regionFootnote 5 and the maximum supply voltage, \(V_{DC}^{MAX}\). Example: Let \(V_{DC}^{MAX}=1.8\,V\) and M1-M2 PMOS biasing transistors in saturation, leading thus \((W/L)_{1,2}^{(1)}\sim 0.06\);

-

4.

From the previous point, it is possible to find a first approximation of the dimensions of all the transistors in the circuit. The suggested value for \(\Gamma ^*=(g_m/I_D)^*\) is a fictitious one and slightly lower than the one selected previously. This value is found out considering that both the maximum bias current and the maximum rectified voltage giving, hence, a lower value of \(\Gamma\), as follows: \(\Gamma ^*=(g_m/I_D)^*={{\overline{\Gamma }}}-4\,V^{-1}=23\,V^{-1}\) giving, as an approximated result, \(\left( \frac{W}{L}\right) ^*_N=12\,,\,\,\left( \frac{W}{L}\right) ^*_P=24\);

-

5.

Given the size for all transistors, it is possible to value the order of magnitude of parasitic capacitances associated to a specific node. Example: for the node \(V_{COMP}\), in Fig. 14, the estimated capacitanceFootnote 6is \(C_{A}^*\sim C_{GD4,ov}+C_{GD7,ov}=C_{ox}L_{ov}(W_n^*+W_p^*)\simeq 6\,\textrm{fF}\);

-

6.

Use the previous approximated result for the capacitance \(C_{A}^*\) to evaluate the minimum bias current, \(I_{B}^{MIN}\) starting from the minimum acceptable slew-rate, \(SR_{min}\). This last value should be chosen accordingly to the period, \(T_0\), (in this design case \(T_0=500\,\hbox {ns}\)) of the power source for the circuit and the minimum output voltage variation of the comparator in Fig. 14 as \(\Delta V_{COMP}^{MIN}=V_{DC}^{MIN}\sim 0.6\,V\). This last is the minimum allowed supply voltage, \(V_{DC}^{MIN}\), to make the circuit to properly work in the desired operating region. Moreover, choose the rise (or fall) time for the same circuit node, as \(\Delta t_{rise,fall}\ll T_0/2\) (e.g. about the 10% of \(T_0/2\)), evaluate the SR and the minimum bias current as in the following example. Example: Let \(\Delta t_{rise,fall}=30\,\hbox {ns}\) and \(\Delta V_{COMP}^{MIN}=0.6\,\hbox {V}\), as worst-case condition. Then, \(SR_{min}= 20\,{V/\mu s}\rightarrow I_{B}^{MIN}\sim 120\,{nA}\).

-

7.

Use the result of the previous point to carry out the proper aspect ratio for the biasing transistors, M1-M2, using also the lowest acceptable value for the supply DC voltage. Example: Let \(V_{DC}^{MIN}=0.6\,V\) and M1-M2 PMOS biasing transistor in saturation \(\rightarrow (W/L)_{1,2}^{(2)}\sim 0.17\);

-

8.

Use now the minimum bias current and check the dimensions of the biasing transistor; find out the aspect rat tios of all the remaining circuit looking for the desired value of \(\overline{(g_m/I_D)}\) ratio with the help of the simulator \(\left( \frac{W}{L}\right) _N=\left( \frac{W}{L}\right) _P=16\).

Design procedure for CGC in a simplified flow-graph form [21]

6 Rectifiers performance comparison

The Active and Passive rectifiers presented so far are now compared from a performance parameters perspective. Indeed, since the US-energy harvesting sources can be applied in several IMDs scenarios, from deep-implanted to under-skin devices, with different power and AC input voltage ranges, the following comparison allows the readers to have an immediate insight on the topology to be chosen according to the input power specifications (16). The addressed passive rectifier is the CC solution while the active AC/DC converter is the presented one, with CGC-DIP sized adopting the design procedure of [21]. Regarding the US-power source, its amplitude will be varied, \(V_{PZT}\), taking into account the measured electrical quantities reported in Tab. 3 and the equivalent series Thévenin resistance is selected equal to \(R_{S}=1.0\, k\Omega\).

The comparison graphs focus on the rectified output voltage values, \(V_{DC}\), the output power \(P_{DC}\) and the PCE of the entire system, including the clamping circuit.

As it can be observed in Fig. 17, the maximum rectified voltage for CC-passive rectifier is about equal to 0.6\(-\)0.7 V, due to the forward biasing of parasitic drain-bulk junctions, regardless the load resistance value. On the other side, the rectified voltage of the proposed active AC/DC converter is strongly depending on the load resistance and, hence, on the output current. Nevertheless, \(V_{DC}\) is much higher than a pn junction potential in almost all the cases. Conceiving the output power and PCE parameters, they have been evaluated by using the following equation

From Figs. 18 and in 19 it can be noted that the CC seems to be the most efficient rectifier solution for lower input power range (in the order of magnitude of 10-\(300\,\mu \hbox {W}\)), while the active rectifier can be efficiently used for input power levels ranging in 0.1\(-\)1.0 mW. Indeed, while the former shows a maximum PCE around 90%, the latter present a maximum PCE around 95%. In both of this cases, the evaluation was executed on pre-layout and simulated in 28-nm technology provided by TSMC with Cadence Virtuoso simulation environment.

7 Conclusions

This work is focused on rectifiers for PMICs powered by US for battery-less IMDs. After a first experimental section made up by measurement on the US power link, passive (Cross-Coupled) and Active AC/DC converters have been presented. Both the solutions have been analyzed and simulated in a 28-nm Bulk CMOS technology carrying out a practical demonstration of the review on rectifiers in [20] and a general guideline for designers of PMIC in energy-autonomous devices. Indeed, the cross-coupled rectifier is widely used for its low-voltage and auto-switching characteristics. However, a high leakage current may occur if the input voltage, during the transition instants, is too high because the PMOS and NMOS will be turned on simultaneously short-circuiting the two supply rails. This rectifier operates efficiently with low input voltage (e.g.,from the threshold voltage of the active devices up to 1\(-\)1.5 V). In such case, reverse and short-circuit currents are extremely reduced, but the on-resistance is increased, making the rectifier useful for very-low power applications. Moreover, if the input voltage is larger than the threshold voltage of the transistors, the leakage currents become relevant and the efficiency decreases, but the channel becomes more conductive decreasing the on-resistance and enabling mW-power level operations. On the other side, the active rectifier better suits for higher voltage and power level, due to an overall higher PCE and an higher (although unregulated) rectified output voltage. In addition, a design procedure based on the \(g_m/I_D\) parameter for CGCs, first introduced in [21], is discussed to allow designers to have a better sizing procedure of these blocks in active AC/DC converters, thus, avoiding, the use of complex turn-on/off delay compensation sub-circuits. Following the proposed design strategy, the topology shown in Fig. 10 is currently being fabricated and experimental results will be available in the near future.

Notes

If \(V_{DB}>V_{j,DB}\) the peak voltage is assumed as the clamped value so \(V_P\approx 0.7\) V.

Note that the value of \(\sim 0.7\,\hbox {V}\) is evaluated according the adopted parameters; on other conditions, the cross-coupled topology can achieve \(V_{DC}\) values significantly higher than 0.7V.

Is used \(N_{AB}\) for n-type transistors built in p-substrate, while \(N_{DB}\) for p-type transistors built in n-well substrate.

Four current branches have to be biased with the same \(I_B\).

Proper behavioural equations, though approximated, have to be used (i.e., squared law for super- and exponential law for sub-threshold working conditions, respectively).

Since the comparator is working in weak-inversion, just overlap capacitance have been computed and other capacitive contributes have been neglected.

References

Alioto, M. (2017). Enabling the internet of things: From integrated circuits to integrated systems. Springer International Publishing. https://doi.org/10.1007/978-3-319-51482-6

Greatbatch, W., & Holmes, C. (1991). History of implantable devices. IEEE Engineering in Medicine and Biology Magazine, 10(3), 38–41. https://doi.org/10.1109/51.84185

Menz, M. D., Oralkan, O., Khuri-Yakub, P. T., & Baccus, S. A. (2013). Precise neural stimulation in the retina using focused ultrasound. Journal of Neuroscience, 33(10), 4550–4560. https://doi.org/10.1523/JNEUROSCI.3521-12.2013

Weber, M.J., Yoshihara, Y., Sawaby, A., Charthad, J., Chang, T., Garland, R., & Arbabian, A. (2017). A high-precision 36 \(\text{mm}^3\) programmable implantable pressure sensor with fully ultrasonic power-up and data link. In 2017 Symposium on VLSI Circuits (pp. C104–C105). https://doi.org/10.23919/VLSIC.2017.8008564

Piech, D. K., Kay, J. E., Boser, B. E., & Maharbiz, M. M. (2017). Rodent wearable ultrasound system for wireless neural recording. Annual International Conference IEEE Engineering Medical Biological Socity 2017, 221–225. https://doi.org/10.1109/EMBC.2017.8036802

Meng, M., & Kiani, M. (2019). Gastric seed: Toward distributed ultrasonically interrogated millimeter-sized implants for large-scale gastric electrical-wave recording. IEEE Transactions on Circuits and Systems II: Express Briefs, 66(5), 783–787. https://doi.org/10.1109/TCSII.2019.2908072

Das, R., Moradi, F., & Heidari, H. (2020). Biointegrated and wirelessly powered implantable brain devices: A review. IEEE Transactions on Biomedical Circuits and Systems, 14(2), 343–358. https://doi.org/10.1109/TBCAS.2020.2966920

Sonmezoglu, S., & Maharbiz, M. M. (2020) In 2020 IEEE International Solid- State Circuits Conference - (ISSCC) (pp. 454–456). https://doi.org/10.1109/ISSCC19947.2020.9062946

Gao, W., Liu, W., Hu, Y., & Wang, J. (2020). Study of ultrasonic near-field region in ultrasonic liquid-level monitoring system. Micromachines, 11(8), 763. https://doi.org/10.3390/mi11080763

Ghovanloo, M., & Najafi, K. (2004). Fully integrated wideband high-current rectifiers for inductively powered devices. IEEE Journal of Solid-State Circuits, 39(11), 1976–1984. https://doi.org/10.1109/JSSC.2004.835822

Lee, H. M., & Ghovanloo, M. (2012). In 2012 IEEE International solid-state circuits conference (pp. 286–288). https://doi.org/10.1109/ISSCC.2012.6177017

Charthad, J., Weber, M. J., Chang, T. C., & Arbabian, A. (2015). A mm-sized implantable medical device (IMD) with ultrasonic power transfer and a hybrid Bi-directional data link. IEEE Journal of Solid-State Circuits, 50(8), 1741–1753. https://doi.org/10.1109/JSSC.2015.2427336

Chang, T. C., Weber, M. J., Wang, M. L., Charthad, J., Khuri-Yakub, B. P. T., & Arbabian, A. (2016). Design of tunable ultrasonic receivers for efficient powering of implantable medical devices with reconfigurable power loads. IEEE Transactions on Ultrasonics, Ferroelectrics, and Frequency Control, 63(10), 1554–1562. https://doi.org/10.1109/TUFFC.2016.2606655

Ibrahim, A., Meng, M., & Kiani, M. (2018). A comprehensive comparative study on inductive and ultrasonic wireless power transmission to biomedical implants. IEEE Sensors Journal, 18(9), 3813–3826. https://doi.org/10.1109/JSEN.2018.2812420

Jiang, D., Shi, B., Ouyang, H., Fan, Y., Wang, Z. L., & Li, Z. (2020). Emerging implantable energy harvesters and self-powered implantable medical electronics. ACS Nano, 14(6), 6436–6448. https://doi.org/10.1021/acsnano.9b08268

Zeng, Z., Estrada-López, J. J., Abouzied, M. A., & Sánchez-Sinencio, E. (2020). A reconfigurable rectifier with optimal loading point determination for RF energy harvesting from -22 dBm to -2 dBm. IEEE Transactions on Circuits and Systems II: Express Briefs, 67(1), 87–91. https://doi.org/10.1109/TCSII.2019.2899338

Shi, C., Costa, T., Elloian, J., Zhang, Y., & Shepard, K. L. (2020). A 0.065-\(\text{ mm}^3\) monolithically-integrated ultrasonic wireless sensing mote for real-time physiological temperature monitoring. IEEE Transactions on Biomedical Circuits and Systems, 14(3), 412–424. https://doi.org/10.1109/TBCAS.2020.2971066

Sawaby, A., Wang, M. L., So, E., Chien, J. C., Nan, H., Khuri-Yakub, B. T. & Arbabian, A. (2018). In 2018 IEEE Symposium on VLSI Circuits (pp. 189–190). https://doi.org/10.1109/VLSIC.2018.8502293

Barbruni, G. L., Ros, P. M., Demarchi, D., Carrara, S., & Ghezzi, D. (2020). Miniaturised wireless power transfer systems for neurostimulation: A review. IEEE Transactions on Biomedical Circuits and Systems, 14(6), 1160–1178. https://doi.org/10.1109/TBCAS.2020.3038599

Ballo, A., Bottaro, M., & Grasso, A. D. (2021). A review of power management integrated circuits for ultrasound-based energy harvesting in implantable medical devices. Applied Sciences, 11(6). https://doi.org/10.3390/app11062487.

Ballo, A., Grasso, A. D., Privitera, M. (2022). In 2022 35th SBC/SBMicro/IEEE/ACM Symposium on integrated circuits and systems design (SBCCI) (pp. 1–6). https://doi.org/10.1109/SBCCI55532.2022.9893249

Lu, Y., Ki, W. H., Lu, Y., & Ki, W. (2018). CMOS Integrated circuit design for wireless power transfer. Analog circuits and signal processing (1st ed.). Springer Singapore.

Cheng, L., Ki, W. H., Lu, Y., & Yim, T. S. (2016). Adaptive on/off delay-compensated active rectifiers for wireless power transfer systems. IEEE Journal of Solid-State Circuits, 51(3), 712–723.

Lu, Y., Ki, W. H., & Yi, J. (2011). In 2011 Symposium on VLSI circuits - digest of technical papers (pp. 246–247).

Ballo, A., Grasso, A. D., & Privitera, M. (2022). A 28 nm bulk cmos fully digital bpsk demodulator for us-powered imds downlink communications. Electronics, 11(5). https://doi.org/10.3390/electronics11050698.

Alves, N., Kim, Angela, Tan, Jeremy, Hwang, Germain, Javed, Talha, Neagu, Bogdan, & Courtney, Brian K. (2020). Cardiac tissue-mimicking ballistic gel phantom for ultrasound imaging in clinical and research applications. Ultrasound in Medicine & Biology, 46(8), 2057–2069. https://doi.org/10.1016/j.ultrasmedbio.2020.03.011

Razavi, B. (2021). Fundamentals of microelectronics (3rd ed.). Wiley.

Ballo, A., Grasso, A. D., & Privitera, M. (2021). In 2021 IEEE international midwest symposium on circuits and systems (MWSCAS) (pp. 344–347). https://doi.org/10.1109/MWSCAS47672.2021.9531877

Cheng, H. C., Gong, C. S. A., & Kao, S. K. (2018). A 13.56 mhz cmos high-efficiency active rectifier with dynamically controllable comparator for biomedical wireless power transfer systems. IEEE Access, 6, 49979–49989. https://doi.org/10.1109/ACCESS.2018.2868743

Masui, S., Ishii, E., Iwawaki, T., Sugawara, Y. & Sawada, K. (1999). In 1999 IEEE international solid-state circuits conference. Digest of technical papers. ISSCC. First Edition (Cat. No.99CH36278) (pp. 162–163). https://doi.org/10.1109/ISSCC.1999.759174

Cha, H. K., Park, W. T., & Je, M. (2012). A CMOS rectifier with a cross-coupled latched comparator for wireless power transfer in biomedical applications. IEEE Transactions on Circuits and Systems II: Express Briefs, 59(7), 409–413. https://doi.org/10.1109/TCSII.2012.2198977

Pelgrom, M., Duinmaijer, A., & Welbers, A. (1989). Matching properties of mos transistors. IEEE Journal of Solid-State Circuits, 24(5), 1433–1439. https://doi.org/10.1109/JSSC.1989.572629

Acknowledgements

This work was supported by the Brain28nm Project (Prot.20177MEZ7T)-Italian Minister of University and Research.

Funding

Open access funding provided by Università degli Studi di Catania within the CRUI-CARE Agreement.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Ballo, A., Grasso, A.D. & Privitera, M. Active and passive rectification methods for US-powered IMDs. Analog Integr Circ Sig Process 117, 21–34 (2023). https://doi.org/10.1007/s10470-023-02166-8

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-023-02166-8