Abstract

This article presents an exact mid-band gain-expression for the CMOS operational-transconductance-amplifier (OTA) with low-voltage-cascode-current-mirror (LVCCM) load. Its small-signal analysis is not available in any CMOS text-book or other published sources/articles. A simplified and innovative technique is employed in performing this analysis with an in depth tutorial flavor. It shows that the derived mid-band gain of the CMOS OTA with LVCCM load is significantly more accurate than that obtained using the highly approximate classical gain-expression of the OTA employing a standard cascode-current-mirror equivalence which may be used in textbooks and other articles. Circuit simulations employing the 180-nm and 65-nm TSMC CMOS process technologies has been performed to indicate the progressively higher accuracy of the derived exact gain-expression for the LVCCM loaded OTA with technology scaling. This new analysis indicates an additional degree of freedom in tuning the gain of the OTA with LVCCM load using an additional transconductance parameter, gm5,6 of (M5, M6). A simplified expression is also deduced which provides an improvement over the classical approximate expression, due to the additional design insight and accuracy provided by this additional parameter while still being amenable to first order gain evaluation in a simplified way. The presented analysis is new and has not been reported before in open literature in any form.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Operational-transconductance-amplifier (OTA) with active cascode-current-mirror load is an well-known topology often used in analog CMOS integrated circuits [1]. It is also used as a suitable differential-to-single-ended converter in analog signal processing using differential signals. In today’s highly scaled low-voltage CMOS systems and applications the low-voltage-cascode-current-mirror (LVCCM) [1,2,3] is often used instead of the regular cascode-current-mirror to overcome the voltage headroom constraint. It has found application in many commercial CMOS ICs as well [4]. The small-signal mid-band analysis of the OTA with active LVCCM is however not available in [1] or other classic texts such as [5,6,7,8]. In several recent articles [9,10,11,12] the 2nd author provided simplified small-signal analysis for a large number of various gain-stages which were not available before. Also, recently in [13] co-authored by the 2nd author, the accurate mid-band analysis of the differential-amplifier OTA with the standard current-mirror load was provided indicating superior accuracy compared to the gain equation provided in [1]. In addition, in [14] an accurate gain-expression for the non-ideal differential-amplifier OTA was also provided by the 2nd author with significantly higher accuracy than that available in [1]. In this article, an exact small-signal mid-band analysis of the OTA with LVCCM load is provided which is not available in any text-book, article or web-source. Results of circuit simulations using the 180-nm and 65-nm TSMC CMOS process technologies are provided to indicate the progressively higher accuracy of the derived exact gain-expression of the OTA with LVCCM load with technology scaling. This new exact gain-expression as well as a simplified form of this exact gain-expression performs better than the classical expression by providing a more accurate mid-band gain value and a further degree of freedom in tuning the gain of the OTA with LVCCM load, using an additional transconductance parameter. It thus provides more design insight in adjusting the mid-band gain of the OTA with LVCCM load, compared to the classical approximate expression available in open literature and textbooks. The simplified form of this new exact gain expression is also amenable to first order gain calculation in a simplified way while providing better design intuition using one additional design parameter as compared to the classical equation. Standard notations employed in [1, 5, 7, 8] have been used in the equations in this article for describing all the CMOS parameters in the small-signal modelling following the standard convention in analog CMOS circuit analysis. In addition, appropriate DC, AC and composite voltage/current signal symbols are employed. Also, it is to be clarified in this context, that, all voltages and currents in lower-case letters along with upper-case subscripts are quantities containing both a large-signal DC Bias (quiescent) value and a small-signal (AC) variation (perturbation) superimposed on it. All voltages/currents in uppercase letters along with uppercase subscripts are DC-bias quantities, and all voltages/currents in lowercase letters along with lowercase subscripts are just the AC perturbation quantities.

2 Exact analysis of the differential-amplifier (OTA) with low-voltage-cascode-current-mirror load

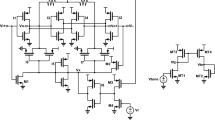

A CMOS OTA with low-voltage-cascode-current-mirror load [1] is shown in the Fig. 1 along-with the composite input and output signals and the DC-bias voltages. Next, Fig. 2 shows its AC-equivalent circuit with all the bias-voltages set at AC ground. For a fully matched input differential-pair the drain of M7 (d7) can be considered to be at AC-ground (Virtual ground) and hence the input differential-pair can be decoupled and decomposed into two half-circuit components near the AC ground. Figure 3 shows this decomposition of the input circuit for a matched input differential-pair. Here,

A standard CMOS OTA with active low-voltage-cascode-current-mirror load [1] showing composite signals at the inputs and the output

Next, Fig. 4 presents the left-half-circuit of the AC-equivalent circuit of the OTA and the technique for determining the load impedance (RL) looking into the drain of M1 using a voltage source, vl that drives the current, il into the load of M1. Following on, Fig. 5 depicts the small-signal equivalent circuit for the load (RL) connected to the drain of M1 in the Fig. 4(b). In Fig. 6 the equivalent circuit of the Fig. 5 is simplified by realizing that vgs5,6 = vl and that vg3 and vb3 are at the ground potential. Next, Fig. 7 provides a further simplified form of the equivalent circuit in the Fig. 6 by merging the two current sources for M3 and removing the negative sign by inverting the direction of the combined current-source for M3. Finally, Fig. 8 provides the reduced and simplified form of the equivalent circuit for the load (RL) looking at the drain of M1 by converting the Norton sources to Thevenin’s sources. A simplified pictorial approach using successive simplification of small-signal equivalent circuits without sacrificing any mathematical details is thus demonstrated here in transforming from Fig. 5 through to Fig. 8 just by inspection. Only one simple source transformation from Norton source to thevenin’s source is employed in the Fig. 8 and no complicated circuit analysis or theorems is used. Then, from the Fig. 8,

a Left-half circuit of the AC-equivalent circuit of the OTA in Fig. 3 b determining the load impedance (RL) looking into the load of M1

Small-signal equivalent circuit for the load (RL) connected to the drain of M1 in the Fig. 4(b)

Simplified form of the equivalent circuit in Fig. 5 by considering that vgs5,6 = vl and that vg3 and vb3 are at AC ground potential

Further simplified form of the equivalent circuit in Fig. 6 by merging the current sources for M3 and inverting the arrow to account for the negative sign

Reduced and simplified form of the equivalent circuit in Fig. 7 obtained by converting Norton sources to Thevenin’s sources

So that,

Hence, KVL along the equivalent circuit in Fig. 8 produces,

From which, by changing sides,

Or, the load resistance, RL looking at the drain of M1 is given by,

Hence, the small-signal voltage at the drain of M1 (and also at the gates of M5 and M6) is given by,

Next, Fig. 9 shows the right-hand-side half-circuit of the AC-equivalent circuit in Fig. 3 where vg6 = vdrainM1. Following-on, Fig. 10 provides the Norton equivalent circuit model for the PMOS cascode upper input section (with input at the gate of M6) formed by M4 and M6 in the Fig. 9 inspecting at the output. This Norton model has an equivalent transconductance, GX and an equivalent output impedance, RX given by [9],

Right-hand-side half-circuit of the AC-equivalent circuit in the Fig. 3 where vg6 = vd1

Norton equivalent circuit model for the PMOS cascode upper-section formed by M4 and M6 in Fig. 9 inspecting at the output

Figure 11 shows the final reduced form of the small-signal equivalent circuit for the matched composite CMOS OTA with active low-voltage-cascode-current-mirror load. Next, using (7, 8 and 9) and Fig. 11,

Since vg6 is negative, both the current-sources will accumulate and drop on the load to produce a positive output voltage. Next, expanding the terms, GX, RL and RX in (10) the exact differential voltage-gain (with vd being the input), \(A_{V\_exact}\) is given by (11) at the top of the next page.

Next, employing approximations assuming long-channel devices (large device output impedances) in relation to technology, to the various constituent terms of the exact and accurate gain-expression in (11), a concise form of the gain-expression can be obtained, while progressing towards the classical gain-expression, as follows:

In the term, \(\frac{{g_{{\text{m5,6}}} r_{{\text{o5,6}}} \left\{ {(g_{{\text{m3,4}}} + g_{{\text{mb3,4}}} )r_{{\text{o3,4}}} + 1} \right\}}}{{r_{{\text{o5,6}}} + r_{{\text{o5,6}}} (g_{{\text{m3,4}}} + g_{{\text{mb3,4}}} )r_{{\text{o3,4}}} + r_{{\text{o3,4}}} }}\), for the denominator \([r_{{\text{o5,6}}} + r_{{\text{o5,6}}} (g_{{\text{m3,4}}} + g_{{\text{mb3,4}}} )r_{{\text{o3,4}}} + r_{{\text{o3,4}}} ]\) it is assumed that \([r_{{\text{o5,6}}} + r_{{\text{o5,6}}} (g_{{\text{m3,4}}} + g_{{\text{mb3,4}}} )r_{{\text{o3,4}}} ] \gg r_{{\text{o3,4}}}\), so that the denominator can be simplified as just equal to \([r_{{\text{o5,6}}} + r_{{\text{o5,6}}} (g_{{\text{m3,4}}} + g_{{\text{mb3,4}}} )r_{{\text{o3,4}}} ]\) based on the cascode output impedance approximation for long channel devices[1]. Hence the term, \(\frac{{g_{{\text{m5,6}}} r_{{\text{o5,6}}} \left\{ {(g_{{\text{m3,4}}} + g_{{\text{mb3,4}}} )r_{{\text{o3,4}}} + 1} \right\}}}{{r_{{\text{o5,6}}} + r_{{\text{o5,6}}} (g_{{\text{m3,4}}} + g_{{\text{mb3,4}}} )r_{{\text{o3,4}}} + r_{{\text{o3,4}}} }} \approx g_{{\text{m5,6}}}\).

Similarly, in the term, \(\frac{{(g_{m3,4} + g_{mb3,4} )r_{05,6} r_{03,4} + r_{05,6} + r_{03,4} }}{{1 + g_{m5,6} r_{05,6} + (g_{m3,4} + g_{mb3,4} )g_{m5,6} r_{05,6} r_{03,4} }}\), the numerator \([(g_{m3,4} + g_{mb3,4} )r_{05,6} r_{03,4} + r_{05,6} + r_{03,4} ]\) can be approximated as just equal to, \([(g_{m3,4} + g_{mb3,4} )r_{05,6} r_{03,4} + r_{05,6} ]\), and for the denominator \([1 + g_{m5,6} r_{05,6} + (g_{m3,4} + g_{mb3,4} )g_{m5,6} r_{05,6} r_{03,4} ]\) it is assumed that, in general, for technology with large channel lengths, the approximation, \([g_{m5,6} r_{05,6} + (g_{m3,4} + g_{mb3,4} )g_{m5,6} r_{05,6} r_{03,4} ] \gg \;1\) holds, so that the denominator can be simplified as, \([g_{m5,6} r_{05,6} + (g_{m3,4} + g_{mb3,4} )g_{m5,6} r_{05,6} r_{03,4} ]\). Next taking \(g_{m5,6}\) common, the simplified denominator becomes, \(g_{m5,6} [r_{05,6} + (g_{m3,4} + g_{mb3,4} )r_{05,6} r_{03,4} ]\), thus rendering the term,

Consequently, the accurate and exact version of the gain-expression in (11) can be collapsed into the reduced and simplified form given by,

After further simplification of the term \(r_{01,2} + \frac{1}{{g_{m5,6} }}\) to just \(r_{01,2}\), assuming that, \(r_{01,2} \gg \frac{1}{{g_{m5,6} }}\) based on long channel device approximation [1] in relation to technology, the simple approximate form of the gain-expression is given by,

And hence, in the final approximate form, the mid-band gain-expression is given by,

Which is the classical gain-expression similar to the approximate gain-expression for an OTA with standard cascode-current-mirror load. The difference in the accuracy between the gain expressions in (11 and 14) thus relates to process technology. Comparing (11 and 14) it is evident that employing the approximate gain expression of a standard cascode-current-mirror load is quite inaccurate compared to the exact form of the gain for the OTA with LVCCM load particularly for advanced technologies where the device output impedance reduces progressively compared to that for long channel devices. The gain-expression in (11) provides significantly more design insight by indicting that the gain is a product of a complex composite transconductance term (involving all the devices in the structure) with the output-impedance at the single-ended output, instead of being the product of just the transconductance of the differential input-pair devices with the output-impedance at the single-ended output. Based on (11) and from its reduced form in (12) a further degree of freedom in the design is available through the fine-tuning of the transconductance of the cascode mirror devices (M5, M6) which gets cancelled mid-way through the further simplification step in (13). This additional design parameter is thus missing in the simple approximate (classical) expression in (14). Hence the simplified expression in (12) provides better design intuition through the additional degree of freedom using one additional design parameter as compared to the classical equation. Also, as device output impedances becomes generally smaller with reduced channel lengths through process scaling, the exact gain-expression in (11) will yield a gain-value closer to the actual circuit-simulated value compared to the classical approximate expression in (14). In addition, the simplified gain-expression in (12) deduced from the exact expression in (11) provides an improvement over the classical method represented by the approximate expression in (14), due to the additional design insight and accuracy provided by the additional transconductance parameter, gm5,6 of (M5, M6) while still being amenable to the evaluation of the first order gain in a simplified way.

The calculated gain-error factors for the exact gain-expression in (11), and the approximate (classical) gain-expression in (14) with respect to the actual Cadence circuit simulated gain (\(A_{v\_actual}\)) can be given by,

The derivations provided in this paper also assists in finding the mirror pole [1], \(\omega_{{\text{PM}}}\) at the drain of M1 (mirror node) using the derived value of RL in (6) for the time-constant,\(\tau_{PM}\) at this node. It is thus approximately given by,

where, CE is approximately the total capacitance at the mirror node, and, is given by,

Consequently, the derivations in this paper also helps in estimating the frequency response of the OTA with low-voltage cascode current mirror load.

3 Numerical analysis and circuit simulation results

The small-signal gain of the CMOS OTA with LVCCM load in the Fig. 1 was simulated through AC-analysis on Cadence Spectre. The gain was also numerically calculated on MATLAB using both (11 and 14). These results were then compared. Two sets of calculations and circuit simulations were performed employing the 180-nm and the 65-nm CMOS process technologies.

Simulation and calculation set I: A power-supply of 1.8 V and the 180-nm TSMC CMOS technology was employed for this set of calculations and simulations. The total bias-current through the tail device M7 was 19.2189 µA with 9.60943 µA in each half-circuit. The bias-voltages were, VB1 = 600 mV, VB2 = 900 mV, and the DC common-mode bias voltage at the two differential-inputs was 800 mV. The MOSFET device sizes and their respective threshold-voltages, transconductances, body transconductances, and output impedances were as follows:

For (M1, M2), (W/L) = 7 µm/0.6 µm, gm = 156.25µ-mho, gmb = 40.774 µ-mho, ro = 1.336 MΩ, and Vth = 575.76 mV. For (M3, M4), (W/L) = 2.7 µm/0.5 µm, gm = 74.71 µ-mho, gmb = 24.172 µ-mho, ro = 866.569 kΩ, and Vth = − 561.25 mV. For (M5, M6), (W/L) = 6.2 µm/0.5 µm, gm = 102.74 µ-mho, gmb = 35.13 µ-mho, ro = 213.33 kΩ, and Vth = − 516.69 mV. Finally, for M7, (W/L) = 5 µm/0.6 µm, gm = 225.619 µ-mho, gmb = 63.812 µ-mho, ro = 176.076 kΩ, and Vth = 515.51 mV.

Figure 12 shows the comparison of the actual Cadence Spectre simulated differential-gain (Av_actual) of the CMOS OTA with LVCCM load, with the MATLAB calculated estimates using the new exact gain-expression in (11) and the approximate (classical) expression for standard cascode-current-mirror load equivalence in (14), employing the 180-nm TSMC CMOS process technology. The actual AC-simulated mid-band gain (Av_actual) was 183.02 (= 45.25 dB), the calculated mid-band gain using (11) was 185.14 (= 45.35 dB), and the calculated mid-band gain using (14) was 195.66 (= 45.83 dB).

Comparison of the actual Cadence simulated differential-gain (Av_actual) of the CMOS OTA with LVCCM load, with the numerical estimates using the new exact gain-expression in (11) and the approximate (classical) gain-expression for standard cascode-current-mirror load equivalence in (14), employing the 180-nm TSMC CMOS process for the circuit in Fig. 1

Simulation and calculation set II: A power-supply of 1 V and the 65-nm TSMC CMOS technology was employed for the 2nd set of calculations and simulations. The total bias-current through the tail device M7 was 67.03 µA with 33.51 µA in each half-circuit. The bias-voltages were, VB1 = 400 mV, VB2 = 550 mV, and the DC common-mode bias voltage at the two differential-inputs was 450 mV. The MOSFET device sizes and their respective threshold-voltages, transconductances, body transconductances, and output impedances were as follows:

For (M1, M2), (W/L) = 1 µm/0.1 µm, gm = 408.4µ-mho, gmb = 64.6 µ-mho, ro = 53 kΩ, and Vth = 422.7 mV. For (M3, M4), (W/L) = 11 µm/0.1 µm, gm = 564.4 µ-mho, gmb = 59.65 µ-mho, ro = 19.3 kΩ, and Vth = − 389.9 mV. For (M5, M6), (W/L) = 5 µm/0.1 µm, gm = 468.6 µ-mho, gmb = 55.9 µ-mho, ro = 20.91 kΩ, and Vth = − 367 mV. Finally, for M7, (W/L) = 3 µm/0.1 µm, gm = 867.2 µ-mho, gmb = 149.3 µ-mho, ro = 6.221 kΩ, and Vth = − 416.2 mV.

Figure 13 depicts the comparative plot of the actual Cadence simulated differential-gain (Av_actual) of the CMOS OTA with LVCCM load, along-with the MATLAB calculated estimate using the new exact gain-expression in (11) and the approximate (classical) gain-expression for standard cascode-current-mirror load equivalence in (14), employing the 65-nm TSMC CMOS process technology. The simulated mid-band gain (Av_actual) was 17.82 (= 25.02 dB), the mid-band gain using (11) was 18.22 (= 25.21 dB), and the gain using (14) was 20.25 (= 26.13 dB).

Comparison of the actual Cadence simulated differential-gain (Av_actual) of the CMOS OTA with LVCCM load, with the numerical estimate using the new exact gain-expression in (11) and the approximate (classical) gain-expression for standard cascode-current-mirror load equivalence in (14), employing the 65-nm CMOS process for the circuit in Fig. 1

It is thus clearly evident that the plots for the exact mid-band gain-expression in (11) matches very closely (almost tracing) the simulated mid-band gain obtained through AC circuit-simulation. The mid-band gain obtained using the approximate (classical) gain-expression in (14) is quite inaccurate compared to the exact gain-expression in (11). Table 1 shows a comparison of the results for the two sets of simulations and calculations using the 180-nm and the 65-nm TSMC CMOS process technologies. As the output impedances of the devices becomes smaller (having smaller finite values) with technology scaling the classical mid-band gain-expression in (14) becomes more inaccurate compared to the exact mid-band gain-expression in (11). For the 180-nm CMOS process, employing (15) the gain-error compared to the actual Cadence Spectre circuit-simulated value (Av_actual) is only around 1.15% by using the exact mid-band gain-expression in (11). Whereas, the error by using the approximate (classical) gain-expression in (14) compared to the circuit-simulation (Av_actual) was 7%. For the 65-nm CMOS process, employing (15) the gain-error is around 2.24% by using the exact gain-expression in (11). On the other hand, the gain-error employing (16) by using the approximate (classical) gain-expression in (14) compared to the circuit-simulated mid-band gain (Av_actual) was as much as 12%. And, hence, the gain-error increases with technology scaling with the reduction in channel length.

4 Conclusion

An exact small-signal mid-band gain-expression for the CMOS differential-amplifier OTA with low-voltage-cascode-current-mirror load has been deduced employing an innovative technique. This exact gain-expression indicates that the actual gain is only a fraction of the gain calculated by an approximate (classical) gain-expression using the standard cascode-current-mirror equivalence and the accuracy of the exact gain-expression increases significantly with reducing technology node. This new exact gain-expression thus provides a more accurate gain-estimate for today’s low-voltage deep nano-metric CMOS processes, and, has not been reported before. Both Cadence Spectre circuit simulations and numerical analysis using MATLAB is provided employing the 180-nm and 65-nm TSMC CMOS process technologies. The derived exact expression also provides new design insight in fine-tuning the gain of the OTA with LVCCM load using the transconductance gm5,6 of the cascode mirror devices (M5, M6) as can be seen from (11 and 12). The simplified expression in (12) deduced from the exact expression in (11) provides an improvement over the approximate (classical) method, due to the additional accuracy provided by this additional transconductance parameter, gm5,6 of (M5, M6) while still being amenable to first order gain analysis. This additional degree of design freedom in gain adjustment is lost through the approximation steps as can be seen from (13 and 14). Hence this paper provides an improved analysis and better design intuition on the topic of mid-band gain expression for the OTA with low-voltage cascode current mirror load.

Data and materials availability

Not applicable—no data or materials is available.

References

Razavi, B. (2001). Design of analog CMOS integrated circuits. McGraw Hill.

Hassen, N., Gabbouj, H. B., & Besbes, K. (2011). Low-voltage high performance current mirrors: Application to linear voltage to current converter. International Journal of Circuit Theory and Applications, 39(7), 47–60.

Raj, N., Singh, A. K., & Gupta, A. K. (2014). Low voltage bulk driven self-biased cascode current mirror with bandwidth enhancement. Electronics Letters, 50(1), 23–25.

Analog Devices ADA 4530-1 chip data-sheet, available on-line: https://www.analog.com/en/products/ada4530-1.html#product-evaluationkit

Razavi, B. (2008). Fundamentals of microelectronics. John Wiley & Sons Inc.

Allen, P. E., & Holberg, D. A. (2002). CMOS analog circuit design (2nd ed.). Oxford University Press.

Johns, D., & Martin, K. W. (1997). Analog integrated circuit design. John Wiley & Sons.

Sedra, A. S., & Smith, K. C. (2010). Microelectronic circuits (6th ed.). Oxford University Press.

Hasan, S. M. R. (2015). “Simplified analog CMOS mid-band small-signal analysis utilizing short-circuits and incremental perturbations. International journal of electrical engineering education (IJEEE) SAGE, UK, 52(4), 356–369.

Hasan, S. M. R. (2017). Novel inspection-based Mid-band derivations for CMOS cascodes and gm-boosted topologies along-with simplified compound structure gain-analysis. Journal of Analog Integrated Circuits and Signal Processing, 91(1), 21–41.

Hasan, S. M. R. (2017). On gm-boosted follower-amplifier and its novel circuit transformation based mid-band derivations. Journal of Analog Integrated Circuits and Signal Processing., 93(1), 107–114.

Hasan, S. M. R., & Kumari, M. (2020). A new mid-band analysis methodology for source-followers and drain-loaded source-follower with application in accurate differential-amplifier mismatch analysis. Journal of Analog Integrated Circuits and Signal Processing-An International Journal, Springer, 103(2), 259–271.

Hasan, S. M. R., & Kumari, M. (2019). Accurate mid-band analysis of the differential-amplifier with active current-mirror load. IEEE VLSI Circuits and Systems Letter, 5(1), 1–5.

Hasan, S. M. R. (2020). The “nonideal” drain-loaded source-follower and accurate differential-amplifier analysis. International Journal of Circuit Theory and Applications., 48(7), 1194–1200.

Funding

Open Access funding enabled and organized by CAUL and its Member Institutions. No funding was received for the work done for this paper.

Author information

Authors and Affiliations

Contributions

Naina Singhal mostly contributed in performing the MATLAB and Cadence Circuit Simulations, while, Rezaul Hasan mostly contributed to the writing of the paper and deriving the equations.

Corresponding author

Ethics declarations

Conflict of interest

There are no interests of a financial or personal nature from any of the authors.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Singhal, N., Hasan, S.M.R. On the exact mid-band gain of the CMOS OTA with low-voltage-cascode-current-mirror. Analog Integr Circ Sig Process 115, 335–343 (2023). https://doi.org/10.1007/s10470-023-02161-z

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-023-02161-z