Abstract

This work presents a complementary PMOS NMOS voltage-controlled power oscillator (VCO) based on a high quality (Q) factor off-chip inductor in 130 nm CMOS process. The proposed VCO achieves a frequency tuning range of 166% from 393 MHz to 4.17 GHz and this wide tuning range is divided into six bands where each band is also sub-divided into three bands using a single switching voltage. The proposed design takes into consideration the effect of the bond wire that is used to connect the off-chip inductor with the VCO core moreover, the measured SNP files of the off-chip inductors are utilized to ensure accurate results. This technique improves the figure of merit (FoM) by 4–25 dB compared to the conventional inductor VCO. Using six different values of the off-chip inductors, the proposed VCO works in six bands with a tuning range of 166%, and a minimum phase noise of − 127 dBc/Hz @ 1 MHz offset frequency 2.2 GHz carrier. Furthermore, the proposed VCO draws 1.37 mA from 1.1 V supply voltage and has a minimum achieved Figure-of-Merit (FOM) equal to -193 dBc/Hz with a maximum output power of 4.25 dBm. The VCO core area equals 0.07 \({\mathrm{mm}}^{2}\), while the total chip area including RF pads and output buffers is \({0.437\mathrm{ mm}}^{2}\).

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

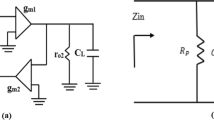

Phase-locked loops (PLLs) are commonly utilized for clock generation in high-speed digital systems and local oscillation signals in wireless communication systems. The voltage-controlled oscillator (VCO) is a crucial component of PLLs. The most important requirements for VCOs are low phase noise and wide tuning range. Other essential considerations are low implementation cost and ease of integration. There are two basic structures of VCO: the ring VCO and the LC-VCO. The ring VCO exhibits a wide tuning range, ease of integration, and low cost, but poor phase noise and high-power consumption. While the LC VCO reduces the power dissipation and maintains low phase noise compared to ring VCO [1, 2].

Several types of research have been reported to increase the frequency tuning range of the VCOs. One method is to design multi-core oscillators at different frequencies and enables a single oscillator at a time, but this technique requires an active element and LC circuit for each band [3]. Another technique relies on implementing switching resonators (inductors or capacitors) [4, 5]. Variable inductors using switches to eliminate part of the inductor were presented [6], switched capacitors were also presented [7], and variable MEMS varactor [8]. However, these switching techniques suffer from the needed large area for the LC tank circuit, and the degradation of the Q-factor of the LC tank circuit, because of the series resistance of the switches implemented by the MOS transistor and, consequently, the phase noise of the oscillator becomes poor.

Phase noise improvement is achieved by maximizing the Q-factor of the LC tank circuit where the maximum losses in the tank circuit appear in the on-chip inductors, there are a lot of studies to increase the on-chip inductor Q-factor at the expense of the chip area as changing inductor shape, implementing pattern ground structure under the inductor, or designing shunt (multi-layers) inductor [9,10,11]. Also, another interest is directed to implement high Q-factor active inductors, but this consumed high power, so this aspect is not recommended [12]. In [13] an active LC tank VCO using a differential boot-strapped inductor (DBSI) was designed and achieved poor phase noise, and low output power of − 11 dBm. In [14] the authors used off-chip inductors to design a reconfigurable power amplifier that covers multi-band applications and improves the RF circuit performance. In [15] a compact CMOS linear trans-conductance NMOS PMOS core without a choke inductor to minimize die area was presented and this achieved a phase noise of − 112 dBc/Hz and low output power of − 10.4 dBm. In [16], a wideband NMOS VCO using a digital switching capacitor bank was introduced with a maximum output power of − 6 dBm, and the power dissipated equals 2.37 mW. In [17,18,19] low phase noise and low power dissipation VCOs were designed, in [17] a class-C VCO using a new structure asymmetry inductor was designed in 130 nm CMOS process and achieved an FTR of 34.5% from 2 to 2.9 GHz. While in [18, 19] a tail current technique or filtering technique is used for phase noise improvement.

To implement VCO in medical frequency (low-frequency band) the first selection is the ring oscillator with poor phase noise and high DC power consumption, so the ring oscillator disqualifies in medical application. The second solution is the LC oscillator, LC-tank circuit needs an inductor in the range from 85 to 62 nH for this application, and implementing this inductance value on-chip is impossible due to the balky area size and low-quality factor of the on-chip inductor. So, the proposed VCO offers the best solution for the 393–700 MHz frequency band by using a high Q-factor off-chip inductor. The proposed VCO covers a frequency band from 393 MHz to 4.17 GHz so this can be used in Medical (ISM) bands from 393 to 700 MHz, GSM900, LTE, and Multi-standard applications.

In this work low phase noise and wideband tuning range voltage-controlled power oscillator is proposed, where the frequency tuning range is risen by using six high Q-factor off-chip inductors. Also, using those inductors enhances the VCO performance (tuning range, phase noise, and output power) compared to the conventional inductor. Moreover, three sub-bands are achieved in each band using a single control pin (\({V}_{SW}\)). The paper is organized as follows; Sect. 2 presents the design of the proposed VCO while Post-layout simulation results are introduced in Sect. 3. Section 4 concludes the work.

2 Proposed VCO design

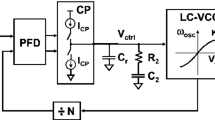

The proposed voltage-controlled power oscillator (VCO) consists of LC-voltage controlled oscillator and two output buffers as displayed in Fig. 1.

2.1 VCO Schematic

The proposed LC-VCO is a complementary cross-coupled PMOS NMOS, that consists of NMOS pair (M1–2), PMOS pair.

(M3–4), PMOS current source (M5) that has low flicker noise compared to NMOS current source, feedback capacitor Cfp that enhances the phase noise. PMOS current source is preferred over the NMOS current sink. PMOS current source is generally utilized because the PMOS transistor has less noise flicker than the NMOS transistor [20]. The frequency tuning range is achieved by the varactor capacitor Cv, the improved switching capacitor Csw to divide each band into three sub-bands, and the high-quality factor off-chip inductor L as shown in Fig. 1. The enhanced varactor composes of a MOS varactor and MIM capacitor connected in series to improve the phase noise. In the first half cycle of the oscillation, the transistors M3 and M2 are in the on state, M4 and M1 are in the off state, and the current passes through the off-chip from left to right, in the second half cycle, the current direction in the resonator is opposite from right to left. The VCO core is followed by two output buffers, each one consisting of two NMOS transistors, and a chock off-chip inductor connected as a cascode amplifier to raise the output power. The buffer is a cascode amplifier because the cascode configuration achieves a high gain and high output power with good isolation over a wide bandwidth, mainly the cascade amplifier is used to increase the dBm output power for voltage-controlled power oscillator applications [21]. Capacitor Co that implemented on-chip and its value is determined to maximize the output power of the VCO. The component values of the proposed VCO circuit are described in Table 1.

2.2 Proposed LC-tank circuit

The spiral inductor usually encounters a low-quality factor, especially the high inductance value, therefore VCO design at the low-frequency band as Medical-band, GSM900, LTE, and Multi-standard applications or beyond is very challenging. The proposed method employs a high-quality factor off-chip inductors and then integrates it into the VCO using bond wire, therefore the proposed method alleviates the above problem of poor Q-factor and gives an alternative design approach to VCO at the low-frequency band. The proposed LC-tank circuit composes of an off-chip inductor, a switching varactor to achieve triple sub-bands, and a tuning varactor to tune between a minimum and maximum oscillation frequencies as illustrated in Fig. 1. The off-chip inductor is selected from six different values to cover the wide tuning range. The selected off-chip inductors have high-quality factors, and high self-resonance frequency so they solve the problems that appear in on-chip inductors. The bonding wire equivalent circuit is considered as Cpad that represents the pad capacitance and Lbond that represents the inductance of bonding wire as displayed in Fig. 1, the value of Lbond is about 1nH/mm [12], and the quality (Q) factor of bonding wire increases with frequency, where the Q-factor of bonding wire equal 50 at 1 GHz and equal 100 at 5 GHz more details about bonding wire in [14].

The discrete inductors are usually specified by the quality factor (Q), Tolerance (T), Self-Resonance Frequency (SRF), and Dimensions (D). Table 2 illustrates the manufacturing part numbers and specification parameters of the used discrete inductors. To ensure accurate results and take into consideration all the parasitic effects, the real model of the discrete components is used by inserting the manufacture SNP file (Measured S-parameters file) of the selected discrete components in the simulation tool. As clear in Table 2, all the chosen inductors have a self-resonance frequency above twice the operating frequency of the proposed VCO. Figure 2 displays the electrical model of an off-chip inductor where Lvar is the inductance, (C) represents the coupling capacitor, and R is loss resistance.

3 Post –layout simulation results

The proposed LC VCO is designed using 130 nm CMOS process. Advanced Design System (ADS) for circuit simulation, and Cadence Design Systems software for circuit layout and physical verifications. The layout of the suggested voltage-controlled oscillator is illustrated in Fig. 3, where the VCO core area equals 0.07 \({\mathrm{mm}}^{2}\), while the total chip area included the two output buffers, and pads is 0.437 \({\mathrm{mm}}^{2}\). The phase noise of the proposed VCO using the high Q-factor off-chip inductor is improved by 4–25 dB compared to the VCO that uses a conventional inductor provided by technology, as displayed in Fig. 4. The proposed VCO is biased from a supply voltage (VDD) of 1.1 V and draws a current of 1.37 mA while each output buffer draws 3.3 mA from 1.2 V supply voltage (VBuf) and Vbias is buffer biasing voltage and set to 0.62 V. In the proposed VCO VB is the biasing voltage of current source (M5) and connected to ground.

The proposed VCO has a frequency tuning range (FTR) of 166% from 393 MHz to 4.17 GHz as shown in Fig. 5 (a, b, c, d, e, f. This excellent tuning range is divided into six bands according to the inductor value (L) and each band is divided into three bands and controlled using switching voltage. The phase noise of the proposed VCO at 1 MHz offset changes from − 111 to − 127 dBc/Hz as plotted in Fig. 6.

Leeson’s formula predicts the phase noise at an offset frequency Δf from the oscillation frequency fosc is specified by [22];

Where F, k, T, Ps, and Q, are the noise factor, the Boltzmann’s constant, the absolute temperature, the average power dissipated, and the tank circuit quality factor, respectively. As clear in Eq. (1) when the tank circuit quality factor (Q) grows the oscillator phase noise will be enhanced.

As illustrated in Table 2, the quality factor of the selected inductor is at least three times of the conventional on chip inductor one. Study the case when the oscillation frequency equals 500 MHz and using Eq. (1) the phase noise at 1 MHz offset using the suggested VCO is enhanced by 16.5 dB compared to the technology inductor VCO.

The simulated figure of merit (FoM) of the suggested VCO versus oscillation frequency is plotted in Fig. 7, the best figure of merit is -193 dBc/Hz. The dBm output power of the proposed VCO versus oscillation frequency is illustrated in Fig. 8, with the maximum dBm value being 4.2dBm. Figure 9 shows the frequency tuning range of the stacked inductor VCO while the phase noise and figure of merit of the stacked inductor VCO are displayed in Fig. 10. The time-domain of differential output signals for the proposed VCO is shown in Fig. 11, the peak-to-peak output signal equals 1.2 V at \({V}_{Control}=1V\), and \({V}_{sw}=1V\) that means an oscillation frequency of 820 MHz.

Table 3 illustrates the frequency bands, phase, and output of the proposed VCO based on the inductance value in the LC tank circuit. The suggested differential VCO displays better or comparable performances than the reported VCOs implemented using the CMOS process in terms of FTR (%), Phase noise, \({P}_{DC}(mW)\), Area (\({\mathrm{mm}}^{2}\)), and FoM. The proposed differential VCO performance and comparison with the state-of-the art is illustrated in Table 4.

4 Conclusion

A low phase noise wide tuning range VCO is introduced. The proposed technique eliminates the detrimental effects of a conventional switched method on VCOs phase noise. By using high Q-factor inductors and feedback capacitors across PMOS transistors the phase noise of the proposed VCO is improved by 15 dB compared to conventional inductor VCO.

The proposed differential VCO achieves a wide frequency tuning range of 166% divided into six bands by using different inductor banks. Also, the proposed VCO consumes 1.5 mW, and achieves a low phase noise of − 127, and FOM of − 193 dBc/Hz, Finally, the chip area of the proposed VCO is 0.437 \({\mathrm{mm}}^{2}\).

Data availability

The data that support the findings of this study are available from the corresponding author, [Islam Mansour], upon reasonable request.

References

Mansour, M., Zekry, A., Ali, M. K., & Shawkey, H. (2020). A comparative study between Class-C and Class-B quadrature voltage-controlled power oscillator for multi-standard applications. Microelectron Journal, 98(8), 104726.

Kumar, V., Sivakumar, R., Jayasheela, C., Sarkar, M., & Singh, S. (2021). Phase noise performance stabilization of PLL system under dynamic vibration condition for airborne applications. International Journal of Microwave and Wireless Technologies, 13(4), 335–343. https://doi.org/10.1017/S1759078720001038

Iotti, L., Mazzanti, A., & Svelto, F. (2017). Insights into phase-noise scaling in switch-coupled multi-core LC VCOs for E-band adaptive modulation links. IEEE Journal of Solid-State Circuits, 52(7), 1703–1718.

Mansour, I., Aboualalaa, M., Allam, A., Abdel-Rahman, A. B., Abo-Zahhad, M., & Pokharel, R. K. (2018). Dual band VCO based on high quality factor switched interdigital resonator for Ku band using 180 nm CMOS technology. IEEE Transactions on Circuits and Systems II: Express Briefs. https://doi.org/10.1109/TCSII.2018.2817499

Li, G., Liu, L., Tang, Y., & Afshari, E. (2012). A low-phase-noise wide-tuning-range oscillator based on resonant mode switching. IEEE Journal of Solid-State Circuits, 47(6), 1295–1308.

Demirkan, M., Bruss, S. P., & Spencer, R. R. (2008). Design of wide tuning range CMOS VCOs using switched coupled-inductors. IEEE Journal of Solid-State Circuits, 43(5), 1156–1163.

Lu, K., Wang, F., & Horng, T. (2013). Ultralow phase noise and wideband CMOS VCO using symmetrical body-bias PMOS varactors. IEEE Microwave and Wireless Components Letters, 23(2), 90–92.

Cazzorla, A., Farinelli, P., Urbani, L., Cacciamani, F., Pelliccia, L., Sorrentino, R., & Margesin, B. (2017). MEMS-based LC tank with extended tuning range for low phase-noise VCO. International Journal of Microwave and Wireless Technologies, 9(2), 249–258. https://doi.org/10.1017/S1759078715001579

Mansour, I., et al. (2020). Analysis and implementation of high-Q CT inductor for compact and wide-tuning range Ku-band VCO. IEEE Microwave Wireless Components Letter, 30(8), 802–805.

Mansour I, Aboualalaa M, Allam A, Abdel-Rahman AB, Abo-Zahhad M, Pokharel RK, (2018). Design of multi-layers DGS resonator for phase noise improvement of K-band VCOs in 0.18 μm CMOS technology. In: Proceedings of IEEE 61st International Midwest Symposium on Circuits Systems (MWSCAS). Windsor, ON, Canada, pp. 178–181

Mansour I et al. (2018). 70 % improvement in Q-factor of spiral inductor and its application in switched K-band VCO using 0.18 μm CMOS technology. In: Proc. Asia–Pacific Microw. Conf. (APMC). Kyoto, Japan, pp. 1133–1135

Zito, D., & Pepe, D. (2010). LC-active VCO for CMOS RF transceivers. International Journal of Circuit Theory and Applications, 38, 69–84.

Zito, D., Pepe, D., & Fonte, A. (2012). 13 GHz CMOS Active Inductor LC VCO. IEEE Microwave and Wireless Components Letters, 22(3), 138–140.

Mansour, M., Zekry, A., Ali, M. K., & Shawkey, H. (2020). A reconfigurable class-ab/f power amplifier for 0.1–4.2 GHz multistandard applications. Circuits, Systems, and Signal Processing, 40(3), 1111–1126. https://doi.org/10.1007/s00034-020-01525-4

Kim, S., Seo, D., Kim, J., Song, R., & Kim, B. (2018). Compact CMOS LiT VCO achieving 198.6 dBc/Hz FoMA. Electronics Letters, 54(3), 175–177.

Wang, T. P., & Wang, S. Y. (2015). Frequency-tuning negative-conductance boosted structure and applications for low-voltage low-power wide-tuning-range VCO. IEEE Transaction Very Large Scale Integration System., 23, 1137–1144.

Mansour, M., & Mansour, I. (2021). Triple bands class-C voltage-controlled power oscillator based on high-quality factor asymmtery inductor. Microelectronics Journal, 110, 105251.

Wang, F., & Wang, H. (2018). A noise circulating cross-coupled VCO with a 195.6dBc, Hz FoM and 50kHz 1, f3 noise corner. IEEE Custom Integrated Circuits Conference, 2018, 1–4.

Hsu, M., Chen, P., & Lee, Y. (2014). Design of 5 GHz low-power CMOS LC VCO based on complementary cross-coupled topology with modified tail current-shaping technique. International Journal of Microwave and Wireless Technologies, 6(6), 573–580. https://doi.org/10.1017/S1759078714000300

Hegazi, E., Sjoland, H., & Abidi, A. A. (2001). A filtering technique to lower LC oscillator phase noise. IEEE Journal of Solid-State Circuits, 36(12), 1921–1930. https://doi.org/10.1109/4.972142

Mansour, M., & Mansour, I. (2022). Three‐stage transformer‐coupled CMOS power amplifier for millimeter‐wave applications using 130 nm CMOS technology. International Journal of Circuit Theory and Applications, 50(10), 3567–3583. https://doi.org/10.1002/cta.3363

Hajimiri, A., & Lee, T. H. (1998). A general theory of phase noise in electrical oscillators. IEEE Journal of Solid-State Circuits, 33(2), 179–194. https://doi.org/10.1109/4.658619

Funding

Open access funding provided by The Science, Technology & Innovation Funding Authority (STDF) in cooperation with The Egyptian Knowledge Bank (EKB).

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Mansour, I., Mansour, M. 166% frequency tuning range power VCO using high-quality off-chip inductor. Analog Integr Circ Sig Process 114, 431–438 (2023). https://doi.org/10.1007/s10470-023-02141-3

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-023-02141-3