Abstract

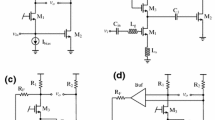

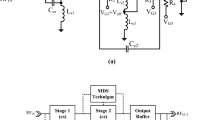

In this paper, an on-chip planar balun and a common-gate (CG) low-noise amplifier (LNA) employing a multiple feedback structure is presented. The planar interleaved balun is characterized through electromagnetic (EM) simulations using Advanced Design System (ADS) Momentum. A new lumped circuit model of the balun is created for use in transient simulations. CG-LNA employs \(g_m\)-boosting and positive feedback structures to reduce the high noise figure (NF) of the traditional CG-LNA. The combined blocks achieve a minimum NF of 5.5 dB and an AC gain of 18.54 dB in post-layout simulations. The balun and LNA blocks are designed in a 180 nm CMOS technology using 1Poly6Metal (1P6M) layers. Simulation results are presented for post-layout and schematic cases. The total power consumption of the the circuit is 2.55 mW with 1.8 V nominal power supply. Furthermore, a time-domain UWB pulse simulation is done to confirm the operation of the blocks combined. These can be used to form the initial stages of an UWB receiver.

Similar content being viewed by others

Data Availability Statement

Data sharing is not applicable to this article as no datasets were generated or analysed during the current study.

Code availability

Not applicable.

References

Chang, S., & Shin, H. (2008). A compact circuit model of five-port transformer balun for CMOS RF integrated circuits. IEICE Transactions on Electronics, E91–C, 10. https://doi.org/10.1093/ietele/e91-c.10.1709.

Long, J. R. (2000). Monolithic transformers for silicon RF IC design. IEEE Journal of Solid-State Circuits, 35(9), 1368–1382. https://doi.org/10.1109/4.868049.

Kapur, S., Long, D. E., Frye, R. C., Chen, Y., Cho, M., Chang, H., et al. (2007). Synthesis of optimal on-chip Baluns. IEEE Custom Integrated Circuits Conference, 2007, 507–510. https://doi.org/10.1109/CICC.2007.4405782.

Zhuo, W., Li, X., Shekhar, S., Embabi, S. H. K., de Gyvez, J. P., Allstot, D. J., & Sanchez-Sinencio, E. (2005). A capacitor cross-coupled common-gate low-noise amplifier. IEEE Transactions on Circuits and Systems II: Express Briefs, 52(12), 875–879. https://doi.org/10.1109/TCSII.2005.853966

Rotella, M., Cismaru, C., Tkachenko, Y., Cheng, Yuhua, & Zampardi, J. (2006). Characterization, design, modeling, and model validation of silicon-wafer M:N Balun components under matched and unmatched conditions. IEEE Journal of Solid-State Circuits, 41(5), 1201–1209. https://doi.org/10.1109/JSSC.2006.872736.

El-Gharniti, O., Kerherve, E., & Begueret, J. (2007). Modeling and characterization of on-chip transformers for silicon RFIC. IEEE Transactions on Microwave Theory and Techniques, 55(4), 607–615. https://doi.org/10.1109/TMTT.2007.893647.

Mohan, S.S., Yue, C.P., del Mar Hershenson, M., Wong, S.S., & Lee, T.H. (1998). “Modeling and characterization of on-chip transformers,” In International Electron Devices Meeting 1998. Technical Digest (Cat. No.98CH36217), pp. 531–534. https://doi.org/10.1109/IEDM.1998.746414.

Gao, W., Jiao, C., Liu, T., & Yu, Z. (2006). Scalable compact circuit model for differential spiral transformers in CMOS RFICS. IEEE Transactions on Electron Devices, 53(9), 2187–2194. https://doi.org/10.1109/TED.2006.880230.

Yue, C. P., & Wong, S. S. (2000). Physical modeling of spiral inductors on silicon. IEEE Transactions on Electron Devices, 47(3), 560–568. https://doi.org/10.1109/16.824729

Kamgaing, T., Myers, T., Petras, M. & Miller, M. (2002).Modeling of frequency dependent losses in two-port and three-port inductors on silicon. In 2002 IEEE Radio Frequency Integrated Circuits (RFIC) Symposium. Digest of Papers (Cat. No.02CH37280), pp. 307–310. https://doi.org/10.1109/RFIC.2002.1012055.

Cao, Y., Groves, R. A., Huang, X., Zamdmer, N. D., Plouchart, J., Wachnik, R. A., et al. (2003). Frequency-independent equivalent-circuit model for on-chip spiral inductors. IEEE Journal of Solid-State Circuits, 38(3), 419–426. https://doi.org/10.1109/JSSC.2002.808285.

Huang, K.-Y., Hsu, C.-J. & Leu L.-Y. (2005) . Modeling methodology of integrated five-port Balun using two-port rf measurement. In 2005 IEEE radio frequency integrated circuits (RFIC) symposium - digest of papers (pp. 295–298). 10.1109/RFIC.2005.1489789.

Niknejad, A. M., & Meyer, R. G. (1998). Analysis, design, and optimization of spiral inductors and transformers for SI RF ICS. IEEE Journal of Solid-State Circuits, 33(10), 1470–1481. https://doi.org/10.1109/4.720393.

Sobhy, E. A., Helmy, A. A., Hoyos, S., Entesari, K., & Sanchez-Sinencio, E. (2011). A 2.8-mw sub-2-db noise-figure inductorless wideband CMOS LNA employing multiple feedback. IEEE Transactions on Microwave Theory and Techniques, 59(12), 3154–3161. https://doi.org/10.1109/TMTT.2011.2169081.

Saleh, S.A., Ortmanns, M., & Manoli, Y. (2008). A low-power differential common-gate LNA. In 2008 51st midwest symposium on circuits and systems (pp. 137–140). https://doi.org/10.1109/MWSCAS.2008.4616755.

Han, T., Li, Z., & Tian, M. (2020). An inductor-less CMOS broadband balun gm-boosting LNA exploiting noise cancellation techniques. Analog Integrated Circuits and Signal Processing, 104, 06. https://doi.org/10.1007/s10470-020-01665-2.

Chaghaei, J., Jalali, A., & Meghdadi, M. (2019). A wideband inductorless lna employing active complementary current-reuse balun, In 2019 27th Iranian Conference on Electrical Engineering (ICEE) (pp. 108–112). https://doi.org/10.1109/IranianCEE.2019.8786474.

Wang, H., Zhang, L., & Yu, Z. (2010). A wideband inductorless lna with local feedback and noise cancelling for low-power low-voltage applications. IEEE Transactions on Circuits and Systems I: Regular Papers, 57(8), 1993–2005. https://doi.org/10.1109/TCSI.2010.2042997

Zhang, K., Li, W., Ye, F., Li, N., & Ren, J. (2011) A 0.13-\(\mu \text{m}\) cmos 0.8–10.6ghz low noise amplifier with active balun for multi-standard applications. In 2011 Asia Pacific Conference on Postgraduate Research in Microelectronics Electronics (pp. 123–126). https://doi.org/10.1109/PrimeAsia.2011.6075086.

Chehrazi, S., Mirzaei, A., Bagheri, R., & Abidi, A.A. (2005). A 6.5 ghz wideband cmos low noise amplifier for multi-band use. In Proceedings of the IEEE 2005 Custom Integrated Circuits Conference, 2005. (pp. 801–804). https://doi.org/10.1109/CICC.2005.1568790.

Funding

The authors did not receive support from any organization for the submitted work.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors have no relevant financial or non-financial interests to disclose.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Aydoğdu, A., Tomar, D., Batur, O.Z. et al. A 2.55-mW on-chip passive balun-LNA in 180-nm CMOS. Analog Integr Circ Sig Process 111, 223–234 (2022). https://doi.org/10.1007/s10470-022-01997-1

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-022-01997-1