Abstract

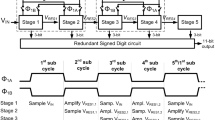

A 4- bit reusable stage based asynchronous binary search analog to digital converter (ADC) with a smart switching network, and reduced comparator count is presented in this paper. The proposed ADC uses asynchronous logic to activate comparators sequentially while switching network is used to provide reference voltages for selected comparators. In the extended version, the 6-bit ADC is designed using only \((\mathrm{N}+1)\) comparators instead of \(2^{(N)}-1\) and (2N − 1) as used in conventional approach. The simulation results of 4 bit ADC confirms that the design achieves conversion speed of 500 MSPS with power consumption of 1.63 mW when operated on 1.8 V supply with SNR, SFDR and ENOB as 22.5 dB, 32.4 dBc and 3.8 bits while for 6 bit the SNR, SFDR and ENOB are 34.96 dB, 42 dBc and 5.56 bits respectively with 0.35 mW of power dissipation. The Walden FOM for proposed 4 bit and 6 bit ADC design are 0.21 pJ/conversion-step and 24.7 fJ/conversion-step respectively.

Similar content being viewed by others

References

Xiaodan, Z., Xiaoyuan, X., Libin, Y., & Yong, L. (2009). A 1-V 450-nW fully integrated programmable biomedical sensor interface chip. IEEE Journal Solid-State Circuits, 44, 1067–1077.

Han, X., Fan, H., Wei, Q., & Yang, H. (2013). A high SFDR 6-bit 20-MS/s SAR ADC based on time-domain comparator. Journal of Semiconductors, 34, 085008.

Lin, Y.-Z., Chang, S.-J., Liu, Y.-T., et al. (2010). An asynchronous binary-search ADC architecture with a reduced comparator count. IEEE Transactions on Circuits and Systems I, 57, 1829–1837.

Xue, H., Hua, F., Qi, W., & Huazhong, Y. (2013). A high SFDR 6-bit 20-MS/s SAR ADC based on time-domain comparator. Journal of Semiconductors, 34, 085008.

Chung, Y. H., & Chiang, M. S. (2019). A 12-bit synchronous-SAR ADC for IoT applications. In IEEE international symposium on circuits and systems (ISCAS) (pp. 1–5).

Njinowa, M. S., Bui, H. T., & Boyer, F. R. (2013). Design of low power 4-bit flash ADC based on standard cells. In IEEE 11th international new circuits and systems conference (pp. 1–4).

Yung, C., & Min, C. (2019). A 12-bit synchronous-SAR ADC for IoT applications. In IEEE international symposium on circuits and systems (ISCAS) (pp. 1–5).

Chih-Yuan, K., Chun-Po, H., & Chia-Chuan, L. (2018). A low energy consumption 10-bit 100kS/s SAR ADC with timing control adaptive window. In IEEE international symposium on circuits and systems (ISCAS) (pp. pp. 1–4).

Shubin, L., Yi, S., & Zhangming, Z. (2016). A 12-bit 10 MS/s SAR ADC with high linearity and energy-efficient switching. IEEE Transactions on Circuits and Systems I, 63, 1616–1627.

Si, W., Chio, U. F., & Chi, C., et.al. (2011). A 4.8-bit ENOB 5-bit 500MS/s binary-search ADC with minimized number of comparators. In IEEE Asian solid-state circuits conference 2011 (pp. 73–76).

Zhangming, Z., & Yuhua, L. (2015). A 0.6-V 38-nW 9.4-ENOB 20-kS/s SAR ADC in 0.18-\(\mu\)m CMOS for Medical Implant Devices. IEEE Transactions on Circuits and Systems, 62, 2167–2176.

Chung, Y., & Hsu, Y. (2019). A 12-Bit 100-MS/s subrange SAR ADC with a foreground offset tracking calibration scheme. IEEE Transactions on Circuits and Systems II, 66, 1094–1098.

Ashima, G., Anil, S., & Alpana, A. (2018). Highly-digital voltage scalable 4-bit flash ADC. IET Circuits, Devices & Systems, 13, 91–97.

Sunghyun, P., & Yorgos, P., et al. (2007). A 4-GS/s 4-bit flash ADC in 0.18-m CMOS . IEEE Journal of Solid state and circuits.

Mohammed, C., & Mohammed, M., et.al. (2013). A 4-bit, 1.6 GS/s low power flash ADC, based on offset calibration and segmentation. IEEE Transactions on Circuits and Systems I.

Acknowledgements

The author would like to thank MeitY (Ministry of Electronics and Information Technology, Govt. of India) for providing support under SMDP-C2SD (Special Manpower Development Program for Chips to System Design) project.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Dipti, Singh, S.V., Joshi, R. et al. A reusable stage based reduced comparator count binary search ADC. Analog Integr Circ Sig Process 105, 33–43 (2020). https://doi.org/10.1007/s10470-020-01686-x

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-020-01686-x