Abstract

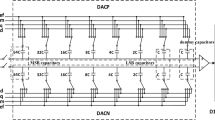

In this paper a 4-bit 720 MHz low-power successive approximation register ADC is simulated in a 0.18 µm digital CMOS process. By using both of the 2-bit/step and time-interleaved techniques, a high sampling frequency is obtained. To simplify the SAR ADC in low-bit applications, the analog switches are eliminated and replaced with inherent digital switches of SAR logics. The power supply, resolution, sampling frequency, SNDR, and power consumption of the proposed SAR ADC are 1.8 V, 4-bit, 720 MHz, 22.1 dB, and 10 mW.

Similar content being viewed by others

References

Giannini, V., Nuzzo, P., Chironi, V., Baschirotto, A., Van der Plas, G., & Craninckx, J. (2008). An 820 μW 9b 40 MS/s noise-tolerant dynamic-SAR ADC in 90 nm digital CMOS. In IEEE International Solid-State Circuits Conference (ISSCC). Digest of Technical Papers (pp. 238-239).

Ginsburg, B. P., & Chandrakasan, A. P. (2008). Highly interleaved 5b 250 MS/s ADC with redundant channels in 65 nm CMOS. In IEEE International Solid-State Circuits Conference (ISSCC). Digest of Technical Papers (pp. 240–241).

Van Elzakker, M., Van Tuijl, E., Geraedts, P., Schinkel, D,. Klumperink, E., & Nauta, B. (2008). A 1.9 μW 4.4fJ/conversion-step 10b 1 MS/s charge-redistribution ADC. In IEEE International Solid-State Circuits Conference (ISSCC). Digest of Technical Papers (pp. 244–245).

Agnes, A., Bonizzoni, E., Malcovati, P., & Maloberti, F. (2008). A 9.4-ENOB 1 V 3.8 μW 100kS/s SAR ADC with time-domain comparator. In IEEE International Solid-State Circuits Conference (ISSCC). Digest of Technical Papers (pp. 246–247).

Zhu, Zh., Xiao, Y., Xu, L., Ding, H., & Yang, Y. (2013). An 8/10 bit 200/100 MS/s configurable asynchronous SAR ADC. In Analog Integrated Circuits Signal Processing (Vol. 77, pp. 249–255).

Liu, Ch.-Ch., Chang, S.-J., Huang, G.-Y., Lin, Y.-Z., & Huang, Ch.-M. (2010). A 1 V 11fJ/conversion-step 10bit 10 MS/s asynchronous SAR ADC in 0.18 μm CMOS. In Symposium on VLSI Circuits. Digest of Technical Papers (pp. 241–242).

Craninckx, J., & Van der plas, G. (2007). A 65fJ/conversion-step 0-to-50 MS/s 0-to-0.7mW 9b charge-sharing SAR ADC in 90 nm Digital CMOS. In IEEE International Solid-State Circuits Conference (ISSCC). Digest of Technical Papers (pp. 246–247).

Ginsburg, B. P., & Chandrakasan, A. P. (2005). An energy-efficient charge recycling approach for a SAR converter with capacitive DAC. In IEEE International Symposium on Circuits and Systems (ISCAS) (Vol. 1, pp. 184-187).

Talekar, S. G., Ramasamy, S., Lakshminarayanan, G., & Venkataramani, B. (2009). 500 MS/s 4-b time interleaved SAR ADC using novel DAC architecture. In IEEE 1st Asia Symposium on Quality Electronic Design (ASQED) (pp. 292–297).

Cao, Zh, Yan, Sh, & Li, Y. (2009). A 32 mW 1.25 GS/s 6b 2b/Step SAR ADC in 0.13 µm CMOS. IEEE Journal of Solid-State Circuits, 44(3), 862–873.

Draxelmayr, D. (2004). A 6b 600 MHz 10 mW ADC array in digital 90 nm CMOS. In IEEE International Solid-State Circuits Conference (ISSCC). Digest of Technical Papers (Vol. 1, pp. 264–527).

Hong, H-Ch., & Lee, G.-M. (2007). A 65-fJ/conversion-step 0.9-V 200-kS/s rail-to-rail 8-bit successive approximation ADC. IEEE Journal of Solid-State Circuits, 42(10), 2161–2168.

Bichan, M., & Carusone, A.C. (2009). The effect of redundancy on mismatch-induced offset and random noise in a dynamic comparator. IEEE Ph.D. Research in Microelectronics and Electronics (PRIME) (pp. 180–183).

Neshani, S., & Azhari, J. (2013). A Low-power low-voltage 6-bit 1.33 GS/s fully MCML all nmos FLASH ADC without a front-end T/H. Journal of Circuits, Systems, and Computers. doi:10.1142/S0218126613500746.

Dang, H., Sawan, M., & Savaria, Y. (2005). A novel approach for implementing ultra-high speed flash ADC using MCML circuits. In IEEE International Symposium on Circuits and Systems (ISCAS) (Vol. 6, pp. 6158–6161).

Alpman, E., Lakdawala, H., Carley, L.R., & Soumyanath, K. (2009). A 1.1 V 50 mW 2.5 GS/s 7b time-interleaved C-2C SAR ADC in 45 nm LP digital CMOS. In IEEE International Solid-State Circuits Conference (ISSCC). Digest of Technical Papers (pp. 76–77,77a).

Harpe, P. J. A., Zhou, C., Bi, Y., van der Meijs, N. P., Wang, X., Philips, K., et al. (2011). A 26 μW 8 bit 10 MS/s asynchronous SAR ADC for low energy radios. IEEE Journal of Solid-State Circuits, 46(7), 1585–1595.

Talekar, S. G., Ramasamy, S., Lakshminarayanan, G., & Venkataramani, B. (2009). A low power 700MSPS 4bit time interleaved SAR ADC in 0.18 µm CMOS. In IEEE Region 10 Conference (TENCON) (pp. 1–5).

Gu, Ch., Zhao, Y., & Hong, Zh. (2011). A 4GS/s 3b two-way time-interleaved ADC in 0.13um CMOS. In IEEE 9th International Conference on ASIC (ASICON) (pp. 1002–1005).

Kopparrthy, S. P., Makwana, I., & Gupta, A. (2012). Asynchronous 8-bit pipelined ADC for self-triggered sensor based applications. In Asia Pacific Conference on Postgraduate Research in Microelectronics and Electronics (Prime Asia) (pp. 205–210).

Cai, X., Li, F., Li, W., Zhang, Ch., & Wang, Zh. (2010). A 12bit 100MSps pipelined ADC without calibration. In IEEE 3rd International Congress on Image and Signal Processing (CISP) (pp. 3547–3552).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Damghanian, M., Shamsi, H. Combination of DAC switches and SAR logics in a 720 MS/s low-bit successive approximation ADC. Analog Integr Circ Sig Process 80, 263–272 (2014). https://doi.org/10.1007/s10470-014-0337-6

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-014-0337-6