Abstract

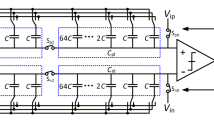

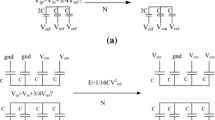

In this paper, a new highly energy-efficient switching scheme is presented for successive approximation register analogue-to-digital converters. The proposed method applies a four-level switching strategy to reduce the switching energy to one of the lowest levels reported yet. Also, the controller of this method has low complexity compared to the other procedures. In contrast to the conventional scheme, the switching energy is reduced by 97.85% and the total capacitor size is decreased by 87.5%. Moreover, under the condition of the 50-times Monte-Carlo simulation for capacitor mismatch and reference voltages mismatch (Vref/2 and Vref/4), the mean value of the effective number of bit (ENOB) with standard deviation of 1% is 7.4 and 7.33 bits, respectively, while the ENOB value without any mismatches is 7.51 bits with sampling frequency of 1MS/s. It is noteworthy that the Monte-Carlo simulations are performed in Spectre simulator in Cadence with consideration all of non-idealities such as transistor charge injection, clock jitter and clock feedthrough. In other words, accurate and electrical simulation is performed instead of behavioral simulation. As a result, the bar graph of the ENOB values is plotted in MATLAB. In addition, the maximum and minimum of DNL/INL values are between − 0.3/0.3 LSB.

Similar content being viewed by others

References

S. Brenna, A.G. Bonfanti, A. Abba, F. Caponio, A.L. Lacaita, Analysis and optimization of a SAR ADC with attenuation capacitor, in 37th International Convention on Information and Communication Technology, Electronics and Microelectronics (MIPRO) (2014)

Y.S. Chen, Y.Q. Zhuang, H.L. Tang, A 99.8% energy-reduced two-stage mixed switching scheme for SAR ADC without reset energy. Circuits Syst. Signal Process. 38, 5426–5447 (2019)

W. Gao, S. Emaminejad, H.Y.Y. Nyein, S. Challa, K. Chen, A. Peck, H.M. Fahad, H. Ota, H. Shiraki, D. Kiriya, Fully integrated wearable sensor arrays for multiplexed in situ perspiration analysis. Nature 529, 509–514 (2016)

B. Ghanavati, E. Abiri, A. Keyhani, M.R. Salehi, A. Sanyal, An energy efficient SAR ADC with lowest total switching energy consumption. Analog Integr. Circuits Signal Process. 97, 123–133 (2018)

B. Ghanavati, E. Abiri, M.R. Salehi, A. Keyhani, A. Sanyal, LSB split capacitor SAR ADC with 99.2% switching energy reduction. Analog Integr. Circuits Signal Process. 93, 375–382 (2017)

W. Guo, Z. Zhu, A 0.3 V 8-bit 8.9 fJ/con.-step SAR ADC with sub-DAC merged switching for biosensors. Microelectron. J. 68, 44–54 (2017)

L. Jian, R.X. Ding, S.B. Liu, Z.M. Zhu, A highly energy-efficient, highly area-efficient capacitance multiplexing switching scheme for SAR ADC. Analog Integr. Circuits Signal Process. 96, 207–215 (2018)

Z. Jinqiang, M. Niansong, Z. Zhaofeng, M. Lingqin, Vaq-based tri-level switching scheme for SAR ADC. Electron. Lett. 54, 66–68 (2018)

T. Kim, S. Kim, A 12.1 mW, 60 dB SNR, 8-channel beamforming embedded SAR ADC for ultrasound imaging systems, in IEEE Asian Solid-State Circuits Conference (A-SSCC) (2017), pp. 141–144

C.C. Liu, S.J. Chang, G.Y. Huang, Y.Z. Lin, A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. J. Solid State Circuits 45, 731–740 (2010)

S. Liu, Y. Shen, J. Wang, Z. Zhu, A 10-bit self-clocked SAR ADC with enhanced energy efficiency for multi-sensor applications. IEEE Sens. J. 10, 4223–4233 (2018)

D.J. Moni, S.M. Jose, Design of 10b SAR ADC for biomedical applications, in International Conference on Electronics and Communication Systems (ICECS) (2015), pp. 276–281

D. Osipov, S. Paul, Two-step reset method for energy-efficient SAR ADC switching schemes. Electron. Lett. 52, 816–817 (2016)

C.S. Ragit, S. Badjate, Design of up-down counter as SAR logic for high speed SAR ADC used in health care system, in Conference on Advances in Signal Processing (CASP) (2016), pp. 465–468

E. Rahimi, M. Yavari, Low-efficient high-accuracy switching method for SAR ADCs. Electron. Lett. 50, 499–501 (2014)

S. Ur Rehman, A.M. Kamboh, A CMOS micro-power and area efficient neural recording and stimulation front-end for biomedical applications. Circuits Syst. Signal Process. 34, 1725–1746 (2015)

A. Sanyal, N. Sun, SAR ADC architecture with 98% reduction in switching energy over conventional scheme. Electron. Lett. 49, 248–250 (2013)

E.V. Tuijl, P. Geraedts, D. Schinkel, E. Klumperink, B. Nauta, M. Van Elzakker, A 1.9 μW 4.4 fJ/Conversion-step 10b 1 ms/s Charge-Redistribution ADC. ISSCC Dig. Tech. Papers (2008)

W.L. Wu, S.W. Sin, U. Seng-Pan, R.P. Martins, A 10-bit SAR ADC with two redundant decisions and splitted-MSB-cap DAC array, in IEEE Asia Pacific Conference on Circuits and Systems (2012), pp. 268–271

L. Xie, J. Su, J. Liu, G. Wen, Energy-efficient capacitor-splitting DAC scheme with high accuracy for SAR ADC. Electron. Lett. 51, 460–462 (2015)

K. Yadav, P. Patra, A. Dutta, A 43-nW 10-bit 1 ks/s SAR ADC in 180 nm CMOS for biomedical applications, in IEEE Asia Pacific Conference on Postgraduate Research in Microelectronics and Electronics (PrimeAsia) (2015), pp. 21–25

C. Yuan, Y. Lam, Low-energy and area-efficient tri-level switching scheme for SAR ADC. Electron. Lett. 48, 482–483 (2012)

Y. Zhang, Y. Li, Z. Zhu, A charge-sharing switching scheme for SAR ADCs in biomedical applications. Microelectron. J. 75, 128–136 (2018)

X. Zhong, B. Zhang, A. Bermak, C.Y. Tsui, M.K. Law, A low-power compression-based CMOS image sensor with microshift-guided SAR ADC, in IEEE Transactions on Circuits and Systems II Exp. Briefs, vol. 65, pp. 1350–1354 (2018)

R. Zhou, S. Liu, J. Liu, R. Ding, J. Wang, S. Huang, Z. Zhu, A 96.88% area-saving and 99.72% energy-reduction switching scheme for SAR ADC with a novel two-step quantisation technique. Analog Integr. Circuits Signal Process. 100, 205–213 (2019)

Y. Zhu, C.H. Chan, U.F. Chio, S.W. Sin, R.P. Martins, F. Maloberti, U. Seng-Pan, A 10-bit 100-MS/s reference-free SAR ADC in 90 nm CMOS. J. Solid State Circuits 45, 1111–1121 (2010)

Y. Zhu, U.F. Chio, H.G. Wei, S.W. Sin, S.P. U, R.P. Martins, Linearity analysis on a series-split capacitor array for high-speed SAR ADCs. in 51th Midwest Symposium on Circuits and Systems, pp. 922–925 (2008)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Sotoudeh, M., Rezaei, F. A Four-Level Switching Scheme for SAR ADCs with 87.5% Area Saving and 97.85% Energy-Reduction. Circuits Syst Signal Process 39, 4792–4809 (2020). https://doi.org/10.1007/s00034-020-01405-x

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-020-01405-x