Abstract

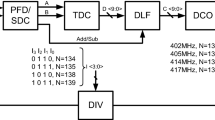

A low power phase locked loop (PLL) based transmitter for wireless sensor application is presented in this paper. The transmitter adopts two-point modulation architecture in high-pass and low-pass paths of PLL; it modulates the divide ratio through sigma-delta modulator and voltage controlled oscillator (VCO) frequency tuning port simultaneously. An interleave-biased varactor pair is used to linearize the frequency tuning curve of the VCO. Besides, to achieve the desired frequency deviation of 500 kHz, we use a capacitance desensitization technique through combined parallel and serial capacitances with tuning varactors. This topology does not need the minimum size varactor, which is sensitive to process variation and mismatch. Implemented in standard 0.18-μm CMOS process, the transmitter achieves a 5.2 % FSK error for 2 Mbps data rate without using any auto-calibration circuit, consuming 7.8 mW power. Loop filter and crystal are the only off-chip components.

Similar content being viewed by others

References

Raja, M. K., Chen X. S., Yan, D. L., Zhao, B., Yeung, B. C. & Yuan X. J. (2010) A 18 mW Tx, 22 mW Rx transceiver for 2.45 GHz IEEE 802.15.4 WPAN in 0.18-μm CMOS, In Proceedings of IEEE A-SSCC, (pp. 1–4).

Yu, R., Yeo, T. T., Tan, K. H., Mou, S. X., Cui, Y. K., Wang, H. F., Yap, H. S., Ting, E., & Itoh, M. (2009) A 5.5 mA 2.4-GHz two-point modulation Zigbee transmitter with modulation gain calibration, In Proceedings of IEEE CICC, (pp. 375–378).

Perrott, M. H., Tewksbury, T. L, III, & Sodini, C. G. (1997). A 27-mW CMOS fractional- synthesizer using digital compensation for 2.5-Mb/s GFSK modulation. IEEE Journal of Solid-State Circuits, 32(12), 2048–2060.

Kim, H., Kim, S. Y., & Lee, K.-Y. (2013). Low power FSK transmitter using all-digital PLL for IEEE 802.15.4g application. Analog Integrated Circuits and Signal Processing, 74, 599–612.

Cook, B. W., Berny, A. D., Molnar, A., Lanzisera, S., & Pister, K. S. J. (2006). Low-power 2.4-GHz transceiver with passive RX front-end and 400-mV supply. IEEE Journal of Solid-State Circuits, 41, 2757–2766.

Xu, L. G., Lindfors, S., Stadius, K., & Ryynanen, J. (2010). A 2.4-GHz low-power all-digital phase-locked loop. IEEE Journal of Solid-State Circuits, 45, 1513–1521.

Lee, S., Lee, J., Park, H., Lee, K.-Y., & Nam, S. (2010). Self-calibrated two-point delta-sigma modulation technique for RF transmitters. IEEE Transactions on Microwave Theory and Techniques, 58(7), 1748–1757.

Notor, J., Caviglia, A. & Levy, G. (2003) CMOS RFIC architectures for IEEE 802.15.4 networks, White Paper.

Peng, K. C., Huang, C. H., Li, C. J., & Horng, T. S. (2004). High-performance frequency-hopping transmitters using two-point delta-sigma modulation. IEEE Transactions on Microwave Theory and Techniques, 52, 2529–2535.

Vaucher, C. S., Ferencic, I., Locher, M., Sedvallson, S., Voegeli, U., & Wang, Z. (2000). A family of low-power truly modular programmable dividers in standard 0.35-µm CMOS technology. IEEE J. Solid-State Circuits, 35(7), 1039–1045.

Lin, T. H., Ti, C. L., & Liu, Y. H. (2009). Dynamic current-matching charge pump and gated-offset linearization technique for delta-sigma fractional-N PLLs. IEEE Transactions on Circuits and Systems I: Regular Papers, 56, 877–885.

Bloom, I., & Nemirovsky, Y. (1991). 1/f noise reduction of metal-oxide-semiconductor transistors by cycling from inversion to accumulation. Applied Physics Letters, 58(15), 1664–1666.

Jia, F., Diao, S. X., Zhang, X. J., Fu, Z. Q., & Lin, F. J. (2012). A digitally controlled power amplifier with neutralization capacitors for Zigbee™ applications. Journal of Semiconductors, 33(12), 125002.

Yu, S. A., & Kinget, P. (2009). A 0.65-V 2.5-GHz fractional-N synthesizer with two-point 2-Mb/s GFSK data modulation. IEEE Journal of Solid-State Circuits, 44, 2411–2425.

Acknowledgments

This work was supported by the USTC and IMECAS jointed lab Micro-Nano electronic System Integration R&D (MESIC) under MESIC Grant No. 2100230011. The authors wish to thank Jingye Sun, Wei Hu, Chuankui Shen for circuits discussion and FPGA test code implementation. We appreciate the Information Science and Technology center of USTC for CAD support and Agilent for measurement support.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Wang, C., Diao, S., Chen, N. et al. A calibration-less low error two-point modulation transmitter for 802.15.4 application. Analog Integr Circ Sig Process 80, 273–282 (2014). https://doi.org/10.1007/s10470-014-0329-6

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-014-0329-6