Abstract

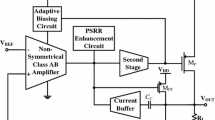

A low-dropout regulator with a wide-bandwidth feedforward supply noise cancellation path for enhancing supply noise rejection at middle-to-high frequency is presented in this paper. This idea has been realized by a bandpass filter and a signal-nulling technique with the help of a voltage buffer. For the PSR filter design, the total on-chip capacitance is about 18.75 pF. This circuit has been implemented in a 0.35 µm CMOS process and occupies an active chip area of 0.062 mm2. From the experimental results, the proposed LDO can operate with nominal dropout voltage of 200 mV at maximum load of 25 mA and quiescent current of 26 μA. It achieves a power-supply rejection better than −59 dB up to 10 MHz with a 4 μF output capacitor.

Similar content being viewed by others

References

Patounakis, G., Li, Y. W., & Shepard, K. (2004). A fully integrated on-chip DC–DC conversion and power management system. IEEE Journal of Solid-State Circuits, 39(3), 443–451.

M. D. Mulligan, B. Broach, and T. H. Lee, “A 3 MHz low-voltage buck converter with improved light load efficiency,” IEEE International Solid-State Circuits Conference, pp. 528–529, Feb. 2007.

Rincon-Mora, G. A., & Allen, P. E. (1998). A low-voltage, low quiescent current, low drop-out regulator. IEEE Journal of Solid-State Circuits, 33(1), 36–44.

Leung, K. N., & Mok, P. K. T. (2003). A capacitor-free CMOS low-dropout regulator with damping-factor-control frequency compensation. IEEE Journal of Solid-State Circuits, 38(10), 1691–1702.

V. Gupta and G. A. Rincon-Mora, “A low dropout, CMOS regulator with high PSR over wideband frequencies,” Proceedings of the International Symposium on Circuits and Systems, May 23–26, 2005, vol. 5, pp. 4245–4248.

S. K. Hoon, S. Chen. F. Maloberti, J. Chen, and B. Aravind, “A low noise, high power supply rejection low dropout regulator for wireless system-on-chip applications,” Proceedings of IEEE Custom Integrated Circuits Conference, pp. 754–757, Sep. 2005.

Lin, Chia-Hsiang, Chen, Ke-Horng, & Huang, Hong-Wei. (2009). Low-dropout regulators with adaptive reference control and dynamic push–pull techniques for enhancing transient performance. IEEE Transactions on Power Electronics, 24(4), 1016–1022.

Chu, Yen-Chia, & Chang-Chien, Le-Ren. (2013). Digitally controlled low-dropout regulator with fast-Transient and autotuning algorithms. IEEE Transactions on Power Electronics, 28(9), 4308–4317.

C. Zhan and W. H. Ki, “Output-capacitor-free adaptively biased low-dropout regulator for system-on-chips,” IEEE Transactions on Circuits and Systems, vol. 57, no. 5, pp. 1017–1028, May. 2010.

K.Wong and D. Evans, “A 150 mA low noise, high PSRR low-dropout linear regulator in 0.13 μm technology for RF SoC applications,” Proceedings.of the European. Solid-State Circuits Conference (ESSCIRC), pp. 532–535, Sep. 2006.

V. Gupta and G. A. Rincon-Mora, “A 5 mA 0.6 μm CMOS miller- compensated LDO regulator with −27 dB worst-case power-supply rejection using 60 pF of on-chip capacitance,” Proceedings of the IEEE ISSCC Digital. Technology Papers, pp. 520–521, Feb. 2007.

Ingino, J. M., & von Kaenel, V. R. (2001). A 4-GHz clock system for a high performance system-on-a-chip design. IEEE Journal of Solid-State Circuits, 36(11), 1693–1698.

S. Heng and Cong-Kha Pham, “A low-power high-PSRR low-dropout regulator with bulk-gate controlled circuit,” IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 57, no. 4, pp. 245–249, Apr. 2010.

Patel, A. P., & Rincon-Mora, G. A. (2010). High power-supply-rejection (PSR) current-mode low-dropout (LDO) regulator. IEEE Transactions on Circuits and Systems II, 57(11), 868–873.

El-Nozahi, M., Amer, A., Torres, J., Entesari, K., & Sanchez-Sinencio, E. (2010). High PSR low drop-out regulator with feed-forward ripple cancellation technique. IEEE Journal of Solid-State Circuits, 45(3), 565–577.

A. Amer and E. Sánchez-Sinencio, “A 140 mA 90 nm CMOS low dropout regulator with −56 dB power supply rejection at 10 MHz,” Proceedings of the IEEE Custom Integrated Circuits Conference, Sep. 2010, pp. 1–4.

Yeung, S., Guo, J., & Leung, K. N. (2010). 25 mA LDO with -63 dB PSRR at 30 MHz for WiMAX. Electronics Letters, 46(15), 1080–1081.

Bangda Yang, B. Drost, S. Rao and P.K. Hanumolu, “A high-PSR LDO using a feedforward supply-noise cancellation technique,” in Proc. IEEE Custom Integr. Circuits Conf., Sep. 2011, pp. 1–4.

Ho, E. N. Y., & Mok, P. K. T. (2012). Wide-loading-range fully integrated LDR with a power-supply ripple injection filter. IEEE Transactions Circuits Systems II Express Briefs, 59(6), 356–360.

J. Teel, “Understanding power supply ripple rejection in linear regulators,” Texas Instruments Application Note, Aug. 2005.

V. Gupta and G. A. Rincón-Mora, “Analysis and design of monolithic, high PSR, linear regulators for SoC applications,” Proceedings of the. IEEE Society Conference, pp. 311–315, Sep. 2004.

S. Pithadia and S. Lester, “LDO PSRR Measurement Simplified,” Texas Instruments Application Note, Jul. 2009.

Acknowledgment

This work was supported in part by the Important National S&T Special Project of China under Grant 2009ZX01031-003-003.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Ming, X., Li, N., Lu, Y. et al. A wide-bandwidth PSR-enhanced low-dropout regulator using a bandpass feedforward supply ripple rejection circuit. Analog Integr Circ Sig Process 80, 221–232 (2014). https://doi.org/10.1007/s10470-014-0316-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-014-0316-y