Abstract

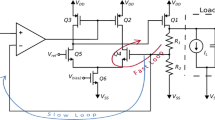

This paper presents an ultra-low-power and high-gain low-dropout (LDO) regulator. It is based on the flipped voltage follower cell with an adaptive biasing technique that is suitable for implantable biomedical applications. The error amplifier for the proposed regulator consists of two cross-coupled common-gate cells and a pseudo-folded-cascode structure to increase the regulator’s loop gain. In addition, three different compensation techniques including Miller, cascode, and Q-reduction are simultaneously utilized at the LDO regulator to achieve high stability despite having the minimum load current and ultra-low power consumption. The proposed LDO regulator has been simulated in TSMC 90-nm CMOS technology with minimum power consumption of 2.8 µW at no load. Post-layout simulation results show that the proposed LDO regulator is stable over load currents from 30 µA to 40 mA with a maximum on-chip CL of 100 pF. Moreover, the voltage regulator settles in less than 850 ns at 0.75 V output voltage that is achieved in response to a load transient step of 40 mA with a rise time of 200 ns. Besides, the obtained line and load regulations are significantly improved to 1 mV/V and 36 µV/mA, respectively.

Similar content being viewed by others

References

Y. Bastan, M. Janipoor-Deylamani, P. Amiri, Fast-transient capacitor-less low-dropout regulator with input current-differencing and dynamic current-boosting. Analog Integr. Circuit Signal Process. 99(5), 371–381 (2019)

S. Bu, K.-N. Leung, Y. Lu, J. Guo, Y. Zheng, A fully integrated low-dropout regulator with differentiator-based active zero compensation. IEEE Trans. Circuits Syst. I Regul. Pap. 65(10), 3578–3591 (2018)

S.S. Chong, P.K. Chan, A 0.9-μA quiescent current output-capacitorless LDO regulator with adaptive power transistors in 65-nm CMOS. IEEE Trans. Circuits Syst. Ι Reg. Pap. 60(4), 1072–1081 (2013)

R. Fathipour, A. Saberkari, H. Martinez, E. Alarcon, High slew rate current mode transconductance error amplifier for low quiescent current output-capacitorless CMOS LDO regulator. Integr. VLSI J. 47(2), 204–212 (2014)

S. Golabi, M. Yavari, A three-stage class AB operational amplifier with enhanced slew rate for switched-capacitor circuits. Analog Integr. Circuits Signal Process. 83(1), 111–118 (2015)

S. Golabi, M. Yavari, Design of CMOS three-stage amplifiers for fast-settling switched-capacitor circuits. Analog Integr. Circuits Signal Process. 80(2), 195–208 (2014)

J. Guo, K.N. Leung, A 6 µW chip-area-efficient output-capacitorless LDO in 90-nm CMOS technology. IEEE J. Solid State Circuits 45(9), 1896–1905 (2010)

X. Han, T. Burger, Q. Huang, An output-capacitor-free adaptively biased LDO regulator with robust frequency compensation in 0.13 µm CMOS for SoC application, In IEEE International Symposium on Circuits and Systems (ISCAS), pp. 2699–2702 (2016)

P. Hazucha et al., Area-efficient linear regulator with ultra-fast load regulation. IEEE J. Solid State Circuits 40(4), 933–940 (2005)

H. Ho, K.N. Leung, Dynamic bias-current boosting technique for ultralow power low-dropout regulator in biomedical applications. IEEE Trans. Circuits Syst. IΙ Exp. Briefs 58(3), 174–178 (2011)

S.R. Khan, I. Nadeem, Low quiescent current capacitorless small gain stages LDO with controlled pass transistors. Analog Integr. Circuits Signal Process. 94(2), 323–331 (2018)

S.K. Lau, P.K.T. Mok, K.N. Leung, A low dropout voltage regulator for SoC with Q-reduction. IEEE J. Solid State Circuits 42(3), 658–664 (2007)

C. Li, P.-K. Chan, FVF LDO regulator with dual dynamic-load composite gain stage. Analog Integr. Circuit. Signal Process 92(1), 131–140 (2017)

G. Li, H. Qian, J. Guo, B. Mo, Y. Lu, D. Chen, Dual active-feedback frequency compensation for output-capacitorless LDO with transient and stability enhancement in 65-nm CMOS. IEEE Trans. Power Electron. 35(1), 415–429 (2020)

K. Li, Y. Zheng, S. Liter, A transient-enhanced low dropout regulator with rail to rail dynamic impedance attenuation buffer suitable for commercial design. Microelectron. J. 63(5), 27–34 (2017)

Y. Lu, Y. Wang, Q. Pan, W.-H. Ki, C.-P. Yue, A fully-integrated low-dropout regulator with full-spectrum power supply rejection. IEEE Trans. Circuits Syst. Ι Reg. Pap. 62(3), 707–716 (2015)

A. Maity, A. Patra, A single-stage low-dropout regulator with a wide dynamic range for generic applications. IEEE Trans. Very Large Scale Integr. Syst. 24(6), 2117–2127 (2016)

A. Maity, A. Patra, Tradeoffs aware design procedure for an adaptively biased capacitorless low dropout regulator using nested Miller compensation. IEEE Trans. Power Electron. 31(1), 369–380 (2016)

V. Majidzadeh, A. Schmid, Y. Leblebici, A fully on-chip LDO voltage regulator for remotely powered cortical implants, in European Solid-State Circuits Conference (ESSCIRC), pp. 424–427 (2009)

T.Y. Man, P.K.T. Mok, M. Chan, A high slew-rate push-pull output amplifier for low-quiescent current low-dropout regulators with transient response improvement. IEEE Trans. Circuits Syst. II Exp. Briefs 54(9), 755–759 (2007)

M. Mojarad, M. Yavari, A low power four-stage amplifier for driving large capacitive loads. Int. J. Circuit Theory Appl. 42(9), 978–988 (2014)

O. Omeni, A.C.W. Wong, A.J. Burdett, C. Toumazou, Energy efficient medium access protocol for wireless medical body area sensor networks. IEEE Trans. Biomed. Circuits Syst. 2(4), 251–259 (2008)

B. Razavi, Design of Analog CMOS Integrated Circuits (McGraw-Hill, New York, 2001)

J.G.A. Rincon-Mora, Analog IC Design with Low-Dropout Regulators (LDOs) (McGraw-Hill, New York, 2009)

M.R. Salehi, R. Dastanian, E. Abiri, S. Nejadhasan, A 147 μW, 0.8 V and 7.5 (mV/V) LIR regulator for UHF RFID application. Int. J. Electron. Commun. 69(1), 133–140 (2015)

L.S.Y. Wong, S. Hossain, A. Ta, J. Edvinsson, D.H. Rivas, H. Nääs, A very low-power CMOS mixed-signal IC for implantable pacemaker applications. IEEE J. Solid State Circuits 39(12), 2446–2456 (2004)

W.-B. Yang, Y.-Y. Lin, Y.-L. Lo, Design of fast-locked digitally controlled low-dropout regulator for ultra-low voltage input. Circuits Syst. Signal Process. 36(12), 5041–5061 (2017)

M. Yavari, A design procedure for CMOS three-stage NMC amplifiers. IEICE Trans. Fundam. E94-A(2), 639–645 (2011)

M. Yavari, Active-feedback single miller capacitor frequency compensation techniques for three-stage amplifiers. J. Circuits Syst. Comput. 19(7), 1381–1398 (2010)

Y. Zeng, Y. Li, X. Zhang, H.-Z. Tan, A push-pulled FVF based output-capacitorless LDO with adaptive power transistors. Microelectron. J. 64(6), 69–77 (2017)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Moradian Boanloo, M., Yavari, M. A Low-Power High-Gain Low-Dropout Regulator for Implantable Biomedical Applications. Circuits Syst Signal Process 40, 1041–1060 (2021). https://doi.org/10.1007/s00034-020-01520-9

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-020-01520-9