Abstract

A new low voltage digital-to-analog conversion (DAC) architecture is proposed using weighted summation of voltages at the input terminals of a Floating Gate MOSFET (FGMOS). An 8-bit DAC has been designed based on this architecture and its simulation results are provided to verify its operation at ±1.0 V. The circuit possesses good accuracy, fast dynamic performance and low power consumption. The circuit operation was verified through SPICE simulations carried out using 0.13 μm CMOS technology.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The development of complex structures for Systems on Chip (SoC) architecture is increasingly becoming dependent on compact mixed-signal systems, embedding high performance analog blocks with complex digital circuitry on the same chip. This necessitates the design of small and simple DACs. Unfortunately, to achieve an acceptable resolution and good performance, a considerable amount of complexity and silicon area is required. Power consumption is also a dominant factor in IC design [1].

The design of DACs based on standard CMOS technologies has been pursued to overcome these constraints with some success [2–7]. Although each of the converters have some attractive features, in the form of either consuming low power [2–5], or possessing good dynamic performance [6], all of them consist of segmented or matrix architecture, rendering a complexity to the D/A converter circuit.

In this paper, a novel topology to design DACs by exploiting the ability of Floating Gate MOSFET (FGMOS) [8], a device introduced in the last decade and used frequently in digital designs, to achieve a weighted sum of input voltages is presented. Though D/A conversion through FGMOS can also be obtained using different approaches such as programming of floating gate charge [9, 10], etc., the resultant DAC is relatively complicated. The proposed circuit shows good accuracy and dynamic performance and its simple architecture and low power consumption make it quite promising for integration.

2 FGMOS transistor

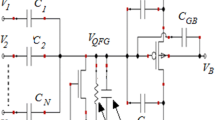

An n-input FGMOS transistor consists of a gate electrode which is left electrically floating. This floating gate is capacitively coupled to an array of n control gates through a second polysilicon layer. The terminal voltages and various capacitive coupling coefficients are defined in Fig. 1(b), where V FG is the floating gate potential, V 1, V 2...V n are the input signal voltages and C 1, C 2...C n are the capacitive coupling coefficients between the floating gate and each of the input gates.

Let Q FG denote the net charge on the floating gate, which is calculated as

where C S , C D and C B are the parasitic capacitances between gate and source, drain and body, respectively. V S , V D and V B are the potentials at the respective terminals.

Under normal circumstances, Q FG is equal to the initial charge on the floating gate, which is assumed to be zero in this case for simplicity. Then Eq. 1 reduces to

Since C S , C D and C B are quite small in comparison to the capacitive coefficients, C i , Eq. 2 can be safely approximated to

where k i = C i /C Total and

3 Principle of operation and design

The proposed approach for the design of the n-input DAC is explained through the circuit structure shown in Fig. 2. Transistors M1 and M2 are multiple input floating gate MOSFETs (MIFG) with n and two gate inputs, respectively.

Now V FG1, the floating gate potential of M1, can be written as

where k T1 = C T1/C Total1, C T1 and C Total1 being the capacitive coupling coefficient of the topmost control gate of M1 and total capacitance of M1, respectively, and V T is the threshold voltage of M1 and M2.

As M1 and M2 form a differential pair, V FG1 ≈ V FG2

where V FG2 is the floating gate potential of M2, k T2 = C T2/C Total2 and k o = C o /C Total2, C T2, C o and C Total2 being the capacitive coupling coefficients of the respective control gates of M2 and total capacitance of M2, respectively.

Equation 6 can be simplified as

Or,

If the die is designed to have

then Eq. 8 becomes

where C FG is the common factor with a suitable value.

4 Low voltage D/A converter

The structure of DAC shown in Fig. 2 has been modified by using a low voltage current mirror proposed in [11], and the resultant circuit for the low voltage D/A converter (LV DAC) is shown in Fig. 3. To drive M3 in saturation, M6 is biased in sub-threshold region by selecting I bias1 at sufficiently low level. M6 acts as a level shifter, reducing the minimum voltage drop across the current mirror. This arrangement reduces the power supply requirements of the D/A converter, thereby reducing the power consumption.

5 Simulation results

SPICE simulations using 0.13 μm CMOS technology were carried out to validate the operation of both the DAC circuits and evaluate their performance characteristics [12]. The simulations were run at 100 M samples/s.

It may be noted that application of inputs V T /k T1 and V T /k T2 at the gates M1 and M2, respectively, is optional. But it was found through simulation that application of these two inputs removes the transition glitches that were found to be present in the circuit’s response, thereby reducing the static non-linearities.

5.1 Proposed DAC

The circuit was operated at a power supply voltage of ±2.5 V, whereas digital LOW and HIGH voltage levels were 0 and 1.5 V and I bias was 100 μA. The output response for the 8-bit DAC is shown in Fig. 4. As seen in Fig. 5, a good accuracy is achieved, and the performance parameters INL and DNL were found to be around 0.43 LSB each. The circuit was found to possess an offset error of 25.22 mV and a full scale gain error of 0.071 V. Simulated values of other performance indices are presented in Table 1.

5.2 LV DAC

The DC output voltage and static linearities for an 8-bit LV DAC are shown in Figs. 6 and 7, respectively. The LV DAC can be operated at a power supply voltage of ±1 V, with the digital LOW and HIGH voltage levels being 0 and 0.5 V. The bias currents, I bias1, I bias2 and I bias3, were set at 10 nA, 20 μA and 100 μA, respectively. The INL and DNL for this circuit have been found to be 0.5 LSB. A comparison of its simulated performance with the proposed DAC is provided in Table 1.

6 Conclusion

A new D/A conversion circuit architecture using floating gate MOSFETs has been presented. The scheme exploits the property of weighted summation of gate-voltages, with capacitive coupling ratios as weighting coefficients. The proposed structure possesses good accuracy and low power consumption which have been verified using SPICE simulations of 8-bit version. The power consumption and supply requirements can be further compressed by employing a low voltage current mirror, without much effect on the performance. Due to their simple structures, the proposed DACs are suitable for complex on-chip mixed-signal circuit blocks.

References

Allen, P., & Holberg, D. (2002). CMOS analog circuit design. New York: Oxford University Press.

Wong, L., Kwok, C., & Rigby, G. (1999). A 1-V CMOS D/A converter with multi-input floating-gate MOSFET. IEEE Journal of Solid-State Circuits, 34(10), 1386–1390.

Greenley, B., Veith, R., Chang, D., & Moon, U. (2005). A low-voltage 10-bit CMOS DAC in 0.01 mm2 die area. IEEE Transactions on Circuits and Systems-II: Express Briefs, 52(5), 246–250.

Rantala, A., Kuivalainen, P., & Aberg, M. (1999). An 8-bit and a 10-bit low power high-speed neuron MOS digital-to-analog converter in 0.04 mm2. European Solid-State Circuits Conference/IEEE, pp. 310–313.

Wang, H., Kao, H., & Lee, T. (2004). An 8-bit 2-V 2-mW 0.25-mm2 CMOS DAC. Asia-Pacific Conference on Advanced System Integrated Circuits/IEEE, pp. 102–105.

Bugeja, A. R., Song, B., Rakers, P. L., & Gillig, S. F. (1999). A 14-b 100 M sample/s CMOS DAC designed for spectral performance. IEEE International Solid-State Circuits Conference, pp. 148–149.

Van De Plassche R. (1994). Integrated analog-to-digital and digital-to-analog converters. New York: Kluwer Academic Publishers.

Shibata, T., & Ohmi, T. (1992). A functional MOS transistor featuring gate-level weighted sum and threshold operation. IEEE Transactions on Electron Devices, 39(6), 1444–1455.

Serrano, G., & Hasler, P. (2004). A floating-gate DAC array. IEEE International Symposium on Circuits and Systems, pp. 357–360.

Lopez-Martin, A. J., Carlosena, A., & Ramirez-Angulo, J. (1999). D/A conversion based on multiple-input floating-gate MOST. Midwest Symposium on Circuits and Systems/IEEE, pp. 149–152.

Rajput, S. S., & Jamuar, S. S. (2003). A current mirror for low voltage, high performance analog circuits. Analog Integrated Circuits and Signal Processing, 36, 221–233.

Hendriks, P. (1997). Specifying communication DAC’s. IEEE Spectrum, pp. 58–69.

Open Access

This article is distributed under the terms of the Creative Commons Attribution Noncommercial License which permits any noncommercial use, distribution, and reproduction in any medium, provided the original author(s) and source are credited.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

Open Access This is an open access article distributed under the terms of the Creative Commons Attribution Noncommercial License (https://creativecommons.org/licenses/by-nc/2.0), which permits any noncommercial use, distribution, and reproduction in any medium, provided the original author(s) and source are credited.

About this article

Cite this article

Sehgal, R., Rajput, S.S. A low voltage 8-bit digital-to-analog converter using floating gate MOSFETs. Analog Integr Circ Sig Process 56, 199–204 (2008). https://doi.org/10.1007/s10470-008-9173-x

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-008-9173-x