Abstract

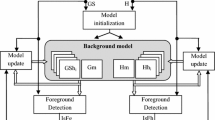

Hardware processing is more suitable for embedded image processing systems because of its higher performance and lower power consumption compared to software processing. In order to gain market share in the rapidly expanding market, early development of products and early introduction to the market are essential. A high-level synthesis tool exists to support this. This tool automatically converts high-level languages into hardware description languages. In a real embedded system, maximum system performance and power saving can be achieved by an optimal combination of carefully generated high-level synthesis hardware and peripheral devices such as cameras and displays. We have developed a program description method for high-level synthesis of the median-based dynamic background subtraction method. In this study, the developed high-level synthesis hardware is installed in the system to obtain the maximum performance. The maximum frame rate, ignoring the performance of the real camera, was 166 fps when the image size was QVGA and the number of past time series data was \(N=4\), which was very fast. Regardless of the image size, the hardware processing was more power efficient than the software processing.

Similar content being viewed by others

References

Applying deep learning vision technology to low-cost/power embedded systems, synopsys, 18 Jan. 2017. [Online]. https://www.slideshare.net/JennyMidwinter/applying-deep-learning-vision-technology-to-lowcostpower-embedded-systems. Accessed 1 Oct 2019

Stacking up software to drive FPGAs into the datacenter, next platform, 20 Nov. 2016. [Online]. https://www.nextplatform.com/2016/11/20/stacking-software-drive-fpgas-datacenter/. Accessed 1 Oct 2019

GPU vs FPGA performance comparison, Berten, 19 May. 2016. [Online]. https://www.bertendsp.com/gpu-vs-fpga-performance-comparison/. Accessed 1 Oct 2019

High-level synthesis with LegUp, [Online]. http://legup.eecg.utoronto.ca/. Accessed 10 Nov 2021

High-level synthesis—MATLAB and simulink, [Online]. https://jp.mathworks.com/discovery/high-level-synthesis.html. Accessed 10 Nov 2021

Ishikawa Y (2017) Hardware acceleration with multi-threading of java-based high level synthesis tool. In: HEART2017 proceedings of the 8th international symposium on highly efficient accelerators and reconfigurable technologies, vol 8, pp 1–6

Shinyamada K, Yamawaki A (2021) Development of high performance hardware by high-level synthesis of median-based dynamic background subtraction method with multiple line buffers, 6 Dec 2021. In: Technical meeting on systems, pp 23–28

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This work was presented in part at the joint symposium of the 27th International Symposium on Artificial Life and Robotics, the 7th International Symposium on BioComplexity, and the 5th International Symposium on Swarm Behavior and Bio-Inspired Robotics (Online, January 25-27, 2022).

About this article

Cite this article

Shinyamada, K., Yamawaki, A. Development of a real camera system with high-level synthesised hardware of median-based dynamic background subtraction. Artif Life Robotics 27, 541–546 (2022). https://doi.org/10.1007/s10015-022-00777-4

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10015-022-00777-4