Abstract

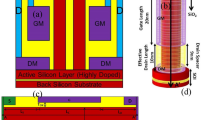

In this reported work, we have analyzed the different figure of merits for dopingless TFET. The charge-plasma based Planar-TFET does have a dual-gate with a half structure made from Silicon–Germanium (Si–Ge) compound. The Si–Ge is used with a composition factor of 0.45. The Si0.55Ge0.45 helped in the current enhancement of the Silicon-based TFET device. Several linearity parameters are calculated for low and high drain bias to acknowledge the device behavior at different biasing conditions. The heteromaterial planar-TFET is optimized according to the physical conditions where the source contact is considered as Schottky contact with barrier lowering. The work function of the source electrode is varied to check the effects of the Schottky barrier on the device characteristics. The optimized dopingless TFET is scaled down to lower dimensions for the possibility of nano-TFET devices without compromising the device performance. The nanoscaled dopingless nanowire TFET performs better as compared to dopingless planar TFET with similar dimensions. The obtained cutoff frequency is greater than 10 GHz and intermodulation distortion is less than − 650 dBm. The optimized structure showed low noise and harmonic distortions to be used for better sensing applications.

Similar content being viewed by others

References

Anand S, Sarin RK (2017) Gate misalignment effects on analog/RF performance of charge plasma-based doping-less tunnel FET. Appl Phys A 123(6):413. https://doi.org/10.1007/s00339-017-1029-8

Baccarani G, Wordeman MR, Dennard RH (1984) Generalized scaling theory and its application to a ¼ micrometer MOSFET design. IEEE Trans Electron Devices 31(4):452–462. https://doi.org/10.1109/T-ED.1984.21550

Barboni L, Siniscalchi M, Sensale-Rodriguez B (2015) TFET-based circuit design using the transconductance generation efficiency gm/Id method. IEEE J Electron Devices Society 3(3):208–216

Bati B, Nuholu Ç, Salam M, Ayyildiz E, Türüt A (2000) On the forward bias excess capacitance at intimate and MIS Schottky barrier diodes with perfect or imperfect ohmic back contact. Phys Scr 61(2):209

Boucart K, Ionescu AM (2007) Double-gate tunnel FET with high-κ gate dielectric. IEEE Trans Electron Devices 54(7):1725–1733. https://doi.org/10.1109/TED.2007.899389

Chen Q, Agrawal B, Meindl JD (2002) A comprehensive analytical subthreshold swing (S) model for double-gate MOSFETs. IEEE Trans Electron Devices 49(6):1086–1090. https://doi.org/10.1109/ted.2002.1003757

Chen ZX, Yu HY, Singh N, Shen NS, Sayanthan RD, Lo GQ, Kwong DL (2009) Demonstration of tunneling FETs based on highly scalable vertical silicon nanowires. IEEE Electron Device Lett 30(7):754–756

Dubey A, Narang R, Saxena M, Gupta M (2019) Investigation of total ionizing dose effect on SOI tunnel FET. Superlattices Microstruct 133:106186

Duvvury C (1986) A guide to short-channel effects in MOSFETs. IEEE Circuits Devices Mag 2(6):6–10. https://doi.org/10.1109/MCD.1986.6311897

Gao XP, Zheng G, Lieber CM (2009) Subthreshold regime has the optimal sensitivity for nanowire FET biosensors. Nano Lett 10(2):547–552

Gao A, Lu N, Wang Y, Li T (2016) Robust ultrasensitive tunneling-FET biosensor for point-of-care diagnostics. Sci Rep 6:22554

Gupta AK, Raman A, Kumar N (2019) Design and investigation of a novel charge plasma-based core-shell ring-TFET: analog and linearity analysis. IEEE Trans Electron Devices 66(8):3506–3512

Hueting RJE, Rajasekharan B, Salm C, Schmitz J (2008) The charge plasma P–N diode. IEEE Electron Device Lett 29(12):1367–1369. https://doi.org/10.1109/LED.2008.2006864

Hur J, Moon DI, Han JW, Kim GH, Jeon CH, Choi YK (2017) Tunneling effects in a charge-plasma dopingless transistor. IEEE Trans Nanotechnol 16(2):315–320

Iida R, Kim SH, Yokoyama M, Taoka N, Lee SH, Takenaka M, Takagi S (2011) Planar-type In0. 53Ga0. 47As channel band-to-band tunneling metal-oxide-semiconductor field-effect transistors. J Appl Phys 110(12):124505

Jayaswal N, Raman A, Kumar N, Singh S (2019) Design and analysis of electrostatic-charge plasma based dopingless IGZO vertical nanowire FET for ammonia gas sensing. Superlattices Microstruct 125:256–270

Kim S, Kwon DW, Lee R, Kim DH, Park BG (2017) Simulation study on temperature dependence of MOSFET and TFET-based pH-sensitive ISFET. In: 2017 Silicon Nanoelectronics Workshop (SNW), IEEE, pp 93–94

Kumar MJ, Nadda K (2012) Bipolar charge-plasma transistor: a novel three terminal device. IEEE Trans Electron Devices 59(4):962–967. https://doi.org/10.1109/TED.2012.2184763

Kumar G, Raman A (2016) Pressure sensor based on MEMS nano-cantilever beam structure as a heterodielectric gate electrode of dopinglessá TFET. Superlattices Microstruct 100:535–547

Kumar N, Raman A (2019a) Design and investigation of charge-plasma-based work function engineered dual-metal-heterogeneous gate Si–Si 0.55 Ge 0.45 GAA-cylindrical NWTFET for ambipolar analysis. IEEE Trans Electron Devices 66(3):1468–1474

Kumar N, Raman A (2019b) Performance assessment of the charge-plasma-based cylindrical GAA vertical nanowire TFET with impact of interface trap charges. IEEE Trans Electron Devices (in press)

Kumar N, Mushtaq U, Amin SI, Anand S (2019) Design and performance analysis of dual-gate all around core-shell nanotube TFET. Superlattices Microstruct 125:356–364

Lee R, Kwon DW, Kim S, Kim DH, Park BG (2017) Investigation of feasibility of tunneling field effect transistor (TFET) as highly sensitive and multi-sensing biosensors. J Semicond Technol Sci 17(1):141–146

Liu H, Vaddi R, Datta S, Narayanan V (2013) Tunnel FET-based ultra-low power, high-sensitivity UHF RFID rectifier. In: International Symposium on Low Power Electronics and Design (ISLPED), IEEE, pp 157–162

Lu H, Li W, Lu Y, Fay P, Ytterdal T, Seabaugh A (2016) Universal charge-conserving TFET SPICE model incorporating gate current and noise. IEEE J Explor Solid-State Comput Devices Circuits 2:20–27

Luisier M, Klimeck G (2010) Simulation of nanowire tunneling transistors: from the Wentzel–Kramers–Brillouin approximation to full-band phonon-assisted tunneling. J Appl Phys 107(8):084507

Luong GV, Narimani K, Tiedemann AT, Bernardy P, Trellenkamp S, Zhao QT, Mantl S (2016) Complementary strained Si GAA nanowire TFET inverter with suppressed ambipolarity. IEEE Electron Device Lett 37(8):950–953

Matheu P, Ho B, Jacobson ZA, Liu TJK (2012) Planar GeOI TFET performance improvement with back biasing. IEEE Trans Electron Devices 59(6):1629–1635

Mokkapati S, Jaiswal N, Gupta M, Kranti A (2019) Gate-all-around nanowire junctionless transistor-based hydrogen gas sensor. IEEE Sens J 19(13):4758–4764

Rajasekhar K, Raman A, Kumar N, Singh S, Kakkar D (2018) Design and analysis of pressure sensor based on MEMS cantilever structure and pocket doped DG-TFET. J Nanoelectron Optoelectron 13(9):1295–1304

Shalaev VM, Douketis C, Haslett T, Stuckless T, Moskovits M (1996) Two-photon electron emission from smooth and rough metal films in the threshold region. Phys Rev B 53(16):11193

Silvaco International (2010) ATLAS user manual 2010. Silvaco International, Santa Clara

Sterkel M, Wang PF, Nirschl T, Fabel B, Bhuwalka KK, Schulze J, Eisele I, Schmitt-Landsiedel D, Hansch W (2005) Characteristics and optimisation of vertical and planar tunnelling-FETs. J Phys 10(1):15 (IOP Publishing)

Wang W, Wang PF, Zhang CM, Lin X, Liu XY, Sun QQ, Zhou P, Zhang DW (2013) Design of U-shape channel tunnel FETs with SiGe source regions. IEEE Trans Electron Devices 61(1):193–197

Zhang Z, Pagette F, D’emic C, Yang B, Lavoie C, Zhu Y, Hopstaken M, Maurer S, Murray C, Guillorn M, Klaus D (2010) Sharp reduction of contact resistivities by effective Schottky barrier lowering with silicides as diffusion sources. IEEE Electron Device Lett 31(7):731–733

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Kumar, N., Raman, A. Low voltage charge-plasma based dopingless Tunnel Field Effect Transistor: analysis and optimization. Microsyst Technol 26, 1343–1350 (2020). https://doi.org/10.1007/s00542-019-04666-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00542-019-04666-y