Abstract

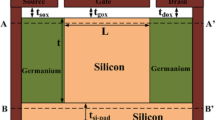

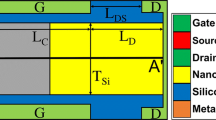

Tunnel FET (TFET) based upon charged-plasma (CP) concept have came out as a potential Metal-Oxide-Semiconductor-Field-Effect-Transistor (MOSFET) replacement as it provides immunization towards short channel effects (SCEs) and random dopant fluctuations (RDFs), along with providing inherent benefits of conventional TFETs such as low off-state current (IOFF) and sub-60 mV/dec subthreshold swing. So, in this manuscript, we investigate a CP-based dopingless TFET (DLTFET) with source and channel made up of Germanium, Si0.6Ge0.4 drain and TiO2 as gate-dielectric using simulations for low power analog/RF and linear applications and abbreviated as HJ HD DLTFET where HJ stands for heterojunction, HD represents high-κ dielectric. In CP-concept, source and drain regions are generated by applying work function for respective electrodes without performing chemical doping. This manuscript investigates, for the first time, a DLTFET which employs a heterojunction of low bandgap material .i.e. Ge as channel and source material and Si0.6Ge0.4 for drain as it is a high bandgap material relative to Ge, along with TiO2 as a high-κ gate dielectric and drain voltage of 0.3 V. The numerical simulations illustrates higher ION, ION/IOFF ratio and improved average sub-threshold swing (SSavg) for HJ HD DLTFET in comparison to conventional DLTFET. Furthermore, we also investigate the analog/RF and linearity parameters of the HJ HD DLTFET to demonstrate its competence in low-power analog, radio frequency (RF), sensors, and linear applications.

Similar content being viewed by others

References

Seabaugh AC, Zhang Q (2010) Low-voltage tunnel transistors for beyond CMOS logic. Proc IEEE 98:2095–110

Ionescu AM, Riel H (2011) Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479:329–37

Damrongplasit N, Kim SH, Liu TJK (2013) Study of random dopant fluctuation induced variability in the raised-ge-source TFET. IEEE Electron Device Lett 34:184–6

Kumar N, Raman A (2019) Design and investigation of charge plasma based WF engineered dual-metal-heterogeneous gate Si − Si0.55Ge0.45 GAA- cylindrical NWTFET for ambipolar analysis. IEEE Trans Electron Devices 66:1468–1474

Sahoo S, Dash S, Mishra GP (2019) Work-function modulated hetero gate charge plasma TFET to enhance the device performance. In: Proceedings of 3rd IEEE international conference on devices for integrated circuit, DevIC, pp 461–4

Raad B, Nigam K, Sharma D, Kondekar P (2016) Dielectric and work function engineered TFET for ambipolar suppression and RF performance enhancement. IET Electron Lett 52:770–2

Das GD, Dash S, Mishra GP (2018) Impact of hetero-dielectric engineering on the performance of single gate tunnel FET. In: 2018 IEEE international conference on control, power, communication and computing technologies, ICCPCCT. IEEE, pp 114–7

Chattopadhyay A, Mallik A (2011) Impact of a spacer dielectric and a gate Overlap/Underlap on the device performance of a tunnel field-effect transistor. IEEE Trans Electron Devices 58:677–83

Zhao Y, Wu C, Huang Q, Chen C, Zhu J, Guo L, Jia R, Lv Z, Yang Y, Li M, Huang R (2017) A novel tunnel FET design through adaptive bandgap engineering with constant sub-threshold slope over 5 decades of current and high ION/IOFF ratio. IEEE Electron Device Lett 38:540–3

Chandan BV, Dasari S, Nigam K, Yadav S, Pandey S, Sharma D (2018) Impact of gate material engineering on ED-TFET for improving DC/analogue-RF/linearity performances. Micro Nano Lett 13:1653–6

Ram MS, Abdi DB (2014) Dopingless tunnel FET with a hetero-material gate: Design and analysis. In: IEEE 2nd Int Conf Emerg Electron Mater to Devices (ICEE 2014), pp 2–5

Saurabh S, Kumar MJ (2011) Novel attributes of a dual material gate nanoscale tunnel field-effect transistor. IEEE Trans Electron Devices 58:404–10

Nagavarapu V, Jhaveri R, Woo JCS (2008) The tunnel source (PNPN) n-MOSFET: A novel high performance transistor. IEEE Trans Electron Devices 55:1013–9

Kumar MJ, Janardhanan S (2013) Doping-less tunnel field effect transistor: design and investigation. IEEE Trans Electron Devices 60:3285–90

Hueting RJE, Rajasekharan B, Salm C, Schmitz J (2008) The charge plasma PN diode. IEEE Electron Device Lett 29(12):1367–1369

Kim SH, Agarwal S, Jacobson ZA, Matheu P, Hu C, Liu TJK (2010) Tunnel field effect transistor with raised germanium source. IEEE Electron Device Lett 31:1107–9

Gupta A, Chiang CK, Yang WY, Hsieh ER, Chung SS (2020) Design of low voltage vertical channel face-tunneling TFET using Ge/SiGe materials and its SRAM circuit performance. In: International symposium on VLSI technology, system and applications, pp 132–133

Han T, Liu H, Chen S, Wang S, Li W (2019) A dopingless, TFET with Si0.6Ge0.4 heterojunction for improvement of on-off current ratio and analog/RF performance. MDPI Electron 8(5):574

Sharma S, Kaur B (2020) Performance investigation of asymmetric double-gate doping less tunnel FET with Si/Ge heterojunction. IET Circ Devices Syst 14(5):695–701

Han T, Lu H, Chen S, Wang S, Li W (2019) Design and investigation of the high-performance doping-less TFET with Ge/Si0.6Ge0.4/Si heterojunction. Micromachines 10:6

Nayfeh OM, Chléirigh CN, Hoyt JL, Antoniadis DA (2008) Measurement of enhanced gate-controlled band-to-band tunneling in highly strained silicon-germanium diodes. IEEE Electron Device Lett 29 (5):468–470

Mech BC, Kumar J (2017) Effect of high-k dielectric on the performance of Si, InAs and CNT. IET Micro Nano Lett 12:624–9

Ghosh B, Akram MW (2013) Junctionless tunnel field effect transistor. IEEE Electron Device Lett 34:584–6

Rawat A, Surana VK, Meer M, Bhardwaj N, Ganguly S, Saha D (2019) Gate Current reduction and improved DC/RF characteristics in GaN-based MOS-HEMTs using thermally grow TiO2, as a dielectric. IEEE Trans Electron Devices 66(6):2557–2562

Kumar A, Mondal S, Rao KSRK (2016) Critical investigation of high performance spin coated high-κ titania thin films based MOS capacitor. J Mater Sci Mater Electron 27(6):5264–5270

Gyanan S, Mondal A, Kumar A (2016) Tunable dielectric properties of TiO2 thin film based MOS system for application in microelectronic. Superlattice Microstruct 100:876–885

Lee WG, Woo SI, Kim JC, Choi SH, Oh KH (1994) Preparation and properties of amorphous TiO2 thin film by plasma enhanced chemical vapor deposition. Thin Solid Films 237(1-2):105–111

ATLAS User’s Manual, Silvaco, (Santa Clara, CA, USA)

Shockley W, Read WT (1952) Statistics of the recombination of holes and electrons. Phys Rev 87:835–42

Rajasekharan B, Hueting RJE, Salm C, Hemert TV, Wolters RAM, Schmitz J (2010) Fabrication and characterization of the charge-plasma diode. IEEE Electron Device Lett 31(6):528– 530

Kumar MJ, Nadda K (2012) Bipolar charge-plasma transistor: A novel three terminal device. IEEE Trans Electron Devices 59(4):962–967

Lim CM, Zhao Z, Sumita K, Toprasertpong K, Takenaka M, Takagi S (2020) Operation of (111) ge-on-insulator n-Channel MOSFET fabricated by smart-cut technology. IEEE Electron Device Lett 41(7):985–988

Ye H, Yu J (2014) Germanium epitaxy on silicon. Sci Technol Adv Mater 15(2):024601

Wang PY, Tsui BY (2015) Experimental demonstration of p-Channel germanium epitaxial tunnel layer (ETL) tunnel FET with high tunneling current and high ON/OFF Ratio. IEEE Electron Device Lett 36(12):1264–1266

Xie Q, Deng S, Schaekers M, Lin D, Caymax M, Delabie A, Qu XP, Jiang YL, Deduytsche D, Detavernier C (2012) Germanium surface passivation and atomic layer deposition of high-k dielectrics—a tutorial review on Ge-based MOS capacitors. Semicond Sci Technol 27(7):074012

Ardalan P, Pickett ER, Harris JS, Marshall AF, Bent SF (2008) Formation of an oxide-free Ge/TiO2 interface by atomic layer deposition on brominated Ge. Appl Phys Lett 92(25):2–5

Simionescu OG, Romanięan C, Tutunaru O, Ion V, Buiu O, Avram A (2019) RF Magnetron sputtering deposition of TiO2 thin films in a small continuous oxygen flow rate. Coatings 9(7):442

Campbell SA, et al. (1997) MOSFET transistors fabricated with high permittivity TiO2 dielectrics. IEEE Trans Electron Devices 44(1):104–109

Dalapati GK, Chatterjee S, Samanta SK, Maiti CK (2003) Electrical characterization of low temperature deposited TiO2 films on strained-SiGe layers. Appl Surf Sci 210(3-4):249–254

Sahay S, Kumar MJ (2017) Spacer design guidelines for nanowire FETs from gate-induced drain leakage perspective. IEEE Trans Electron Devices 64(7):3007–3015

Malik A, Chattopadhyay A, Guin S, Karmakar A (2013) Impact of a spacer-drain overlap on the characteristics of a Silicon tunnel field-effect transistor based on vertical tunneling. IEEE Trans Electron Devices 60(3):935–943

Wadhwa G, Raj B (2019) Design, Simulation and performance analysis of JLTFET biosensor for high sensitivity. IEEE Trans Nanotechnol 18:567–574

Lin R, Lu Q, Ranade P, King TJ, Hu C (2002) An adjustable work function technology using Mo gate for CMOS devices. IEEE Electron Device Lett 23:49–51

Mallik A, Chattopadhyay A (2012) Tunnel field-effect transistors for analog/mixed-signal system-on-chip applications. IEEE Trans Electron Devices 59:888–894

Nigam K, Kondekar P, Sharma D (2016) DC characteristics and analog/RF performance of novel polarity control GaAs-Ge based tunnel field effect transistor. Superlattice Microstruct 92:224– 231

Mookerjea S, Krishnan R, Datta S, Narayanan V (2009) On enhanced miller capacitance effect in interband tunnel transistors. IEEE Electron Device Lett 30:1102–1104

Yang Y, Tong X, Yang LT, Guo PF, Fan L, Yeo YC (2010) Tunneling field-effect transistor: capacitance components and modeling. IEEE Electron Device Lett 31:752–754

Cho S, Lee JS, Kim KR, Park BG, Harris JS, Kang IM (2011) Analyses on small-signal parameters and radio-frequency modeling of gate-all-around tunneling field-effect transistors. IEEE Trans Electron Devices 58:4164–4171

Kumar S, Singh KS, Nigam K, Tikkiwal VA, Chandan BV (2019) Dual-Material dual-oxide double gate TFET for improvement in DC Characteristics, analog/RF and linearity performance. Springer Appl Phys A 125

Gupta AK, Raman A, Kumar N (2019) Design and investigation of a novel charge-plasma-based core-shell Ring TFET: Analog and linearity analysis. IEEE Trans Electron Devices 66:3506–3512

Acknowledgements

This work was supported by the SMDP-C2SD under the reference letter no. 9(1)2014-MDD (NIT Delhi, Delhi, India).

Funding

The authors did not receive any financial support from any agency/organization for the submitted work.

Author information

Authors and Affiliations

Contributions

In this work, Suruchi Sharma, Rikmantra Basu and Baljit Kaur contributed equally to the design, implementation and analysis of the research, and manuscript write-up.

Corresponding author

Ethics declarations

Conflicts of interest/Competing interests

No conflicts of interest/competing interests regarding this manuscript.

Additional information

Availability of data and material (data transparency)

All the data taken from another resource has been given the corresponding reference. The data, for which reference is not provided, is the original data.

Code availability (software application or custom code)

The code has been implemented on 2-D silvaco ATLAS device simulator.

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Sharma, S., Basu, R. & Kaur, B. Investigation of Charge-plasma Based Dopingless Tunnel FET for Analog/RF and Linear Applications. Silicon 14, 7701–7710 (2022). https://doi.org/10.1007/s12633-021-01514-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-01514-5