Abstract

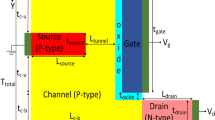

The generation and accumulation of trap charges at oxide-semiconductor contact is a crucial point to consider since it affects device performance and reliability. This paper aimed to provide a comprehensive assessment of interface trap charges on the characteristics of a ultra-thin source region-based F-shaped Tunnel FET (UTS-F-TFET) with theoretical and numerical calculation of important frequency and linearity parameters. Comparative research is carried out to opt for the best lower bandgap material for source region to optimize the analog functionality of UTS-F-TFET. With a steeper subthreshold slope, the UTS-F-TFET has increased current carrying capabilities and reduced ambipolar behavior. This research aims to investigate the impact of ITCs on DC characteristics (Thermal equilibrium state, ON and OFF state) and analog/RF performance of the simulated device. Moreover, the consequence of ITCs on linearity figure of merits with reliability consideration is also investigated. As per this investigation, the proposed TFET structure exhibited minimal distortion in linearity metrics with negligible influence of ITCs. As a result, the proposed UTS-F-TFET is compatible with ultra-low power high-frequency operations with minimum distortion.

Similar content being viewed by others

Availability of data and material

All relevant data has been included in manuscript.

References

S.-W. Sun, P.G. Tsui, Limitation of cmos supply-voltage scaling by mosfet threshold-voltage variation. IEEE J. Solid-State Circuits 30(8), 947–949 (1995)

M.-H. Tsai, T.-P. Ma, The impact of device scaling on the current fluctuations in mosfet’s. IEEE Trans. Electron Dev. 41(11), 2061–2068 (1994)

S.O. Koswatta, M.S. Lundstrom, D.E. Nikonov, Performance comparison between pin tunneling transistors and conventional mosfets. IEEE Trans. Electron Dev. 56(3), 456–465 (2009)

U. E. Avci, R. Rios, K. J. Kuhn, I. A. Young, Comparison of power and performance for the tfet and mosfet and considerations for p-tfet. In: 2011 11th IEEE International Conference on Nanotechnology. IEEE, (2011), pp. 869–872

U.E. Avci, D.H. Morris, I.A. Young, Tunnel field-effect transistors: prospects and challenges. IEEE J. Electron Dev. Soc. 3(3), 88–95 (2015)

J. Bizindavyi, A.S. Verhulst, Q. Smets, D. Verreck, B. Sorée, G. Groeseneken, Band-tails tunneling resolving the theory-experiment discrepancy in esaki diodes. IEEE J. Electron Dev. Soc. 6, 633–641 (2018)

W.Y. Choi, B.-G. Park, J.D. Lee, T.-J.K. Liu, Tunneling field-effect transistors (tfets) with subthreshold swing (ss) less than 60 mv/dec. IEEE Electron Dev. Lett. 28(8), 743–745 (2007)

K. Nigam, D. Sharma et al., Approach for ambipolar behaviour suppression in tunnel fet by workfunction engineering. Micro Nano Lett. 11(8), 460–464 (2016)

Prabhat, D.S. Yadav, Design and investigation of f-shaped tunnel fet with enhanced analog/rf parameters. Silicon, pp. 1–16 (2021)

P. Singh, D.S. Yadav, Impactful study of f-shaped tunnel fet. Silicon, pp. 1–7 (2021)

S. Yun, J. Oh, S. Kang, Y. Kim, J.H. Kim, G. Kim, S. Kim, F-shaped tunnel field-effect transistor (tfet) for the low-power application. Micromachines 10(11), 760 (2019)

S. Kumar, D.S. Yadav, Assessment of interface trap charges on proposed tfet for low power high-frequency application (2021)

C.K. Pandey, A. Singh, S. Chaudhury, Analysis of interface trap charges on dielectric pocket soi-tfet. In: Devices for Integrated Circuit (DevIC). IEEE 2019, pp. 337–340 (2019)

Z. Jiang, Y. Zhuang, C. Li, P. Wang, Y. Liu, Impact of interface traps on direct and alternating current in tunneling field-effect transistors. J. Electr. Comput. Eng. 2015 (2015)

S.W. Kim, J.H. Kim, T.-J.K. Liu, W.Y. Choi, B.-G. Park, Demonstration of l-shaped tunnel field-effect transistors. IEEE Trans. Electron Dev. 63(4), 1774–1778 (2015)

T. Silvaco, Manuals. atlas (Silvaco Intematiailal. Co, USA, 2021)

P. Venkatesh, K. Nigam, S. Pandey, D. Sharma, P.N. Kondekar, Impact of interface trap charges on performance of electrically doped tunnel fet with heterogeneous gate dielectric. IEEE Trans. Dev. Mater. Reliab. 17(1), 245–252 (2017)

S. Chander, S.K. Sinha, S. Kumar, P.K. Singh, K. Baral, K. Singh, S. Jit, Temperature analysis of ge/si heterojunction soi-tunnel fet. Superlatt. Microstruct. 110, 162–170 (2017)

N. Parmar, P. Singh, D.P. Samajdar, D.S. Yadav, Temperature impact on linearity and analog/rf performance metrics of a novel charge plasma tunnel fet. Appl. Phys. A 127(4), 1–9 (2021)

D.S. Yadav, D. Sharma, R. Agrawal, G. Prajapati, S. Tirkey, B.R. Raad, V. Bajaj, Temperature based performance analysis of doping-less tunnel field effect transistor. In: 2017 International Conference on Information, Communication, Instrumentation and Control (ICICIC). IEEE, pp. 1–6 (2017)

S. Kumar, D.S. Yadav, Temperature analysis on electrostatics performance parameters of dual metal gate step channel tfet. Appl. Phys. A 127(5), 1–11 (2021)

A. Dixit, D.P. Samajdar, N. Bagga, D.S. Yadav, Performance investigation of a novel gaas1-xsbx-on-insulator (gasoi) finfet: role of interface trap charges and hetero dielectric. Mater. Today Commun. 26, 101964 (2021)

S. Sharma, R. Basu, B. Kaur, Interface trap charges associated reliability analysis of si/ge heterojunction dopingless tfet. Dev. Syst. IET Circuits (2021)

P.G. Der Agopian, M.D.V. Martino, S.G. dos Santos Filho, J.A. Martino, R. Rooyackers, D. Leonelli, C. Claeys, Temperature impact on the tunnel fet off-state current components. Solid-State Electron. 78, 141–146 (2012)

K. Nigam, S. V. Singh, P. Kwatra, Investigation and design of stacked oxide polarity gate jltfet in the presence of interface trap charges for analog/rf applications. Silicon, pp. 1–18 (2021)

N. Parmar, D. S. Yadav, S. Kumar, R. Sharma, S. Saraswat, A. Kumar, Performance analysis of a novel dual metal strip charge plasma tunnel fet. In: 2020 IEEE International Students’ Conference on Electrical, Electronics and Computer Science (SCEECS). IEEE, pp. 1–5 (2020)

N. Kumar, A. Raman, Design and analog performance analysis of charge-plasma based cylindrical gaa silicon nanowire tunnel field effect transistor. Silicon, pp. 1–8 (2019)

B.V. Chandan, K. Nigam, D. Sharma, S. Pandey, Impact of interface trap charges on dopingless tunnel fet for enhancement of linearity characteristics. Appl. Phys. A 124(7), 1–6 (2018)

P. Singh, D.P. Samajdar, D.S. Yadav, A low power single gate l-shaped tfet for high frequency application. In: 6th International Conference for Convergence in Technology (I2CT). IEEE 2021, pp. 1–6 (2021)

B.R. Raad, D. Sharma, P. Kondekar, K. Nigam, D.S. Yadav, Drain work function engineered doping-less charge plasma tfet for ambipolar suppression and rf performance improvement: a proposal, design, and investigation. IEEE Trans. Electron Dev. 63(10), 3950–3957 (2016)

D.S. Yadav, D. Sharma, S. Tirkey, D.G. Sharma, S. Bajpai, D. Soni, S. Yadav, M. Aslam, N. Sharma, Hetero-material cptfet with high-frequency and linearity analysis for ultra-low power applications. Micro Nano Lett. 13(11), 1609–1614 (2018)

D.S. Yadav, D. Sharma, B.R. Raad, V. Bajaj, Impactful study of dual work function, underlap and hetero gate dielectric on tfet with different drain doping profile for high frequency performance estimation and optimization. Superlatt. Microstruct. 96, 36–46 (2016)

S. Tirkey, D.S. Yadav, D. Sharma, Controlling ambipolar current of dopingless tunnel field-effect transistor. Appl. Phys. A Mater. Sci. Process. 124(12), 809 (2018)

D.S. Yadav, A. Verma, D. Sharma, S. Tirkey, B.R. Raad, Comparative investigation of novel hetero gate dielectric and drain engineered charge plasma tfet for improved dc and rf performance. Superlatt. Microstruct. 111, 123–133 (2017)

N. Kumar, A. Raman, Performance assessment of the charge-plasma-based cylindrical gaa vertical nanowire tfet with impact of interface trap charges. IEEE Trans. Electron Dev. 66(10), 4453–4460 (2019)

J. Madan, R. Chaujar, Interfacial charge analysis of heterogeneous gate dielectric-gate all around-tunnel fet for improved device reliability. IEEE Trans. Dev. Mater. Reliab. 16(2), 227–234 (2016)

D.A. Buchanan, Scaling the gate dielectric: materials, integration, and reliability. IBM J. Res. Dev. 43(3), 245–264 (1999)

Acknowledgements

The authors would like to thank Dr. Dip Prakash Samajdar from Department of Electronics and Communication Engineering, PDPM Indian Institute of Information Technology, Design & Manufacturing, Jabalpur, Madhya Pradesh, India for providing valuable suggestions and support to carry out this research work.

Funding

Not applicable.

Author information

Authors and Affiliations

Contributions

PS: Conceptualization, data curation, formal analysis, methodology, investigation, writing-original draft. DSY: Supervision, validation, visualization, writing-review and editing.

Corresponding author

Ethics declarations

Conflict of interest

No conflicts of interest.

Consent for publication

We are giving consent to publish.

Consent to participate

We are giving consent to participate.

Research involving human participants and/or animals

No.

Informed consent

Not applicable.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Singh, P., Yadav, D.S. Performance analysis of ITCs on analog/RF, linearity and reliability performance metrics of tunnel FET with ultra-thin source region. Appl. Phys. A 128, 612 (2022). https://doi.org/10.1007/s00339-022-05741-4

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00339-022-05741-4