Abstract

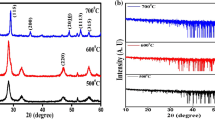

For this proposed work, the electrical and ferroelectric properties of metal–ferroelectric–insulator–silicon (MFeIS) and metal–ferroelectric–insulator–metal (MFeIM) capacitors with Bi4Ti3O12 (BIT) ferroelectric film deposited on HfO2/Si substrate were investigated. Physical vapor deposition technique (RF sputtering) was carried out for the deposition of 100 nm ferroelectric and high-k dielectric film of 5, 10 and 15 nm thickness. The structural properties such as crystallographic phase, grain size with composition and refractive index of the deposited films were measured by X-ray diffraction, field emission scanning electron microscopy with energy dispersive spectroscopy (FESEM-EDS) and multiple angle ellipsometry. Metal/ferroelectric/silicon (MFeS), metal/ferroelectric/metal (MFeM), metal/insulator/silicon (MIS), MFeIS and MFeIM structures were fabricated to obtain the electrical and ferroelectric properties. Investigation shows that the MFeIS structure with 10 nm buffer layer demonstrates improved memory window of 8.81 V as compared to the 3.3 V in the MFeS structure. MFeIM with 10 nm HfO2 buffer layer shows maximum remnant polarization of 4.05 μC/cm2. MFeI (10 nm) S structure even shows endurance higher than 1013 read/write cycles and data retention for more than 10 years. The reliability of the ferroelectric and ferroelectric/dielectric stack was obtained by measuring the breakdown voltage characteristics.

Similar content being viewed by others

References

S. M. Said, M. F. M. Sabri, and F. Salleh, in Ref. Modul. Mater. Sci. Mater. Eng. (Elsevier, 2016).

H. Ishiwara, J. Nanosci. Nanotechnol. 12, 7619 (2012)

T. Mikolajick, Encycl. Mater. Sci. Technol. 2, 1 (2004)

E.C. Ahn, H.-S.P. Wong, E. Pop, Nat. Rev. Mater. 3, 1 (2018)

J.S. Meena, S.M. Sze, U. Chand, T.Y. Tseng, Nanoscale Res. Lett. 9, 1 (2014)

H. Pirovano, in Search Next Mem. Insid. Circuitry from Oldest to Emerg. Non-Volatile Memories (Springer International Publishing, Cham, 2017), pp. 27–46.

C.S. Hwang, Adv. Electron. Mater. 1, 1 (2015)

X. Pan, Designing Future Low-Power and Secure Processors with Non-Volatile Memory, The Ohio State University, 2017.

J. Zhao, C. Xu, P. Chi, Y. Xie, I.P.S.J. Trans, Syst. LSI Des. Methodol. 8, 2 (2015)

H. A. Demkov and A.-B. Posadas, in Thin Film. Silicon (World Scientific Publishing Co Pte Ltd, Austin, 2016), pp. 403–454.

S. Sakai, R. Ilangovan, IEEE Electron Device Lett. 25, 369 (2004)

G.H. Haertling, J. Am. Ceram. Soc. 82, 797 (1999)

O. Auciello, J.F. Scott, R. Amesh, Phys. Today 51, 22 (1998)

N.M. Sbrockey, G.S. Tompa, R. Lavelle, K.A. Trumbull, M.A. Fanton, D.W. Snyder, R.G. Polcawich, D.M. Potrepka, J. Vac. Sci. Technol. A Vacuum, Surfaces, Film. 36, 031509 (2018)

X.K. Wei, T. Sluka, B. Fraygola, L. Feigl, H. Du, L. Jin, C.L. Jia, N. Setter, A.C.S. Appl, Mater. Interfaces 9, 6539 (2017)

P. Kour, S.K. Pradhan, P. Kumar, S.K. Sinha, M. Kar, Mater. Today Proc. 4, 5727 (2017)

H. H. Huang, Q. Zhang, E. Huang, R. Maran, O. Sakata, Y. Ehara, T. Shiraishi, H. Funakubo, P. Munroe, and N. Valanoor, Adv. Mater. Interfaces 2, (2015).

C. A. P. De Araujo, J. D. Cuchiaro, D. L. Mc Millan, M. C. Scott, and J. F. Scott, Nature 374, 627 (1995).

D.V. Averyanov, C.G. Karateeva, I.A. Karateev, A.M. Tokmachev, M.V. Kuzmin, P. Laukkanen, A.L. Vasiliev, V.G. Storchak, Mater. Des. 116, 616 (2017)

S. R. Singamaneni, J. T. Prater, and J. Narayan, Appl. Phys. Rev. 3, (2016).

Z. Fan, J. Chen, J. Wang, J. Adv. Dielectr. 06, 1630003 (2016)

F.T.L. Muniz, M.A.R. Miranda, C. dos Santos, J.M. Sasaki, Acta Crystallogr. Sect. A Found. Adv. 72, 385 (2016)

J. Geissbühler, S. De Wolf, B. Demaurex, J. P. Seif, D. T. L. Alexander, L. Barraud, and C. Ballif, Appl. Phys. Lett. 102, (2013).

J.T. Dawley, R. Radspinner, B.J.J. Zelinski, D.R. Uhlmann, J. Sol-Gel Sci. Technol. 20, 85 (2001)

M. Vehkanaki, T. Hatanpaa, M. Kemell, M. Ritala, M. Leskela, Chem. Matter. 18, 3883 (2006)

C. Long, W. Ren, L. Liu, Y. Xia, and H. Fan, (n.d.).

M.M. Hasan, A.S.M.A. Haseeb, R. Saidur, H.H. Masjuki, M. Hamdi, Opt. Mater. (Amst). 32, 690 (2010)

M. -Ur-Rahman, G. Yu, T. Soga, T. Jimbo, H. Ebisu, M. Umeno, J. Appl. Phys. 88, 4634 (2000)

K. K. Shih and D. B. Dove, J. Vac. Sci. Technol. A Vacuum, Surfaces, Film. 12, 321 (1994).

P. Singh, R.K. Jha, R.K. Singh, B.R. Singh, Mater. Res. Express 5, 26301 (2018)

P. Singh, R.K. Jha, R.K. Singh, B.R. Singh, Superlattices Microstruct. 121, 55 (2018)

P. Singh, R. K. Jha, R. K. Singh, and B. R. Singh, Phys. Semicond. Devices 517 (2017).

J. Sigman, G.L. Brennecka, P.G. Clem, B.A. Tuttle, J. Am. Ceram. Soc. 91, 1851 (2008)

S.A. Yerişkin, M. Balbaşı, İ. Orak, J. Mater. Sci. Mater. Electron. 28, 7819 (2017)

B. Gabriel, Clin. Sci. 1 (2012).

J.J. Wang, H.B. Huang, T.J.M. Bayer, A. Moballegh, Y. Cao, A. Klein, E.C. Dickey, D.L. Irving, C.A. Randall, L.Q. Chen, Acta Mater. 108, 229 (2016)

L. Zhu and Q. Wang, (2012).

C. Long, Q. Chang, H. Fan, Sci. Rep. 7, 1 (2017)

S. Ma, X. Cheng, Z. Ma, T. Ali, Z. Xu, R. Chu, Ceram. Int. 44, 20465 (2018)

J. Gao, G. He, J.W. Zhang, B. Deng, Y.M. Liu, J. Alloys Compd. 647, 322 (2015)

M. Dawber, K.M. Rabe, J.F. Scott, Rev. Mod. Phys. 77, 1083 (2005)

T. Ali, P. Polakowski, S. Riedel, T. Buttner, T. Kampfe, M. Rudolph, B. Patzold, K. Seidel, D. Lohr, R. Hoffmann, M. Czernohorsky, K. Kuhnel, P. Steinke, J. Calvo, K. Zimmermann, J. Muller, I.E.E.E. Trans, Electron Devices 65, 3769 (2018)

C. Dubourdieu, J. Bruley, T.M. Arruda, A. Posadas, J. Jordan-Sweet, M.M. Frank, E. Cartier, D.J. Frank, S.V. Kalinin, A.A. Demkov, V. Narayanan, Nat. Nanotechnol. 8, 748 (2013)

Acknowledgements

The authors would like to express their sincere thanks to Prof. P. Nagabhushan, Director, Indian Institute of Information Technology, Allahabad for his constant encouragement and support.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Jha, R.K., Singh, P., Goswami, M. et al. Integration of ferroelectric BIT and dielectric HfO2 on silicon substrate with high data retention and endurance for ferroelectric FET applications. Appl. Phys. A 125, 798 (2019). https://doi.org/10.1007/s00339-019-3091-x

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00339-019-3091-x