Abstract

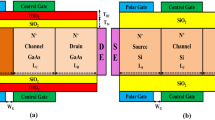

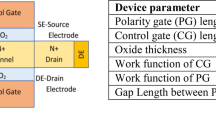

In this research, to achieve steep subthreshold slope, high \({I}_\mathrm{{on}}/{I}_\mathrm{{off}}\) ratio and low ambipolarity in TFETs, we have proposed a device which consists of metal strips near drain–channel and source–channel interfaces. The proposed device is named as dual metal-strip charge plasma-based junction-less tunnel FET (DMS-CP-JL-TFET), which will improve the device performance in terms of DC and analog/RF figure of merits (FOMs). The introduction of a metal strip near the drain–channel interface which produces a wider energy gap reduces ambipolarity, while the metal strip near the source–channel interface delivers abruptness at the junction, leading to a better subthreshold slope and higher \({I}_\mathrm{{on}}/{I}_\mathrm{{off}}\) ratio. Also, positive trap charge (PTC) is taken in the simulations, because the proposed devices have shown great improvement in the presence of PTC, which has also been discussed in this work. In supporting our work, we have added the optimization part for metal strips (M1 and M2) in terms of work functions, lengths to achieve better electrical characteristics.

Similar content being viewed by others

References

M.R. William, A.J.A. Gehan, Silicon surface tunnel transistor. Appl. Phys. Lett. 67(4), 494–496 (1995)

Q. Zhang, W. Zhao, A. Seabaugh, Low-subthreshold-swing tunnel transistors. IEEE Trans. Electron Device Lett. 27(4), 297–300 (2006)

K. Boucart, A.M. Ionescu, Double-gate tunnel FET with high-k gate dielectric. IEEE Trans. Electron Devices 54(7), 1725–1733 (2007)

A.M. Ionescu, H. Riel, Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479(7373), 329–337 (2010)

W.Y. Choi, B.-G. Park, J.D. Lee, T.-J.K. Liu, Tunneling field-effect transistor (TFETs) with subthreshold swing (SS) less than 60 mV/Dec. IEEE Electron Device Lett. 28(8), 743–745 (2007)

S.O. Koswatta, M.S. Lundstrom, D.E. Nikonov, Performance comparison between p-i-n tunneling transistors and conventional MOSFETs. IEEE Trans. Electron Devices 56(3), 456–465 (2007)

N. Damrongplasit, C. Shin, S.H. Kim, R.A. Vega, T.J.K. Liu, Study of random dopant fluctuation effects in germanium-source tunnel FETs. IEEE Trans. Electron Devices 58(10), 3541–3548 (2011)

M.-H. Chiang, J.-N. Lin, K. Kim, C.-T. Chuang, Random dopant fluctuation in limited-width FinFET technologies. IEEE Trans. Electron Devices 54(8), 2055–2060 (2007)

C.L. Royer, F. Mayer, Exhaustive experimental study of tunnel field effect transistors (TFETs): from materials to architecture, in Proc. 10th Inter. Conf. Ultimate Integr. Silicon, pp. 53–56 (2009)

U.E. Avci, D.H. Morris, I.A. Young, Tunnel field effect transistors: prospects and challenges. IEEE J. Electron Devices Soc. 3(3), 88–95 (2015)

D.B. Abdi, M.J. Kumar, Controlling ambipolar current in tunneling FETs using overlapping gate-on-drain. IEEE J. Electron Devices Soc. 2(6), 187–190 (2014)

B. Raad, K. Nigam, D. Sharma, P. Kondekar, Dielectric and work function engineered TFET for ambipolar suppression and RF performance enhancement. Electron. Lett. 52(9), 770–772 (2016)

S. Ghosh, K. Koley, C.K. Sarkar, Impact of the lateral straggle on the analog and RF performance of TFET. Microelectron. Reliab. 55(2), 326–331 (2015)

K. Nigam, P. Kondekar, D. Sharma, DC characteristics and analog/RF performance of novel polarity control GaAs-Ge based tunnel field effect transistor. Superlattices Microstruct. 92, 224–231 (2016)

V. Vijayvargiya, S.K. Vishvakarma, Effect of drain doping profile on double-gate tunnel field-effect transistor and its influence on device RF performances. IEEE Trans. Nanotechnol. 13(5), 978–981 (2014)

W.Y. Choi, W. Lee, Hetero-gate-dielectric tunneling field effect transistors. IEEE Trans. Electron Devices 57(9), 2317–2319 (2010)

M. Jagadesh Kumar, Sindhu Janardhanan, Doping-less tunnel field effect transistor: design and investigation. IEEE Trans. Electron Devices 16(10), 3285–3290 (2013)

B. Ghosh, M.W. Akram, Junctionless tunnel field effect transistor. IEEE Electron Device Lett. 34(5), 584–586 (2013)

Bandi Venkata Chandan, Sushmitha Dasari, S. Yadav, D. Sharma, Approach to suppress ambipolarity and improve RF and linearity performances on ED-tunnel FET. IET Micro Nano Lett. 13, 684–689 (2018)

K. Boucart, A.M. Ionescu et al., Length scaling of the double gate tunnel FET with a high-K gate dielectric. Solid State Electron. 51, 1500–1507 (2007)

ATLAS Device Simulation Software, Silvaco Int, Santa Clara (2016)

C. Shen, L.-T. Yang, G. Samudra, Y.-C. Yeo, A new robust non-local algorithm for band-to-band tunneling simulation and its application to tunnel-FET. Solid State Electron. 57, 23–30 (2011)

P.G.D. Agopian, M.D.V. Martino, S.D. Filho, J.A. Martino, R. Rooyackers, D. Leonelli, C. Claeys, Temperature impact on the tunnel FET off-state current components. Solid State Electron. 78, 141–146 (2012)

W. Shockley, W.T. Read Jr., Statistics of the recombinations of holes and electrons. Phys. Rev. 87, 835–842 (1952)

S. Tirkey, D. Sharma, D.S. Yadav, S. Yadav et al., Analysis of a novel metal implant junctionless tunnel FET for better DC and analog/RF electrostatic parameters. IEEE Trans. Electron Devices 64, 3943–3950 (2017)

B.V. Chandan, M. Gautami, K. Nigam et al., Impact of a metal-strip on a polarity-based electrically doped TFET for improvement of DC and analog/RF performance. J. Comput. Electron. (2018). https://doi.org/10.1007/s10825-018-1280-z

B.V. Chandan, K. Nigam, D. Sharma et al., A novel methodology to suppress ambipolarity and improve the electronic characteristics of polarity-based electrically doped tunnel FET. Appl. Phys. A 125, 81 (2019). https://doi.org/10.1007/s00339-019-2378-2

Farkhanda Ana, Najeeb-ud-din, Gate work function engineering for deep sub-micron MOSFETs: motivation, features and challenges. IJECT 2, 2230–9543 (2011)

R. Lin, Q. Lu, P. Ranade, T.-J. King, C. Hu, An adjustable workfunction technology using Mo gate for CMOS devices. IEEE Electron Device Lett. 23, 49–51 (2002)

Pushkar Ranade et al., Work function engineering of molybdenum gate electrodes by nitrogen implantation. Electrochem. Solid State Lett. 4(11), G85–G87 (2001)

Q. Zeng, X. Zheng et.al., Deposition of dense SiO\(_2\) thin films for electrical insulation applications by microwave ECR plasma source enhanced RF reactive magnetron sputtering, in International Conference on Measuring Technology and Mechatronics Automation (2010). https://doi.org/10.1109/ICMTMA.2010.773

M.Dennis Hausmann, Esther Kim, Jill Becker, Roy G. Gordon, Atomic layer deposition of hafnium and zirconium oxides using metal amide precursors. Am. Chem. Soc. 14, 4350–4358 (2002)

R.W. Johnson, A. Hultqvist, S.F. Bent, A brief review of atomic layer deposition: from fundamentals to applications. Mater. Today. 17(5), 236–246 (2015)

S. Gupta, Kaushal Nigam, S. Pandey, D. Sharma, P.N. Kondekar, Effect of interface trap charges on performance variation of heterogeneous gate dielectric junctionless-TFET. IEEE Trans. Electron Devices 64(11), 4731–4737 (2017)

B. Awadhiya, S. Pandey, Kaushal Nigam, S. Pandey, D. Sharma, P.N. Kondekar, Effect of ITC’s on linearity and distortion performance of junctionless tunnel field effect transistor. Superlattices Microstruct. 111, 293–301 (2017)

Y. Qiu, R. Wang, Q. Huang, R. Huang, A comparative study on the impacts of interface traps on tunneling FET and MOSFET. IEEE Trans. Electron Devices 61(5), 1284–1291 (2014)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Chandan, B.V., Nigam, K., Tirkey, S. et al. Metal-strip approach on junctionless TFET in the presence of positive charge. Appl. Phys. A 125, 665 (2019). https://doi.org/10.1007/s00339-019-2966-1

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00339-019-2966-1