Abstract

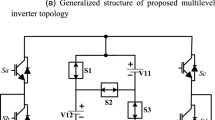

Multilevel inverters (MLIs) have been widely accepted in several industrial applications. The advantages provided by MLI are achieved only through the use of several semiconductor switches and capacitors; consecutively increase the total system cost and complexity. To overcome the above limitations, this article develops a reduced device count hybrid MLI topology. The proposed MLI topology (PMLIT) can produce a 9-level voltage waveform with symmetrical sources and a 7-, 11-level output voltage waveform with asymmetrical sources using a single cell. In addition, PMLIT can be extended to produce any number of voltage levels by cascade connection of the cells with the built-in ability to produce both negative and positive voltage levels. Also, the voltage across the used capacitor is self-balanced without the use of any external components. The comparative investigation reveals the superior characteristics of the PMLIT in terms of the components and total blocking voltage over the newly and conventional topologies. Also, the calculated cost function shows that the PMLIT is more economical than the recently developed topologies. Finally, the viability of the PMLIT has been validated by conducting various tests on the simulation platform and also experimentally for 7, 9, 11 and 81 levels under diverse operating conditions.

Similar content being viewed by others

Data availability

Data not available due to [ethical/legal/commercial] restrictions.

References

Sun X, Wang B, Zhou Y, Wang W, Huiyuan Du, Zhigang Lu (2016) A single dc source cascaded seven-level inverter integrating switched-capacitor techniques. IEEE Trans Ind Electron 63(11):7184–7194

Gupta KK, Ranjan A, Bhatnagar P, Sahu LK, Jain S (2016) Multilevel inverter topologies with reduced device count: a review. IEEE Trans Power Electron 31(1):135–151. https://doi.org/10.1109/TPEL.2015.2405012

Chappa A, Gupta S, Sahu LK, Gupta KK (2021) A fault-tolerant multilevel inverter topology with preserved output power and voltage levels under pre- and postfault operation. IEEE Trans Ind Electron 68(7):5756–5764. https://doi.org/10.1109/TIE.2020.2994880

Chappa A, Gupta S, Sahu LK, Gupta KK (2020) Resilient multilevel inverter topology with improved reliability. IET Power Electron 13(15):3384–3395. https://doi.org/10.1049/iet-pel.2020.0158

Kouro S et al (2010) Recent advances and industrial applications of multilevel converters. IEEE Trans Ind Electron 57(8):2553–2580. https://doi.org/10.1109/TIE.2010.2049719

Buccella C, Cecati C, Cimoroni MG, Kulothungan G, Edpuganti A, Rathore AK (2017) A selective harmonic elimination method for five-level converters for distributed generation. IEEE J Emerg Sel Top Power Electron 5(2):775–783. https://doi.org/10.1109/JESTPE.2017.2688726

Franquelo LG, Rodriguez J, Leon JI, Kouro S, Portillo R, Prats MAM (2008) The age of multilevel converters arrives. IEEE Ind Electron Mag 2(2):28–39. https://doi.org/10.1109/MIE.2008.923519

Abu-Rub H, Holtz J, Rodriguez J, Baoming G (2010) Medium-voltage multilevel converters state of the art, challenges, and requirements in Industrial applications. IEEE Trans Ind Electron 57(8):2581–2596. https://doi.org/10.1109/TIE.2010.2043039

Nabae A, Takahashi I, Akagi H (1981) A new neutral-point-clamped PWM inverter. IEEE Trans Ind Appl 17(5):518–523. https://doi.org/10.1109/TIA.1981.4503992

Zhang L, Waite MJ, Chong B (2013) Three-phase four-leg flying-capacitor multi-level inverter-based active power filter for unbalanced current operation. IET Power Electron 6(1):153–163. https://doi.org/10.1049/iet-pel.2012.0317

Peng FZ, Lai J-S, John M, VanCOevering J (1996) A multilevel voltage-source inverter with separate DC sources for static var generation. IEEE Trans Ind Appl 32(5):1130–1138. https://doi.org/10.1109/28.536875

Jing H, Corzine KA (2006) Extended operation of flying capacitor multilevel inverters. IEEE Trans Power Electron 21(1):140–147. https://doi.org/10.1109/TPEL.2005.861108

Gupta KK, Jain S (2014) Comprehensive review of a recently proposed multilevel inverter. IET Power Electron 7(3):467–479. https://doi.org/10.1049/iet-pel.2012.0438

Mondal G, Gopakumar K, Tekwani PN, Levi E (2007) A reduced-switch-count five-level inverter with common-mode voltage elimination for an open-end winding induction motor drive. IEEE Trans Ind Electron 54(4):2344–2351. https://doi.org/10.1109/TIE.2007.899927

Shalchi Alishah R, Nazarpour D, Hosseini SH, Sabahi M (2015) Reduction of power electronic elements in multilevel converters using a new cascade structure. IEEE Trans Ind Electron 62(1):256–259. https://doi.org/10.1109/TIE.2014.2331012

Alishah RS, Nazarpour D, Hosseini SH, Sabahi M (2014) Novel multilevel inverter topologies for medium and high-voltage applications with lower values of blocked voltage by switches. IET Power Electron 7(12):3062–3071. https://doi.org/10.1049/iet-pel.2013.0670

Ali AIM, Sayed MA, Mohamed EEM, Azmy AM (2019) Advanced single-phase nine-level converter for the integration of multiterminal DC supplies. IEEE J Emerg Sel Top Power Electron 7(3):1949–1958. https://doi.org/10.1109/JESTPE.2018.2868734

Niu D, Gao F, Wang P, Zhou K, Qin F, Ma Z (2020) A nine-level T-type packed U-cell inverter. IEEE Trans Power Electron 35(2):1171–1175. https://doi.org/10.1109/TPEL.2019.2931523

Kala P, Arora S (2021) “Implementation of hybrid GSA SHE technique in hybrid nine-level inverter topology. IEEE J Emerg Sel Top Power Electron 9(1):1064–1074. https://doi.org/10.1109/JESTPE.2019.2963239

Hamidi MN, Ishak D, Zainuri MAAM, Ooi CA (2020) Multilevel inverter with improved basic unit structure for symmetric and asymmetric source configuration. IET Power Electron 13(7):1445–1455. https://doi.org/10.1049/iet-pel.2019.0916

Chappa A, Gupta S, Sahu LK, Gautam SP, Gupta KK (2021) Symmetrical and asymmetrical reduced device multilevel inverter topology. IEEE J Emerg Sel Top Power Electron 9(1):885–896. https://doi.org/10.1109/JESTPE.2019.2955279

MohamedAli JS, Almakhles DJ, AhamedIbrahim SA, Alyami S, Selvam S, Bhaskar MS (2020) A generalized multilevel inverter topology with reduction of total standing voltage. IEEE Access 8:168941–168950. https://doi.org/10.1109/ACCESS.2020.3022040

Toupchi Khosroshahi M (2014) Crisscross cascade multilevel inverter with reduction in number of components. IET Power Electron 7(12):2914–2924. https://doi.org/10.1049/iet-pel.2013.0541

Gupta KK, Jain S (2014) A novel multilevel inverter based on switched dc sources. IEEE Trans Ind Electron 61(7):3269–3278. https://doi.org/10.1109/TIE.2013.2282606

Thamizharasan S, Baskaran J, Ramkumar S, Jeevananthan S (2014) Cross-switched multilevel inverter using auxiliary reverse-connected voltage sources. IET Power Electron 7(6):1519–1526. https://doi.org/10.1049/iet-pel.2013.0606

Hosseinpour M, Seifi A, Rahimian MM (2020) A bidirectional diode containing multilevel inverter topology with reduced switch count and driver. Int J Circuit Theory Appl 48(10):1766–1785. https://doi.org/10.1002/cta.2810

Yahya A, Usman Ali SM, Ghani A (2019) New level doubling architecture of cascaded multilevel inverter. IET Power Electron 12(8):1891–1902. https://doi.org/10.1049/iet-pel.2018.5512

Gautam SP, Kumar L, Gupta S (2015) Hybrid topology of symmetrical multilevel inverter using less number of devices. IET Power Electron 8(11):2125–2135. https://doi.org/10.1049/iet-pel.2015.0037

Mustafa U, Bin Arif MS, Kennel R, Abdelrahem M (2022) Asymmetrical eleven-level inverter topology with reduced power semiconductor switches, total standing voltage and cost factor. IET Power Electron 15(5):395–411. https://doi.org/10.1049/pel2.12238

Alnuman H, Hussan MR, Islam S, Sarwar A, Ahmed EM, Armghan A (2023) A single-source switched-capacitor 13-level high gain inverter with lower switch stress. IEEE Access 11:38082–38093. https://doi.org/10.1109/ACCESS.2023.3266050

Al-Hitmi MA, Hussan MR, Iqbal A, Islam S (2023) Symmetric and asymmetric multilevel inverter topologies with reduced device count. IEEE Access 11:5231–5245. https://doi.org/10.1109/ACCESS.2022.3229087

Siddique MD et al (2021) A new cascaded asymmetrical multilevel inverter based on switched dc voltage sources. Int J Electric Power Energy Syst 128:1–16

Rodriguez J, Bernet S, Wu B, Pontt JO, Kouro S (2007) Multilevel voltage-source-converter topologies for industrial medium-voltage drives. IEEE Trans Ind Electron 54(6):2930–2945. https://doi.org/10.1109/TIE.2007.907044

Qashqai P, Sheikholeslami A, Vahedi H, Al-Haddad K (2015) A review on multilevel converter topologies for electric transportation applications. In: 2015 IEEE vehicle power and propulsion conference (VPPC), Montreal, QC, Canada, pp 1-6. https://doi.org/10.1109/VPPC.2015.7352882

Villanueva E, Correa P, Rodriguez J, Pacas M (2009) Control of a single-phase cascaded h-bridge multilevel inverter for grid-connected photovoltaic systems. IEEE Trans Ind Electron 56(11):4399–4406. https://doi.org/10.1109/TIE.2009.2029579

Iqbal A, Siddique MD, Reddy BP, Maroti PK, Alammari R (2021) A new family of step-up hybrid switched-capacitor integrated multilevel inverter topologies with dual input voltage sources. IEEE Access 9:4398–4410. https://doi.org/10.1109/ACCESS.2020.3046192

Siddique MD et al (2020) Dual asymmetrical dc voltage source based switched capacitor boost multilevel inverter topology. IET Power Electron 13(7):1481–1486

Funding

No funding.

Author information

Authors and Affiliations

Contributions

KKK developed, simulated the proposed topology, wrote the manuscript and experimental results have been taken under the guidance of VS. All authors read and approved the final manuscript.

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interests.

Ethical approval

Not applicable.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Karri, K.K., Singh, V. & Pattnaik, S. Symmetrical and asymmetrical source configured multilevel inverter with reduced device count. Electr Eng 106, 263–277 (2024). https://doi.org/10.1007/s00202-023-01975-4

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00202-023-01975-4