Abstract

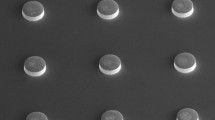

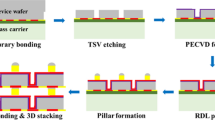

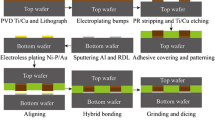

We used the surface planer process to minimize the within-die and within-wafer nonuniformity caused by the nonoptimized Cu pillar and Si thinning processes. The height variation of the planarized Cu pillars was 3.5% of the within-wafer uniformity in a 300-mm wafer, which represents a substantial reduction of the post-electrodeposition height variation. In addition, the topography of the Cu pillar surface was flat and uniform after the surface planer process. The backgrind tape-laminated Cu pillar wafer exhibited a total thickness variation of 31.77 µm. This variation was reduced to 14.55 µm by the surface planer process. The bulk Si of the Cu pillar wafer with the planarized backgrind tape was thinned to 100 µm by grinding. The total thickness variation of the Si was 1.52 µm when the backgrind tape was subjected to the surface planer process, whereas it was 8.2 µm in the case where the surface planer process was not applied. These results indicate that the surface planer process is a promising method for achieving high coplanarity of a die and wafer, thereby representing an advancement toward high-yield advanced packaging.

Similar content being viewed by others

Availability of data and material

All the data shown in this paper is safely stored and available.

Code availability

Not applicable.

References

Che F, Ho D, Ding M, Zhang X (2015) Modeling and design solutions to overcome warpage challenge for fan-out wafer level packaging (FO-WLP) technology. 17th Electronics Packaging Technology Conference, pp 2–8

Chang CS, Oscilowski A, Bracken R (1998) Future challenges in electronic packaging. Circuits & Devices, pp 45–54

Podpod A, Slabbekoorn J, Phommahaxay A, Duval F, Salahouedlhadj A, Gonzalez M, Rebibis K, Miller RA, Beyer G, Beyne E (2018) A novel fan-out concept for ultra-high chip-to-chip interconnect density with 20-µm pitch. 2018 IEEE 68th Electronic Components and Technology Conference, pp 370–378

Srinivasa Rao V, Tai Chong C, Ho D, Mian Zhi D, Ser Choong CS, Lim PS, Ismael D, Yong Liang Y (2016) Development of high density fan out wafer level package (HD FOWLP) with multi-layer fine pitch RDL for mobile applications. 2016 IEEE 66th Electronic Components and Technology Conference, pp 1522–1529

Yang Y, Chou T, Yu T, Chang Y, Huang T, Yang K, Ko C, Chen Y, Tseng T, Chen K (2017) Low-temperature Cu–Cu direct bonding using pillar–concave structure in advanced 3-D heterogeneous integration. IEEE Transactions on Components, Packaging and Manufacturing Technology 7:9

DeProspo B, Liu F, Nair C, Kubo A, Wei F, Chen Y, Sundaram V, Tummala RR (2018) First demonstration of silicon-like >250 I/O per mm per layer multilayer RDL on glass panel interposers by embedded photo-trench and fly cut planarization. 2018 IEEE 68th Electronic Components and Technology Conference, pp 1152–1157

Zihan Dong, Yuanwei Lin (2020) Ultra-thin wafer technology and applications: A review. Mater Sci Semicond Process 105:104681

Öztürk S, Kahraman MF (2019) Modeling and optimization of machining parameters during grinding of flat glass using response surface methodology and probabilistic uncertainty analysis based on Monte Carlo simulation. Measurement 145:274–291

Kahraman MF, Öztürk S (2019) Experimental study of newly structural design grinding wheel considering response surface optimization and Monte Carlo simulation. Measurement 147:106825

Zhang Z, Wanga B, Kang R, Zhang B, Guo D (2015) Changes in surface layer of silicon wafers from diamond scratching. CIRP Ann Manuf Technol 64:349–352

Zhang Z, Huo F, Zhang X, Guo D (2012) Fabrication and size prediction of crystalline nanoparticles of silicon induced by nanogrinding with ultrafine diamond grits. Scripta Mater 67:657–660

Wang B, Zhang Z, Chang K, Cui J, Rosenkranz A, Yu J, Lin C-T, Chen G, Zang K, Luo J, Jiang N, Guo D (2018) New deformation-induced nanostructure in silicon. Nano Lett 18:4611–4617

Zhang Z, Guo D, Wang B, Kang R, Zhang B (2015) A novel approach of high speed scratching on silicon wafers at nanoscale depths of cut. Sci Rep 5:16395

Zhang Z, Huang S, Wang S, Wang B, Bai Q, Zhang B, Kang R, Guo D (2017) A novel approach of high-performance grinding using developed diamond wheels. Int J Adv Manuf Technol 91:3315–3326

Inoue F, Jourdain A, De Vos J, Sleeckx E, Beyne E, Patel J, Ansell O, Ashraf H, Hopkins J, Thomas D, Uedono A (2016) Characterization of extreme Si thinning process for wafer-to-wafer stacking. 2016 IEEE 66th Electronic Components and Technology Conference, pp 2095–2102

Phommahaxay A, Suhard S, Bex P, Iacovo S, Slabbekoorn J, Inoue F, Peng L, Kennes K, Sleeckx E, Beyer G, Beyne E (2019) Enabling ultra-thin die to wafer hybrid bonding for future heterogeneous integrated systems. 2019 IEEE 69th Electronic Components and Technology Conference (ECTC), pp 607–613

Phommahaxay A, Potoms G, Verbinnen G, Sleeckx E, Beyer G, Beyne E, Guerrero A, Bai D, Liu X, Yess K, Arnold K, Spiess W, Griesbach T, Rapps T, Lutter S (2016) Extremely low-force debonding of thinned CMOS substrate by laser release of a temporary bonding material. 2016 IEEE 66th Electronic Components and Technology Conference, pp 1685–1690

Gurnett K, Adams T (2006) Ultra-thin semiconductor wafer applications and processes. III-Vs REVIEW THE ADVANCED SEMICONDUCTOR MAGAZINE 19(4):38–40

Christian B, Bacquian S, Gomez F (2019) A study of wafer backgrinding tape selection for SOI wafers. J Eng Res Rep 6(2):1–6

Christian B, Bacquian S, Gomez F (2020) Effect of backgrinding tape lamination on die alignment. Journal of Engineering Research and Reports 14(4):1–4

Inoue F, Derakhshandeh J, Lofrano M, Beyne E (2021) Fine-pitch bonding technology with surface-planarized solder micro-bump/polymer hybrid for 3D integration. Jpn J Appl Phys 60:026502

Suzuki Y, Hichri H, Wei F, Sundaram V and Tummala R (2017) Embedded trench redistribution layers at 2– 5 µm width and space by excimer laser ablation and surface planer processes for 20– 40 µm I/O pitch interposers. IEEE Transactions on Components, Packaging and Manufacturing Technology 7(6):838–845

Zhang W, Limaye P, Agarwal R, Soussan P (2010) Surface planarization of Cu/Sn micro-bump and its application in fine pitch Cu/Sn solid state diffusion bonding. 2010 IEEE 12th 2010 12th Electronics Packaging Technology Conference (EPTC), pp 143–146

Zhang SJ, Tob S, Zhu ZW, Zhang GQ (2016) A review of fly cutting applied to surface generation in ultra-precision machining. Int J Mach Tools Manuf 103:13–27

Agarwal R, Pham N, Cotrin R, Andrei A, Ruythooren W, Iker F, Soussan P (2009) Diamond bit cutting for processing high topography wafers. 2009 11th Electronics Packaging Technology Conference, pp 267–271

Liu C, Hirano H, Froemel J, Tanaka S (2017) Wafer-level vacuum sealing using AgAg thermocompression bonding after fly-cut planarization. Sensors and Actuators A 261:210–218

Hsiang-Yao H, Ho S-W, Siak Boon Lim S, Leong Ching W, Ser Choong C, Lim S, Siang P, Yong H, Tai Chong C (2019) Ultra-thin FO package-on-package for mobile application. 2019 IEEE 69th Electronic Components and Technology Conference (ECTC), pp 21–27

Sakai T, Imaizumi N, Sakuyama S (2016) Hybrid bonding technology with CU-CU/adhesives for high density 2.5D/3D integration. 2016 Pan Pacific Microelectronics Symposium (Pan Pacific)

He R, Fujino M, Akaike M, Sakai T, Sakuyama S, Suga T (2017) Combined surface activated bonding using H-containing HCOOH vapor treatment for Cu/adhesive hybrid bonding at below 200 °C. Appl Surf Sci 414:163–170

Inoue F, Jourdain A, Peng L, Phommahaxay A, De Vos J, June Rebibis K, Miller A, Sleeckx E, Beyne E, Uedono A (2017) Influence of Si wafer thinning processes on (sub)surface defects. Appl Surf Sci 404:82–87

Inoue F, Podpod A, Peng L, Phommahaxay A, June Rebibis K, Uedono A, Beyne E (2020) Morphological characterization and mechanical behavior by dicing and thinning on direct bonded Si wafer. J Manuf Process 58:811–818

Yang Y, De Munck K, Teixeira RC, Swinnen B, Verlinden B, and De Wolf I (2008) Process induced sub-surface damage in mechanically ground silicon wafers. Semicond Sci Technol 23:7

Pei ZJ, Fisher GR, Liu J (2008) Grinding of silicon wafers: a review from historical perspectives. Int J Mach Tools Manuf 48(12–13):1297–1307

Inoue F, Jourdain A, Visker J, Peng L, Moeller B, Yokoyama K, Phommahaxay A, June Rebibis K, Miller A, Beyne E, Sleeckx E (2017) Edge trimming for surface activated dielectric bonded wafers. Microelectron Eng 167:10–16

Inoue F, Jourdain A, Peng L, Phommahaxay A, Kosemura D, De Wolf I, June Rebibis K, Miller A, Sleeckx E, Beyne E (2018) Edge trimming induced defects on direct bonded wafers. J Electron Packag 140(3):031004

Funding

This study was supported by the IMEC Industrial Affiliation Program (IIAP). However, the partners had no control over the interpretation, writing, or publication of this work.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

All authors declare that (i) no support, financial or otherwise, has been received from any organization that may have an interest in the submitted work and (ii) there are no other relationships or activities that could appear to have influenced the submitted work.

Ethics approval

Not applicable.

Consent to participate

Not applicable.

Consent for publication

All authors have agreed.

Competing interests

The authors declare no competing interests.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Inoue, F., Phommahaxay, A., Gokita, Y. et al. Application of the surface planer process to Cu pillars and wafer support tape for high-coplanarity wafer-level packaging. Int J Adv Manuf Technol 119, 3427–3435 (2022). https://doi.org/10.1007/s00170-021-08622-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00170-021-08622-x