Abstract

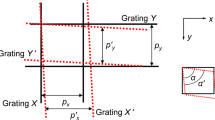

Deformations of a Si-epoxy-FR4 (simplified flip chip) structure under thermal testing were inspected with a real-time Moiré technique. Specimens without cracks and specimens with a crack at the silicon-epoxy interface were prepared. The measurement results showed that the maximum deformation appeared at the edge. When the specimen was cooled to 20 °C, there was residual plastic deformation in the specimen. The creep effect was more dominant in the FR4-epoxy interface. Upon cooling to 20 °C, the specimen experienced partial strain recovery. To characterize the behavior of the interfacial crack, stress intensity factors KI and KII, and the strain energy release rate G in the vicinity of the crack tip were calculated using the measured deformations to conduct a quantitative study. It was observed that a sharp strain gradient occurred at the crack tip. KI and KII were dependent on temperature, and G was dominated by KI for the interfacial crack in the specimen.

Similar content being viewed by others

References

Zhong ZW, Tok WH (2003) Grinding of single-crystal silicon along crystallographic directions. Mater Manuf Process 18(5)811–824

Lau JH (1996) Flip chip technologies. McGraw-Hill, New York

Zhong ZW (2001) Development of a reliable packaging process for flip chip on ceramics. Microelectron Int 18(1)19–22

Zhong ZW (2001) Flip chip assemblies using gold bumps and adhesive. Microelectron Int 18(3)15–19

Zhong ZW (2001) Reliability of flip chips on FR-4 assembled with reduced process steps. Circuit World 27(3):26–30

Zhong ZW (2001) Stud bump bond packaging with reduced process steps. Solder Surf Mount Technol 13(2):35–38

Kuhl A, Qu JM (2000) A technique to measure interfacial toughness over a range of phase angles. J Electron Packag 122:147–151

Lau JH (2000) Low cost flip chip technologies for DCA, WLCSP and PBGA assemblies. McGraw-Hill, New York

Zhong ZW (1999) Assembly and reliability of flip chip on boards using ACAs or eutectic solder with underfill. Microelectron Int 16(3):6–14

Zhong ZW (2001) Reliability of FCOB with and without encapsulation. Solder Surf Mount Technol 13(2):21–25

Lau JH, Lee SWR, Chang C (2000) Effects of underfill material properties on the reliability of solder bumped flip chip on board with imperfect underfill encapsulants. IEEE Trans Compon Packag Technol ogies 23(2):323–332

Darveaux R, Mawer A (1995) Thermal and power cycling limits of plastic ball grid array (PBGA). In: Proceedings of Surface Mount International, 1995, pp 315–325

Darveaux R, Baneji K, Mawer A, Doddoy G (1994) Reliability of ball grid array solder joints. In: Lau JH, ed. Ball grid array technology. McGraw-Hill, New York

Syed A (1997) A review of finite element methods for solder joint analysis. E/NMEP 1

Zhong ZW, Yip PK (2003) Finite element analysis of a three dimensional package. Solder Surf Mount Technol 15(1):21–25

Han B, Guo Y (1995) Thermal deformation analysis of various electronic packaging products by Moiré and microscopic Moiré interferometry. J Electron Packag 117:185–191

Lau JH (1993) Thermal stress and strain in microelectronics packaging. Van Nostrand, New York

Guo Y, Liu S (1998) Development in optical methods for reliability analysis in electronic packaging applications. J Electron Packag 120:186–193

B Han, D Post (1992) Immersion interferometer for microscopic Moiré interferometry. Exp Mech 31(1):38–41

Zhong ZW, Lim SC, Asundi AK, Chai TC (2001) Micro Moiré for thermal deformation investigation in electronics packaging. In: Proceedings of SPIE 4596:256–260

Lu YG, Zhong ZW, Yu J, Xie HM, Ngoi BKA, Chai JB, Asundi A (2001) Thermal deformation measurement of electronic packages using atomic force microscope scanning Moiré technique. Rev Sci Instrum 72(4):2180–2185

Xie HM, Asundi A, Chai GB, Lu YG, Yu J, Zhong ZW, Ngoi BKA (2002) High resolution AFM scanning Moiré method and its application to the micro-deformation in the BGA electronic package. Microelectron Reliab 42:1219–1227

Zhong ZW, Lu YG (2003) An AFM scanning Moiré technique for inspection of surface deformations. Int J Adv Manuf Technol 23(5-6):462–466

Zhong ZW, Nah SK (2003) Thermal strain analysis of an electronics package using the SEM Moiré technique. Solder Surf Mount Technol 15(3):33–35

Zhong ZW, Shi XQ, Wong KW, Wang ZP (2002) Flip chip interfacial behavior under thermal testing. In: Proceedings of 4th Electronics Packaging Technology Conference, , 2002, pp 56–59

Post D, Han B, Ifju P (1993) High sensitivity Moiré: experimental analysis for mechanics and materials. Springer, Berlin Heidelberg New York

Zhang W, Wu D, Su B, Hareb SA, Lee YC, Materson BP (1998) The effect of underfill epoxy on warpage in flip chip assemblies. IEEE Trans Compon Packag Manuf Technol 21(2):323–328

Hanna CE, Sitaraman SK (1999) Role of underfill materials and thermal cycling on die stresses. Adv Electron Packag 26(1):795–801

Miller MR, Mohammed I, Ho PS (2001) Quantitative strain analysis of flip chip electronic packages using phase-shifting Moiré interferometry. Opt Lasers Eng 36:127–139

Hutchinson JW, Suo Z (1992) Mixed mode cracking in layered materials. Adv Appl Mech 29:64–187

Lau JH, Lee SWR (2000) Fracture mechanics analysis of low cost solder bumped flip chip assemblies with imperfect underfills. J Electron Packag 122:306–310

Rice JR (1988) Elastic fracture mechanics concepts for interfacial cracks. J Appl Mech 55:98–103

Malyshev BM, Salganik RL (1965) The strength of adhesive joints using the theory of cracks. Int J Fract Mech 1:114–128

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Zhong, Z., Wong, K. & Shi, X. Deformations of a simplified flip chip structure under thermal testing inspected using a real-time Moiré technique. Int J Adv Manuf Technol 27, 708–714 (2006). https://doi.org/10.1007/s00170-004-2245-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00170-004-2245-x