Abstract

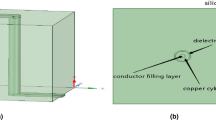

In this paper, a co-optimization design method for thermal-stress coupling 3-dimensional integrated system with through silicon via is proposed based on the finite element method, support vector machine model and modified particle swarm optimization algorithm. In the cause of analyzing the effects of geometrical parameters (radius of through silicon via, oxide thickness and the height of oxide insolation layer) on the thermal-stress distribution, the finite element method based COMSOL software is conducted to simulate the thermal-stress coupling 3-dimensional integrated system. Based on the simulation data obtained by COMSOL, the support vector machine models are adopted to establish the database for describing the relationships between the geometrical parameters and key indexes (peak temperature, peak stress and temperature difference) to improve the design efficiency. Based on the desired key indexes of thermal-stress coupling 3-dimensional integrated system, the multi-objective evaluation function is formulated. Then, the geometrical parameters are optimized by the modified particle swarm optimization algorithm. The finite element simulation is conducted to verify the effectiveness of the proposed strategy. In three cases, the errors between the simulated and desired temperature differences are all less than 0.28 K, and the relative errors between the simulated and desired peak temperature/peak stress are all less than 4.78%, which indicates that the geometrical parameters can be optimized to control the key indexes of thermal-stress coupling 3-dimensional integrated system. Therefore, the developed method can be used in the design and manufacture of 3-dimensional integrated system.

Similar content being viewed by others

Abbreviations

- d :

-

Degree of the polynomial kernel function

- c :

-

Offset of polynomial kernel function

- s :

-

Width of Gauss kernel function

- r :

-

Radius of through silicon via unit

- t ox :

-

Oxide thickness

- h 1 :

-

Height of oxide isolation layer

- AARE:

-

Absolute average relative error

- PT:

-

Peak temperature

- PS:

-

Peak stress

- TD:

-

Temperature difference

- α:

-

Weight coefficient of peak temperature

- β:

-

Weight coefficient of peak stress

- γ:

-

Weight coefficient of temperature difference

- v i :

-

Velocity of the ith particle

- x i :

-

Position of the ith particle

- x r , x tox , x hl :

-

Range of particle position

- v r , v tox , v hl :

-

Range of particle velocity

- w :

-

Inertia weight

- p i :

-

Best previous positions of the ith particle

- p g :

-

Best previous positions of all particles

- C 1 , C 2 :

-

Constants to determine the weights of pi and pg

- r 1 , r 2 :

-

Two random values

- iter :

-

Current iteration

- iter max :

-

Maximum of the current iteration

- w max :

-

Maximum of inertia weight

- w min :

-

Minimum of inertia weight

- N :

-

Population size

- M G :

-

Maximum generation

References

Barroso ES, Parente E, Cartaxo de Melo AM (2017) A hybrid PSO-GA algorithm for optimization of laminated composites. Struct Multidisc Optim 55:2111–2130. https://doi.org/10.1007/s00158-016-1631-y

Chen Q, Zhang D, Xu Z, Beece A, Patti R, Tan Z, Wang Z, Liu L, Jian-Qiang Lu (2012) A novel chip-to-wafer (C2W) three-dimensional (3D) integration approach using a template for precise alignment. Microelectron Eng 92:15–18. https://doi.org/10.1016/j.mee.2011.04.047

Chen D, Lin Y, Wu F (2019a) A design framework for optimizing forming processing parameters based on matrix cellular automaton and neural network-based model predictive control methods. Appl Math Model 76:918–937. https://doi.org/10.1016/j.apm.2019.07.023

Chen DD, Lin YC, Chen XM (2019b) A strategy to control microstructures of a ni-based superalloy during hot forging based on particle swarm optimization algorithm. Adv in Manuf 7(2):238–247. https://doi.org/10.1007/s40436-019-00259-0

Chen DD, Zhao JX, Fei CL, Li D, Zhu YB, Li ZX, Guo R, Lou LF, Feng W, Yang YT (2020) Particle swarm optimization algorithm-based design method for ultrasonic transducers. Micromachines 11(8):715. https://doi.org/10.3390/mi11080715

Chen Z, Song X, Liu S (2009) Thermo-mechanical characterization of copper filled and polymer filled tsvs considering nonlinear material behaviors. 2009 59th Electronic Components and Technology Conference 1374–1380. https://doi.org/10.1109/ECTC.2009.5074192

Cheng K, Lu ZZ, Zhou YC, Shi Y, Wei YH (2017) Global sensitivity analysis using support vector regression. Appl Math Model 49:587–598. https://doi.org/10.1016/j.apm.2017.05.026

Cheng Z, Ding Y, Xiao L, Wang X, Chen Z (2019) Comparative evaluations on scallop-induced electric-thermo-mechanical reliability of through-silicon-vias. Microelectron Reliab 103:113512. https://doi.org/10.1016/j.microrel.2019.113512

Choa SH, Song CG, Lee HS (2011) Investigation of durability of TSV interconnect by numerical thermal fatigue analysis. Int J Precis Eng Manuf 12:589–596. https://doi.org/10.1007/s12541-011-0076-x

Dai HP, Chen DD, Zheng ZS (2018) Effects of random values for particle swarm optimization algorithm. Algorithms 11(2):23. https://doi.org/10.3390/a11020023

Dixit Pradeep, Sun Y, Miao J, Pang John HL, Chatterjee Ritwik, Rao R, Tummala (2008) Numerical and experimental investigation of thermomechanical deformation in high-aspect-ratio electroplated through-silicon vias. J Electrochem Soc 155(12):H981. https://doi.org/10.1149/1.2994154

Dong C, Chen C, Haruehanroengra S, Wang W (2007) 3-D nFPGA: a reconfigurable architecture for 3-D CMOS/Nanomaterial hybrid digital circuits. IEEE T Circuits-I 54(11):2489–2501. https://doi.org/10.1109/TCSI.2007.907844

Dukovic J, Ramaswami S, Pamarthy S, Yalamanchili R, Rajagopalan N, Sapre K, Cao Z, Ritzdorf T, Wang Y, Eaton B, Ding R, Hernandez M, Naik M, Mao D, Tseng J, Cui D, Mori G, Fulmer P, Sirajuddin K, Hua J, Xia S, Erickson D, Beica R, Young E, Kulzer R, Oemardani S, Dai H, Xu X, Okazaki M, Dotan K, Yu C, Lazik C, Tran J, Luo L (2010) Through-silicon-via technology for 3D integration. 2010 IEEE International Memory Workshop https://doi.or/https://doi.org/10.1109/IMW.2010.5488399

Fang Z, You P, Jia Y, Pan X, Shi Y, Jiao J, He Y (2021) Wafer-level 3D integration based on poly (Diallyl Phthalate) adhesive bonding. Micromachines 12:1586. https://doi.org/10.3390/mi12121586

Fengmin Xu, Shanhe W (2013) A hybrid simulated annealing thresholding algorithm for compressed sensing. Signal Process 93(6):1577–1585. https://doi.org/10.1016/j.sigpro.2012.10.019

Gomes W, Khushu S, Ingerly D, Stover P, Chowdhury N, O’Mahony F, Balankutty A, Dolev N, G. Dixon M, Jiang L, Prekke S, Patra B, V. Rott P, Kumar R (2020) 8.1 Lakefield and Mobility Compute: A 3D Stacked 10nm and 22FFL Hybrid Processor System in 12×12mm2, 1mm Package-on-Package. 2020 IEEE International Solid- State Circuits Conference - (ISSCC) 144–146. https://doi.org/10.1109/ISSCC19947.2020.9062957

He DG, Lin YC, Chen J, Chen DD, Huang J, Tang Y, Chen MS (2018) Microstructural evolution and support vector regression model for an aged Ni-based superalloy during two-stage hot forming with stepped strain rates. Mater Des 154:51–62. https://doi.org/10.1016/j.matdes.2018.05.022

Hopcroft MA, Nix WD, Kenny TW (2010) What is the young’s modulus of silicon? J Microelectromech S 19(2):229–238. https://doi.org/10.1109/JMEMS.2009.2039697

Hsieh M, Yu C (2008) Thermo-mechanical simulations for 4-layer stacked IC packages. EuroSimE 2008—International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Micro-Systems 1–7. https://doi.org/10.1109/ESIME.2008.4525007

Ingerly D, Amin S, Aryasomayajula L, Balankutty A, Borst D, Chandra A, Cheemalapati K, Cook C, Criss R, Enamul1 K, Gomes W, Jones D, Kolluru K, Kandas A, Kim G, Ma H, Pantuso D, Petersburg C, Phen-givoni M, Pillai A, Sairam A, Shekhar P, Sinha P, Stover P, Telang A, and Zell Z (2019) Foveros: 3D Integration and the use of Face-to-Face Chip Stacking for Logic Devices. IEEE International Electron Devices Meeting (IEDM) 19.6.1–19.6.4. https://doi.org/10.1109/IEDM19573.2019.8993637

Jung M, Liu X, Sitaraman SK, Pan DZ, Lim SK (2011) Full-chip through-silicon-via interfacial crack analysis and optimization for 3D IC. 2011 IEEE/ACM International Conference on Computer-Aided Design (ICCAD) 563-570. https://doi.org/10.1109/ICCAD.2011.6105386

Kang U, Chung H, Heo S, Park D, Lee H, Kim J, Ahn S, Cha S, Ahn J, Kwon D, Lee J, Joo H, Kim W, Jang D, Kim N, Choi J, Chung T, Yoo J, Choi J, Kim C, Jun Y (2010) 8 Gb 3-D DDR3 DRAM Using through-silicon-via technology. IEEE J Solid-State Circuits 45(1):111–119. https://doi.org/10.1109/JSSC.2009.2034408

Ladani LJ (2010) Numerical analysis of thermo-mechanical reliability of through silicon vias (TSVs) and solder interconnects in 3-dimensional integrated circuits. Microelectron Eng 87(2):208–215. https://doi.org/10.1016/j.mee.2009.07.022

Lau JH (2014) Overview and outlook of three-dimensional integrated circuit packaging, three-dimensional Si Integration, and three-dimensional integrated circuit integration. ASME J Electron Packag 136(4):040801. https://doi.org/10.1115/1.4028629

Lee JS, Park CH (2010) Hybrid simulated annealing and its application to optimization of hidden markov models for visual speech recognition. IEEE Trans Syst Man Cy-s 40(4):1188–1196. https://doi.org/10.1109/TSMCB.2009.2036753

Lee I, Cheong M, Kang S (2019) Highly reliable redundant TSV architecture for clustered faults. IEEE Trans Reliab 68(1):237–247. https://doi.org/10.1109/TR.2018.2864591

Lee J, Lee C, Kim C, and Kalchuri S (2018) Micro Bump System for 2nd Generation Silicon Interposer with GPU and High Bandwidth Memory (HBM) Concurrent Integration. IEEE 68th Electronic Components and Technology Conference (ECTC) 607–612. https://doi.org/10.1109/ECTC.2018.00096

Liu IS (1990) On Fourier’s law of heat conduction. Continuum Mech Thermodyn 2:301–305. https://doi.org/10.1007/BF01129123

Liu C, Ganusov I, Burtscher M, Tiwari S (2005) Bridging the processor-memory performance gap with 3D IC technology. IEEE Des Test Comput 22(6):556–564. https://doi.org/10.1109/MDT.2005.134

Liu X, Chen Q, Dixit P, Chatterjee R, Tummala RR, Sitaraman SK (2009) Failure mechanisms and optimum design for electroplated copper Through-Silicon Vias (TSV). 2009 59th Electronic Components and Technology Conference 624–629. https://doi.org/10.1109/ECTC.2009.5074078

Liu X, Zhu Z, Yang Y, Ding R (2016) Low-loss air-cavity through-silicon vias (TSVs) for high speed three-dimensional integrated circuits (3-D ICs). IEEE Microw Wirel Compon Lett 26(2):89–91. https://doi.org/10.1109/LMWC.2016.2517325

Loh GH, Naffziger S and Lepak K (2021) Understanding Chiplets Today to Anticipate Future Integration Opportunities and Limits. 2021 Design, Automation & Test in Europe Conference & Exhibition (DATE) 142–145. https://doi.org/10.23919/DATE51398.2021.9474021

Lu KH, Zhang X, Ryu SK, Im J, Huang R, Ho PS (2009) Thermo-mechanical reliability of 3-D ICs containing through silicon vias. 2009 59th Electronic Components and Technology Conference 630–634. https://doi.org/10.1109/ECTC.2009.5074079

Ly W, Li L, Zhang Zh (2016) Accurate descriptions of hot flow behaviors across β transus of Ti-6Al-4V alloy by intelligence algorithm GA-SVR. J Mater Eng Perform 25:3912–3923. https://doi.org/10.1007/s11665-016-2230-1

Mesbahi A, Semnani D, Khorasani S (2012) Performance prediction of a specific wear rate in epoxy nanocomposites with various composition content of polytetrafluoroethylen (PTFE), graphite, short carbon fibers (CF) and nano-TiO2 using adaptive neuro-fuzzy inference system (ANFIS). Compos Part B-Eng 43(2):549–558. https://doi.org/10.1016/j.compositesb.2011.11.026

Mokarram V, Banan MR (2018) A new PSO-based algorithm for multi-objective optimization with continuous and discrete design variables. Struct Multidisc Optim 57:509–533. https://doi.org/10.1007/s00158-017-1764-7

Park J, Cheong M, Kang S (2017) R2-TSV: a repairable and reliable TSV set structure reutilizing redundancies. IEEE Trans Reliab 66(2):458–466. https://doi.org/10.1109/TR.2017.2681103

Qian L, Xia Y, He X, Qian K, Wang J (2018a) Electrical modeling and characterization of silicon-core coaxial through-silicon vias in 3-D integration. IEEE Trans Compon Packaging Manuf Technol 8(8):1336–1343. https://doi.org/10.1109/TCPMT.2018.2854829

Qian L, Sang J, Xia J, Wang J, Zhao P (2018b) Investigating on through glass via based RF passives for 3-D integration. IEEE J Electron Devices Soc 6:755–759. https://doi.org/10.1109/JEDS.2018.2849393

Qian L, Qian K, He X, Chu Z, Ye Y, Shi G, Xia Y (2019) Through-silicon via-based capacitor and its application in LDO regulator design. IEEE Trans VLSI Syst 27(8):1947–1951. https://doi.org/10.1109/TVLSI.2019.2904200

Qu C, Ding R, Liu X, Zhu Z (2017) Modeling and optimization of multiground TSVs for signals shield in 3-D ICs. IEEE Trans Electromagn Compat 59(2):461–467. https://doi.org/10.1109/TEMC.2016.2608981

Ranganathan N, Prasad K, Balasubramanian N, Pey KL (2008) A study of thermo-mechanical stress and its impact on through-silicon vias. J Micromech Microeng 18(7):075018. https://doi.org/10.1088/0960-1317/18/7/075018

Rao X, Song J, Tian Q, Liu H, Jin C, Xiao C (2022) A universal and efficient equivalent modeling method for thermal analysis of 3D ICs containing tapered TSVs. Int Commun Heat Mass 136:106161. https://doi.org/10.1016/j.icheatmasstransfer.2022.106161

Rassoul N, Jourdain A, Tutunjyan N, De Vos J, Sardo S, Inoue F, Piumi D, Beyer G, Miller A, Beyne E, Walsby E, Patel J, Ansel O, Ashraf H, Hopkins J, Thomas D (2018) RIE dynamics for extreme wafer thinning applications. Microelectron Eng 192:30–37. https://doi.org/10.1016/j.mee.2018.02.001

Ren Z, Alqahtani A, Bagherzadeh N, Lee J (2020) Thermal TSV optimization and hierarchical floorplanning for 3-D integrated circuits. IEEE Trans Compon Packaging Manuf Technol 10(4):599–610. https://doi.org/10.1109/TCPMT.2020.2970382

Selvanayagam C, Zhang X, Rajoo R, Pinjala D (2011) Modeling stress in silicon with TSVs and its effect on mobility. IEEE Trans Compon Packaging Manuf Technol 1(9):1328–1335. https://doi.org/10.1109/TCPMT.2011.2158002

Shabany Y (2009) Heat Transfer Thermal Management of Electronics, 1st edn. CRC Press, Boca Raton. https://doi.org/10.1201/9781439814680

Shulaker Max M, Hills G, Park RS, Howe RT, Saraswat K, Philip Wong HS, Mitra S (2017) Three-dimensional integration of nanotechnologies for computing and data storage on a single chip. Nature 547:74–78. https://doi.org/10.1038/nature22994

Tang Q, Eberhard P (2011) A PSO-based algorithm designed for a swarm of mobile robots. Struct Multidisc Optim 44:483–498. https://doi.org/10.1007/s00158-010-0618-3

Thakur S, Nakanekar S, Kaisare A, Tonapi S (2011) Design for reliability of stacked die package using TSV technology. Proc Int Electron Packag Tech Conf Exhib 44618:75–82. https://doi.org/10.1115/IPACK2011-52264

Tsai HY, Kuo CW (2016) Thermal stress and failure location analysis for through silicon via in 3D integration. J Mech 32(1):47–53. https://doi.org/10.1017/jmech.2015.52

Wang XL, Li D, Chen DD, Zhang QD, Yang YT (2022a) A precise ultra-wideband ranging method using pre-corrected strategy and particle swarm optimization algorithm. Measurement 194:110966. https://doi.org/10.1016/j.measurement.2022.110966

Wang XL, Yang YT, Li D, Chen DD, Zhang QD (2022b) An improved indoor 3-D Ultrawideband positioning method by particle swarm optimization algorithm. IEEE Trans Instrum Meas 71(1005211):1–11. https://doi.org/10.1109/TIM.2022.3192252

Wang XL, Yang YT, Chen DD, Li D (2022c) A High-efficiency design method of TSV array for thermal management of 3D integrated system. IEEE T Comput Aid D. https://doi.org/10.1109/TCAD.2022.3213610

Acknowledgements

This work was supported by the Fundamental Research Funds for the Central Universities (No: QTZX23022), the Innovation Fund of Xidian University (No: YJSJ23019), Youth Talent Fund of Joint Fund of the Ministry of Education for Equipment Pre-Research (No: 8091B032138), the National Natural Science Foundations of China (No: 62104177), the Equipment Pre-research Project of China (No:80924020307), and the Cooperation Program of XDU-Chongqing IC Innovation Research Institute (No: CQIRI-2022CXY-Z01).

Funding

Fundamental Research Funds for the Central Universities, QTZX23022, Dongdong Chen, the Innovation Fund of Xidian University, YJSJ23019, Xianglong Wang, Youth Talent Fund of Joint Fund of the Ministry of Education for Equipment Pre-Research, 8091B032138, Dongdong Chen, National Natural Science Foundations of China,62104177, Dongdong Chen,Equipment Pre-research Project of China, 80924020307, Dongdong Chen,Cooperation Program of XDU-Chongqing IC Innovation Research Institute, CQIRI-2022CXY-Z01, Di Li

Author information

Authors and Affiliations

Contributions

XW and DC wrote the manuscript with support from DL and YY generated the simulation results. DC (ddchen@xidian.edu.cn) and DL (lidi2004@126.com) supervised the project, and they are co-corresponding authors of this paper.

Corresponding author

Ethics declarations

Competing interest

On behalf of all authors, the corresponding author states that there is no conflict of interest.

Replication of results

The current work is part of a confidential project. Therefore, the developed codes cannot be disclosed at present.

Additional information

Responsible Editor: Palaniappan Ramu

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Wang, X., Chen, D., Li, D. et al. A co-optimization method of thermal-stress coupling 3D integrated system with through silicon via. Struct Multidisc Optim 66, 251 (2023). https://doi.org/10.1007/s00158-023-03706-6

Received:

Revised:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00158-023-03706-6