Abstract

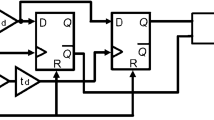

The phase frequency detector (PFD) is an important component in a phase-locked loop (PLL). PFD detects the timing difference between the reference clock (REFCK) and the feedback clock (FBCK). PFD plays a major role in deciding the amount of time required by a PLL to achieve lock. The blind zone in the PFD causes inaccurate PFD output. This negatively impacts the PLL’s lock-in time. The increase in lock-in time poses great challenges for developing high-speed PLLs. This paper proposes a PFD architecture that eliminates the reset pulse when the timing difference between the REFCK and the FBCK is significantly high. The elimination of the reset pulse in this way leads to a blind zone free PFD across process, voltage, and temperature (PVT) variations. The PFD is realized and implemented in the Cadence spectre environment using the UMC 0.18 \(\upmu \)m CMOS process. From the results, it can be stated that the designed PFD is blind zone free across PVT variations. The proposed PFD-based PLL locks faster than the traditional PFD-based PLL. The proposed PFD consumes 163 \(\upmu \)W power at a 100 MHz operating frequency which is the lowest compared to the earlier reported works. Its operational range is [\(-2\pi ,2\pi \)]. The PFD occupies an area of 0.0069 \(\textrm{mm}^2\). The proposed design is well suited to low-power, high-speed PLL applications.

Similar content being viewed by others

Availability of data and materials

The datasets generated during and/or analyzed during the current study are available from the corresponding author on reasonable request.

References

A. Abolhasani, M. Mousazadeh, A. Khoei, A high-speed, power efficient, dead-zone-less phase frequency detector with differential structure. Microelectron. J. 97, 104719 (2020)

T. Ahmed, N. Tasneem, R. M. Walker, A 250–600 MHz ring oscillator-based phase-locked loop for implantable wireline applications, using 1.0 V supply in 180 nm CMOS, in 2021 19th IEEE International New Circuits and Systems Conference (NEWCAS) (2021), pp. 1–4. https://doi.org/10.1109/NEWCAS50681.2021.9462757

R.E. Best, Phase-Locked Loops: Design, Simulation, and Applications (McGraw-Hill Professional, New York, 2007)

M.B. Castro, R.R.N. Souza, A.M.P. Junior, E.R. Lima, L.T. Manera, Phase locked loop-based clock synthesizer for reconfigurable analog-to-digital converters. Analog Integr. Circuits Signal Process. 109(3), 647–656 (2021)

W.-H. Chen, M.E. Inerowicz, B. Jung, Phase frequency detector with minimal blind zone for fast frequency acquisition. IEEE Trans. Circuits Syst. II: Express Br. 57(12), 936–940 (2010)

M. Divya, K. Sundaram, Dead zone-less low power phase frequency detector, independent of duty cycle variations for charge pump phase locked loop. Analog Integr. Circuits Signal Process. 114, 13–30 (2023)

M. Divya, K. Sundaram, A novel blind zone free, low power phase frequency detector for fast locking of charge pump phase locked loops, in 3rd International Conference, ICMDCS 2022, Vellore, India (2022), pp. 117–128

X. Gao, E.A.M. Klumperink, P.F.J. Geraedts, B. Nauta, Jitter analysis and a benchmarking figure-of-merit for phase-locked loops. IEEE Trans. Circuits Syst. II: Express Br. 56(2), 117–121 (2009)

M. Gholami, Phase detector with minimal blind zone and reset time for GSamples/s DLLs. Circuits Syst. Signal Process. 36(9), 3549–3563 (2017)

A.M. KK, B.J. Kailath, PLL architecture with a composite PFD and variable loop filter. IET Circuits Dev. Syst. 12(3), 256–262 (2018)

H.L. Kirankumar, S. Rekha, T. Laxminidhi, A dead-zone-free zero blind-zone high-speed phase frequency detector for charge-pump PLL. Circuits. Syst. Signal Process. 39(8), 3819–3832 (2020)

A. Koithyar, T.K. Ramesh, A faster phase frequency detector using transmission gate-based latch for the reduced response time of the PLL. Int. J. Circuit Theory Appl. 46(4), 842–854 (2018)

S.S. Kuncham, M. Gadiyar, K. Sushmitha Din, K.K. Lad, T. Laxminidhi, A novel zero blind zone phase frequency detector for fast acquisition in phase locked loops, in 2018 31st International Conference on VLSI Design and 2018 17th International Conference on Embedded Systems (VLSID) (2018), pp. 167–170. https://doi.org/10.1109/VLSID.2018.56

J. Lan, Y. Wang, L. Liu, R. Li, A nonlinear phase frequency detector with zero blind zone for fast-locking phase-locked loops, in 2010 International Conference on Anti-Counterfeiting, Security and Identification (2010), pp. 41–44

D.-G. Lee, P.P. Mercier, A sub-mW 2.4-GHz active-mixer-adopted sub-sampling PLL achieving an FoM of \(-256\) dB. IEEE J. Solid-State Circuits 55(6), 1542–1552 (2019)

K.K.A. Majeed, B.J. Kailath, Low power, high frequency, free dead zone PFD for a PLL design, in 2013 IEEE Faible Tension Faible Consommation, pp. 1–4 (2013)

R.H. K, J. Mukherjee, PFD with improved average gain and minimal blind zone combined with lock-in detection for fast settling PLLs. Microelectron. J. 116, 105233 (2021)

G. Nikolić, G. Jovanović, M. Stojčev, T. Nikolić, Precharged phase detector with zero dead-zone and minimal blind-zone. J. Circuits Syst. Comput. 26(11), 1750179 (2017)

N. Pradhan, S.K. Jana, Improved Phase Noise Performance of PFD/CP Operating in 1.5 MHz–4.2 GHz for Phase-Locked Loop Application. Circuits. Syst. Signal Process 41(12), 6651–6671 (2022)

H.K. Ravi, S. Tiwari, J. Mukherjee, A new architecture of the phase frequency detector with improved gain and minimal blind zone for fast settling PLLs, in 2020 IEEE International Symposium on Circuits and Systems (ISCAS) (2020), pp. 1–5

B. Razavi, Design of CMOS Phase-Locked Loops: From Circuit Level to Architecture Level (Cambridge University Press, UK, 2020)

A. Rezaeian, G. Ardeshir, M. Gholami, A low-power and high-frequency phase frequency detector for a 3.33-GHz delay locked loop. Circuits. Syst. Signal Process 39(4), 1735–1750 (2020)

A. Sai, T. Yamaji, T. Itakura, A low-jitter clock generator based on ring oscillator with 1/f noise reduction technique for next-generation mobile wireless terminals, in 2008 IEEE Asian Solid-State Circuits Conference (2008), pp. 425–428

Z.M. Saifullah, P.M. Furth, S. Pakala, A. Roman-Loera, Frequency-to-voltage converter based dual-loop phase-locked loop with variable phase locking capability. Electron. Lett. 58(25), 943–945 (2022)

H.G. Shettar, S. Kotabagi, N. Shanbhag, S. Naik, R. Bagali, S. Nandavar, Frequency multiplier using phase-locked loop, in 2020 IEEE 17th India Council International Conference (INDICON) (2020), pp. 1–5

S. Sofimowloodi, F. Razaghian, M. Gholami, Low-power high-frequency phase frequency detector for minimal blind-zone phase-locked loops. Circuits. Syst. Signal Process. 38(2), 498–511 (2019)

P.S. Volobuev, R.A. Fedorov, M.V. Poryadina, D.I. Ryzhova, S. Gavrilov, A low-jitter 300 MHz CMOS PLL for double data rate applications, in 2019 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (EIConRus) (2019), pp. 1631–1635

Funding

No funding was received to assist with the preparation of this manuscript.

Author information

Authors and Affiliations

Contributions

All authors reviewed the manuscript. Kumaravel Sundaram contributed to the study conception. The design and analysis were performed by Marichamy Divya. The first draft of the manuscript was written by Marichamy Divya, and all authors commented on previous versions of the manuscript. All authors read and approved the final manuscript.

Corresponding author

Ethics declarations

Conflict of interest

The authors have no competing interests to declare that are relevant to the content of this article.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Divya, M., Sundaram, K. Blind Zone-Less Phase Frequency Detector for a Low-Power Phase-Locked Loop Architecture. Circuits Syst Signal Process 42, 6399–6419 (2023). https://doi.org/10.1007/s00034-023-02413-3

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-023-02413-3