Abstract

Second-generation voltage conveyor structures, based on the employment of flipped voltage follower stages, are investigated and proposed in this work. The proposed core has the feature of offering extremely low or electronically adjustable input resistance and programmable outputs, enhancing the achieved design flexibility and versatility of this active cell. Two design examples are presented in this work, including a multi-phase sinusoidal oscillator topology and an electronically adjustable first-order low-pass filter, both supported by simulation and experimental results.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The second-generation voltage conveyors (VCIIs) are attractive alternatives of second-generation current conveyors (CCIIs) and this is originated from the fact that they offer a low-impedance output terminal, allowing their direct interconnection with other stages for implementing analog signal processing systems [21]. A significant number of such active cells have been already introduced in the literature, and they have been employed in several applications, including filters, capacitance multipliers, inductance emulators and oscillators [1,2,3, 13, 17, 18, 20, 22, 28, 29, 31, 34, 35]. One of the requirements that VCII must fulfill is the extremely low resistance at its terminals Y and Z. The topology in [29] offers such features with relatively low circuit complexity, but it suffers from the different dc levels at these terminals. There are also applications where external resistors could be substituted by the inherent (i.e., parasitic) resistance of the terminal Y, providing electronic adjustment capability of the derived structures, which is an attractive feature of nowadays systems. The VCII structures in [2, 17, 18] offer electronic adjustable parasitic impedance at node Y, but they suffer from the non-zero resistance at the output terminal Z and, also, from the increased circuit complexity. The VCII topology in [32] offers a relatively simple circuitry with electronically controlled resistance at node Y and an extremely low resistance at terminal Z, but the problem there is that the terminal Z is at a different dc level than that of the other terminals of VCII. A relatively simple VCII structure which offers extremely low resistances at both terminal Y and Z, without having different dc levels between these terminals, is presented in this work. An attractive feature of this topology is that it can be easily transposed into an electronically controllable structure, just by changing the point where the Y terminal is fed, providing design flexibility and versatility. This is achieved without losing the aforementioned features.

The paper is organized as follows: the basic structure is presented in Sect. 2, where possible enhancements for further increasing its usefulness are also provided. The performance of the proposed core is evaluated and compared with that of the already published relevant structures in Sect. 3 in order for the added value to be evident. A programmable multi-phase sinusoidal oscillator (MSO) topology and a first-order low-pass filter design are presented and evaluated in Sect. 4, as design examples.

2 Flipped Voltage Follower-Based Second-Generation Voltage Conveyors

2.1 Proposed Topology of FVF-Based VCII

The symbol of a VCII is provided in Fig. 1, and the matrix equation which describes its behavior is the following:

The current conveying operation in (1) between terminals Y and X is described by the factor \(+\alpha \) for a VCII+, and by the opposite one in the case of a VCII-; the factor \(\beta \) describes the voltage conveying operation between terminals X and Z. In addition, \(C_{X}\) are \(r_{X}\) are the inherent (parasitic) capacitance and resistance associated with the terminal X, and \(r_{Y},r_{Z}\) are the inherent resistances of terminals X and Z, respectively. For an ideal VCII, i.e., \(\alpha =1\), \(\beta =1\), \(r_{Y}=0,r_{X}\rightarrow \infty \), \(r_{Z}=0\), and \(C_{X}=0\).

The FVF is an attractive stage for achieving the goal of the minimum input resistances at nodes Y and Z, and this is originated from the fact that the implemented resistances are scaled versions of the basic resistance \(1/g_{m}\), with \(g_{m}\) being the transconductance parameter of a MOS transistor [4].

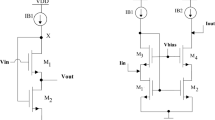

Such a topology with nMOS-pMOS conversion, introduced in [29], is depicted in Fig. 2.

Thanks to the employment of FVF in stages associated with the terminals Y and Z, the corresponding inherent resistances are

Inspecting (2)–(3), it is readily obtained that the “effective” transconductance seen from terminals Y and Z is scaled by a factor \(g_{m}r_{0}\), and therefore, the corresponding input resistances are reduced by the same factor. This is a benefit with regard to the convectional way for implementing the required ac ground at terminal Y as well as the voltage conveying between terminals X and Z, where a differential-pair in cascade connection with a voltage follower have been employed, offering inherent resistances equal to \(1/g_{m}\) at these terminals. It must be pointed out that reduced values of \(1/g_{m}\) can be implemented by these stages, but the values of the dc bias currents of these stages must be significantly increased making the power dissipation of the active cell not reasonable for practical applications.

FVF-based VCII implementation, with nMOS-pMOS conversion, introduced in [29]

The inherent resistance at terminal X is:

A practical problem that occurs in the topology of Fig. 2 is related to the dc levels of the terminals voltages. More specifically, the dc level at terminal Y is determined by the value of the extra dc supply voltage connected at the gate of Mp1, being equal to \(V_{B}\) plus a source-gate voltage. Owing to the high-impedance nature of terminal X and the fact that the current flowing through this terminal at dc operation is equal to zero, the dc voltage at this terminal is determined by the external circuit. The voltage at terminal Z will be equal to that at terminal X increased by a source-gate voltage, limiting the maximum amplitude of the signal that it could be handled without distortion by the VCII.

Proposed modifications of the scheme in Fig. 2 for realizing a VCII+, and b VCII- with equalized dc operating point voltages at all terminals

In order to overcome this obstacle, the proposed modification of the topology in Fig. 2 is demonstrated in Fig. 3a. The dc voltage at terminal X is shifted up by the source-gate voltage of Mp9 and taking into account that both Mp9 and Mp2 are fed by the same dc current and they have common gate connection, the dc voltage at terminal X is restored back at terminal Z. The corresponding expressions of the inherent resistances given by (2)–(4) are still valid for the modified topology. The price paid for this improvement is that an extra branch constructed from three transistors is required, increasing also the power dissipation of the circuit by a term equal to \((V_{\mathrm{{DD}}}-V_{\mathrm{{SS}}})I_{0}\). Also, the minimum supply voltage requirement is increased by a factor \(V_{\mathrm{{DS,sat}}}\), being equal to \(|V_{\mathrm{{THp}}}|+2V_{\mathrm{{DS,sat}}}\), with \(|V_{\mathrm{{THp}}}|\) being the (absolute) value of the threshold of a pMOS transistor and \(V_{\mathrm{{DS,sat}}}\) being the minimum gain-overdrive voltage of MOS transistors for entering in the strong inversion region of operation. In addition, due to the absence of a diode-connected MOS at terminal Y, the level of \(\upsilon _{Y}\) is sensitive to variations in process, voltage and temperature (PVT) and this is s a disadvantage, compared with the op-amp-based input stage. Considering a typical twin-well process, the proposed topology preserves the feature for being immune from the body effect. The corresponding implementation of a VCII- is demonstrated in Fig. 3b.

2.2 Enhancements of the Proposed Topology

Inspecting the topologies in Fig. 3, it is readily obtained that the required inversion of the current that flows at terminal X is performed through the employment of a current-mirror stage formed by the transistors Mn3, Mn5, and Mp6. They can be merged into one topology, which is demonstrated in Fig. 4a, where its function (i.e., VCII+ or VCII-) can be digitally programmed through the utilization of a non-overlapping pulse scheme denoted by (\(\phi ,\bar{\phi }\)) . The associated symbol is provided in Fig. 4b. The scheme in Fig. 4a offers design modularity and versatility, in the sense that the same core can be used for realizing various types of transfer function.

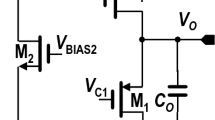

The topologies in Fig. 3 can be fed at different point in order to take advantage of the electronic tuning capability of the small-signal transconductance parameter. This is demonstrated in Fig. 5a and, assuming operation of MOS transistors in the strong inversion region, the resistance associated with terminal Y is given by (5)

Therefore, the resistance can be tuned through the corresponding dc bias current \(I_{0}\) , while the other inherent resistances are still given by (3)–(4). This circuit will be mentioned hereinafter as current-controlled VCII (CCVCII), in correspondence with the notation of a current-controlled second-generation current conveyor (CCCII), where the inherent resistance at node X is electronically controllable. The associated symbol of the CCVCII is depicted in Fig. 5b.

This topology would be useful in the cases where only an external resistor is connected at the terminal Y of the VCII, in the sense that it can be implemented by directly feeding the cell by the applied excitation without the requirement for employing an extra resistor.

3 Comparison and Discussion

The realization of the input stage related to the Y terminal of the VCII can be implemented using: (a) a two-stage op-amp, as it is depicted in Fig. 6a, (b) a single diode-connected transistor (Fig. 6b), (c) a current-mirror stage (Fig. 6c), and (d) the flipped voltage follower (Fig. 6d), fed at two different points. Their most important performance factors are summarized in Table 1, where the main conclusions are the following: (a) with regard to the circuit complexity, the topology of Fig. 6b is the most advantageous, (b) with regard to the flexibility and versatility, the employment of a FVF is the best option, in the sense that this stage is capable of offering an electronically adjustable resistance (\(1/g_{m,Mp1}\)) when is fed at the drain of Mp2 or an extremely low resistance equal to \(1/g_{m,Mp2}(g_{m,Mp1}r_{o,Mp2})\) when it is fed at the drain of Mp1.

Considering the possible realizations of the output stages (i.e., these convey the voltage at terminal X to the terminal Z) of VCIIs, which have been already published in the literature, they are summarized in Fig. 7.

From the results in Table 2, it is concluded that the FVF-based scheme in Fig. 7c is the simplest one among these in consideration, but it suffers from the relatively large parasitic resistance and from the difference between the dc levels of the voltages at terminals X and Z. More specifically, the dc level at node Z is increased by a gate-source voltage with regard to the established one at terminal X. This problem can be solved by the scheme in Fig. 7d, through the utilization of an extra-level shifter established by Mp1-Mp2 and, simultaneously, the parasitic resistance is scaled by a factor \(g_{m,Mp4}r_{o,Mp2}\). This solution is preferable than that in Fig. 7b, because of its relative simplicity, reduced power dissipation, and minimum supply voltage requirement.

Concluding, the basic topology in Fig. 3a is the best option for simultaneously achieving capability of having electronically tuned or minimized values of the parasitic resistor at terminal Y, minimized parasitic resistor at node Z, the same dc levels at all terminals of the VCII, with reasonable circuit complexity. Such VCII structure has not yet been published in the literature as its easily derived from Table 3.

4 Application Design Examples

Multi-phase sinusoidal oscillators have been widely employed in measurement systems, in control systems, in power systems, and in communication systems [5, 6, 9,10,11, 13,14,15,16, 24,25,27, 30].

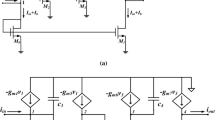

The proposed scheme of a VCII-based MSO is demonstrated in Fig. 8, where the intermediate stages realize the voltage transfer function of a first-order low-pass filter

In the case of the activation of switch controlled by \(\phi \) activation, a MSO with odd number of phases is realized, while in the case of \(\bar{\phi }\) activation an even number of phases will be offered. In both cases, the open-loop gain is given by (7)

In order to produce and sustain sinusoidal oscillations, the transfer function in (7) must satisfy the Barkhausen criteria, and therefore, the frequency of oscillation as well as the start-up oscillation condition will be

Inspecting (9), it is readily seen that the oscillation condition can be set by changing \(R_{2}\) without disturbing the frequency of oscillation. In other words, the frequency of oscillation can be determined through the time-constant of the low pass filters without disturbing the gain.

The minimum number of odd stages, and therefore of phases that will be implemented, must fulfill the condition \(n\ge 3\), while a number of \(n\ge 4\) even stages is capable of being realized by the topology in Fig. 8. This is originated from the fact that the phase shift that could be realized by each intermediate stage is less than 90\({^{\circ }}\). The phase shift introduced by each filter stage is equal to \(\pi /n\).

Using (8)–(9), the derived design equations for n=3, 4 become

With regard to the relevant literature, only single-phase VCII-based oscillator topologies have been already published in [28] and, therefore, the topology in Fig. 8 is the first VCII-based multi-phase oscillator, introduced in the literature. It must be mentioned at this point that multi-phase oscillators suitable for implementing both even and odd number of phases have been already introduced in the literature [12].

As a second design example, the implementation of an electronically controlled first-order low-pass filter, using the CCVCII as active element, will be demonstrated. Using (5), the topology given in Fig. 9 realizes the transfer function

According to (12), the -3dB cut-off frequency is given by the formula: \(\omega _{-3\mathrm{{dB}}}=g_{m,Mp5}/C_{1}\) and, therefore, it is electronically adjusted through the dc bias current. It must be mentioned at this point that by adding an external resistor at terminal X, then the topology will act as a trans-resistance filter [33] with its output being obtained at terminal Z.

5 Simulation and Experimental Results

5.1 Multi-phase Oscillator

5.1.1 Simulation Results

The behavior of the topology in Fig.8 will be initially evaluated through simulations, performed using the Cadence IC design suite and MOS transistors models provided by the Austria Mikro Systeme (AMS) 0.35 \(\upmu \)m CMOS process. Considering a single power supply voltage scheme with \(V_{\mathrm{{DD}}}\)=1.5 V and \(V_{\mathrm{{SS}}}\) = 0 V, and choosing \(V_{B}\) = 300 mV and \(I_{0}\) = 10 \(\upmu \)A , the aspect ratios of the MOS transistors in Fig. 3a are summarized in Table 4. The values of the parasitic resistances are the following: \(r_{X}\) = 338 k\(\Omega \), \(r_{Y}\) = 34.7 \(\Omega \), and \(r_{Z}\) = 34.5 \(\Omega \). The frequency behavior of the current and voltage transfer between terminals Y, X and X, Z, respectively, is demonstrated in Fig. 10, where the bandwidth of the current gain is 52 MHz, while the bandwidth of the voltage gain is 46.7 MHz.

Frequency responses of the current (\(i_{X}/i_{Y}\)) and voltage (\(\upsilon _{Z}/\upsilon _{X}\)) gain of the VCII in Fig. 3a

The passive elements values were \(R_{1}\)=22 k\(\Omega \), \(C_{1}\) = 1 nF, while for n = 3 the value of resistor \(R_{2}\) for establishing oscillations was chosen equal to 10 k\(\Omega \). The obtained output waveforms of three-phase oscillator are demonstrated in Fig. 11a, where the simulated value of the frequency of oscillation is 13.34 kHz with the theoretically predicted one calculated from (10) being 12.54 kHz. The values of the phase difference between \(\upsilon _{\mathrm{{out2}}}\) and \(\upsilon _{\mathrm{{out1}}}\) as well as between \(\upsilon _{\mathrm{{out3}}}\) and \(\upsilon _{\mathrm{{out2}}}\) are 120.1\(^{\circ }\), 119.3\(^{\circ }\), close to the theoretically predicted value of 120\(^{\circ }\). The Total Harmonic Distortion (THD) level of the outputs is 0.84%. The phase noise plot associated to \(\upsilon _{\mathrm{{out3}}}\) is depicted in Fig. 12a.

The oscillations in the case of n = 4 start for \(R_{2}\) = 14.1 k\(\Omega \), and the derived waveforms are plotted in Fig. 11b, with the frequency of oscillation being 7.69 kHZ and the theoretical one being 7.25 kHz. The values of the phase difference between \(\upsilon _{\mathrm{{out2}}}\) and \(\upsilon _{\mathrm{{out1}}}\), \(\upsilon _{\mathrm{{out3}}}\) and \(\upsilon _{\mathrm{{out2}}}\), and \(\upsilon _{\mathrm{{out4}}}\) and \(\upsilon _{\mathrm{{out3}}}\) are 134.8\(^{\circ }\), 133.4\(^{\circ }\), and 138.4\(^{\circ }\), with the theoretically predicted one being 135\(^{\circ }\). The THD of the outputs {\(\upsilon _{\mathrm{{out1}}}\), \(\upsilon _{\mathrm{{out2}}}\), \(\upsilon _{\mathrm{{out3}}},\) \(\upsilon _{\mathrm{{out4}}}\)} is {0.29%, 0.11%, 0.12%, 0.40%}, while the phase noise plot of \(\upsilon _{\mathrm{{out4}}}\) is provided in Fig. 12b.

5.1.2 Experimental Results

The implementation of the configuration in Fig. 8 is also performed by employing the AD844 discrete component ICs as VCIIs and using the same values of the passive elements as in the previous cases. The experimental setups are demonstrated in Fig. 13, and the obtained waveforms are provided in Fig. 14a–b. The measured frequencies of oscillation are 14.45 kHz (for n = 3) and 7.58 kHz for n = 4. The values of the phase difference, in accordance with those derived through simulations, were {120.7\({^{\circ }}\), 118.3\({^{\circ }}\)} and {135.1\({^{\circ }}\), 138.7\({^{\circ }}\), 132.5\({^{\circ }}\)}. The spectrum of \(\upsilon _{\mathrm{{out3}}}\) in the case of the three-phase MSO and \(\upsilon _{\mathrm{{out4}}}\) in the case of the four-phase MSO is depicted in Fig. 15a–b, with the measured values of THD being 0.63% and 0.45%, respectively.

5.2 Electronically Controlled Current-Mode First-Order Low-pass Filter

The performance of the filter is evaluated using the same bias scheme (about dc voltages) as in the previous example, and the circuitry provided in Fig. 5a. The MOS transistors have the aspect ratios given in Table 4. The electronic tuning capability of the resistance \(r_{Y}\) is demonstrated in Fig. 16, where the bias current (\(I_{0}\)) is varied within the range where the MOS transistors are operate in the strong inversion region. The resulted values of resistance are in the range [1.14,41] k\(\Omega \).

Demonstration of the electronics tuning capability of the parasitic resistance at terminal Y of the CCVCII in Fig. 5a

The obtained magnitude and phase frequency responses for bias currents {1 \(\upmu \)A, 10 \(\upmu \)A, and 20 \(\upmu \)A}, which correspond to transconductance values {24.37 \(\upmu \)S, 192.17 \(\upmu \)S, 327.19 \(\upmu \)S}, and C = 1 nF, are depicted by the plots in Fig. 17, with the corresponding theoretically predicted ones given by dashes. The values of the cut-off frequencies are 3.91 kHz, 30.8 kHz, 51.2 kHz and, as they are close to the theoretically expected values 3.88 kHz, 30.6 kHz, 52.1 kHz they confirm the electronic adjustment capability of the characteristic frequency of the filter. As the capacitor value is very large, it cannot be implemented on silicon. As a result, an external capacitor will be utilized for implementing the presented scheme.

Time-domain behavior of the filter in Fig. 9a input and output waveforms for a 5\(\upmu \)A, 30.8 kHz sinusoidal excitation, and b THD vs modulation index factor

Setup for evaluating the performance of the CCVCII-based electronically controlled first-order LP filter in Fig. 9

The time-domain behavior of the filter is evaluated for a 5 \(\upmu \)A, 30.8 kHz sinusoidal input signal in the case of the bias current \(I_{0}\)=10 \(\upmu \)A. The derived output waveform, along with the input waveform, are demonstrated in Fig. 18a, and the values of the gain and output-input phase difference are \(-\) 3.1 dB and 136.3\({^{\circ }}\), with the theoretically expected values being \(-\) 3 dB and 135\({^{\circ }}\), respectively.

In addition, the linear performance of the filter (for \(I_{0}\) = 10 \(\upmu \)A) is evaluated by stimulating it by a 1 kHz sinusoidal signal of variable amplitude. The plot of THD versus the modulation index factor (i.e., the ratio of the amplitude over the input and the value of the dc bias current) is given in Fig. 18b, where it is derived that THD levels equal to 1% and 2% are obtained for modulation index factors 0.6 and 0.84, respectively.

The sensitivity performance of the filter, with regard to the effects of the MOS transistors parameters mismatching, is evaluated through the Monte-Carlo analysis tool. The obtained statistical plots related to the maximum gain and cut-off frequency of the filter are presented in Fig. 19a–b, respectively. Taking into account that the values of the standard deviation are 19 mdB and 0.52 kHz, and the corresponding mean values are 0.17 dB and 32.55 kHz, it is concluded that the presented filter structure offers reasonable sensitivity characteristics.

The behavior of the filter has been also experimentally verified through the setup depicted in Fig. 20. The obtained responses are demonstrated in Fig. 21a–c. The values of the resistance \(R_{1}\) have been chosen as 41.04 k\(\Omega \), 5.2 k\(\Omega \), and 3.06 k\(\Omega \), in order to be equal to the corresponding values of the inherent resistance \(r_{Y}\) of the CCVCII for bias currents {1\(\upmu \)A, 10 \(\upmu \)A, and 20 \(\upmu \)A}. The measured values of cut-off frequencies are 3.98 kHz, 30.2 kHz, and 52.48 kHz with the theoretically predicted ones being 3.88 kHz, 30.6 kHz, 52.1 kHz, while the values of phase are 135.4\({^{\circ }}\), 136.9\({^{\circ }}\), and 137.2\({^{\circ }}\) with the theoretically predicted value being 135\({^{\circ }}\).

6 Conclusions

The employment of appropriately configured flipped voltage followers for realizing the stages associated with the terminals Y and Z of a VCII leads to configurations which offer extremely low inherent resistances. As it is proved through the presented comparison results, this is achieved by keeping the same dc levels at these terminals in contrast to the literature where an offset is observed.The presented MSO design example, which is the first one in the literature, is supported by simulation and experimental results both proved the correct operation of the MSO scheme. The introduced VCII structure could be also fed into another point, where the small-signal transconductance parameter of MOS transistor is utilized, offering the capability of electronic adjustment of the associated inherent resistance. This is demonstrated in the case of a current-mode first-order filter, where the cut-off frequency is controlled by a dc bias current. The derived results about the frequency and time-domain behavior of the filter show attractive performance characteristics.

Data Availability

Data sharing was not applicable to this article as no datasets were generated or analyzed during the current study.

References

G. Barile, L. Safari, G. Ferri, V. Stornelli, A VCII-based stray insensitive analog interface for differential capacitance sensors. Sensors 19(16), 3545 (2019)

G. Barile, L. Safari, L. Pantoli, V. Stornelli, G. Ferri, Electronically tunable first order AP/LP and lp/hp filter topologies using electronically controllable second generation voltage conveyor (CVCII). Electronics 10(7), 822 (2021)

G. Barile, V. Stornelli, G. Ferri, L. Safari, E. D’Amico, A new rail-to-rail second generation voltage conveyor. Electronics 8(11), 1292 (2019)

R.G. Carvajal, J. Ramírez-Angulo, A.J. López-Martín, A. Torralba, J.A.G. Galán, A. Carlosena, F.M. Chavero, The flipped voltage follower: a useful cell for low-voltage low-power circuit design. IEEE Trans. Circuits Syst. I Regul. Pap. 52(7), 1276–1291 (2005)

B. Chaturvedi, A. Kumar, Electronically tunable first-order filters and dual-mode multiphase oscillator. Circuits Syst. Signal Process. 38(1), 2–25 (2019)

J. Dvorak, D. Kubanek, J. Koton, J. Jerabek, and D. Smekal. Adjustable multiphase sinusoidal oscillator with fractional–order elements. In 2019 11th International Congress on Ultra Modern Telecommunications and Control Systems and Workshops (ICUMT), pp. 1–6. IEEE, 2019

G. Ferri, L. Safari, G. Barile, L. Pantoli, V. Stornelli, Noise analysis and optimization of VCII-based SiPM interface circuit. Analog Integr. Circuits Sig. Process 109(1), 1–9 (2021)

G. Ferri, L. Safari, G. Barile, M. Scarsella, V. Stornelli, New resistor-less electronically controllable\(\pm \)C simulator employing VCII, DVCC, and a grounded capacitor. Electronics 11(2), 286 (2022)

W. Jaikla, P. Prommee, Electronically tunable current-mode multiphase sinusoidal oscillator employing CCCDTA-based allpass filters with only grounded passive elements. Radioengineering 20(3), 594–599 (2011)

M. Jones, S.N. Vukosavic, E. Levi, A. Iqbal, A six-phase series-connected two-motor drive with decoupled dynamic control. IEEE Trans. Ind. Appl. 41(4), 1056–1066 (2005)

A. Kumar, S.K. Paul, Current mode first order universal filter and multiphase sinusoidal oscillator. AEU-Int. J. Electron. Commun. 81, 37–49 (2017)

M. Kumngern, J. Chanwutitum, K. Dejhan, Electronically tunable multiphase sinusoidal oscillator using translinear current conveyors. Analog Integr. Circuits Sig. Process 65(2), 327–334 (2010)

M. Kumngern, U. Torteanchai, and F. Khateb. CMOS class AB second generation voltage conveyor, in 2019 IEEE International Circuits and Systems Symposium (ICSyS), pp. 1–4. IEEE, 2019

D.-C. Lee, Y.-S. Kim, Control of single-phase-to-three-phase AC/DC/AC PWM converters for induction motor drives. IEEE Trans. Industr. Electron. 54(2), 797–804 (2007)

R. Pandey, N. Pandey, M. Bothra, S.K. Paul, Operational transresistance amplifier-based multiphase sinusoidal oscillators. J. Electr. Comput. Eng. 2, 11 (2011)

K. Pitaksuttayaprot and W. Jaikla. Electronically tunable current-mode multiphase sinusoidal oscillator employing CDCTA-based all pass filters, in Proceedings of the International Conference on Circuits, Systems and Control, pp. 69–73, 2014

L. Safari, G. Barile, D. Colaiuda, V. Stornelli, G. Ferri, Realization of an electronically tunable resistor-less floating inductance simulator using VCII. Electronics 11(3), 312 (2022)

L. Safari, G. Barile, G. Ferri, M. Ragnoli, V. Stornelli, A new realization of electronically tunable multiple-input single-voltage output second-order LP/BP filter using VCII. Electronics 11(4), 646 (2022)

L. Safari, G. Barile, G. Ferri, V. Stornelli, High performance voltage output filter realizations using second generation voltage conveyor. Int. J. RF Microwave Comput. Aided Eng. 28(9), e21534 (2018)

L. Safari, G. Barile, G. Ferri, V. Stornelli, A new low-voltage low-power dual-mode VCII-based SIMO universal filter. Electronics 8(7), 765 (2019)

L. Safari, G. Barile, V. Stornelli, G. Ferri, An overview on the second generation voltage conveyor: features, design and applications. IEEE Trans. Circuits Syst. II Express Briefs 66(4), 547–551 (2018)

L. Safari, G. Barile, V. Stornelli, S. Minaei, G. Ferri, Towards realization of a low-voltage class-AB VCII with high current drive capability. Electronics 10(18), 2303 (2021)

L. Safari, E. Yuce, S. Minaei, G. Ferri, V. Stornelli, A second-generation voltage conveyor (vcii)-based simulated grounded inductor. Int. J. Circuit Theory Appl. 48(7), 1180–1193 (2020)

M. Sagbas, U.E. Ayten, N. Herencsar, S. Minaei, Current and voltage mode multiphase sinusoidal oscillators using CBTAs. Radioengineering 22(1), 24–33 (2013)

S. Siripongdee, P. Suwanjan, S. Tuntrakool, W. Jaikla, Electronically controllable current-mode multiphase sinusoidal oscillator for biomedical tissue measurement systems. Int. J. Biosci. Biochem. Bioinform. 4(1), 57 (2014)

G. Skotis, C. Psychalinos, Multiphase sinusoidal oscillators using second generation current conveyors. AEU-Int. J. Electron. Commun. 64(12), 1178–1181 (2010)

G. Souliotis, C. Psychalinos, Electronically controlled multiphase sinusoidal oscillators using current amplifiers. Int. J. Circuit Theory Appl. 37(1), 43–52 (2009)

V. Stornelli, G. Barile, L. Pantoli, M. Scarsella, G. Ferri, F. Centurelli, P. Tommasino, A. Trifiletti, A new VCII application: sinusoidal oscillators. J. Low Power Electron. Appl. 11(3), 30 (2021)

V. Stornelli, L. Safari, G. Barile, G. Ferri, A new extremely low power temperature insensitive electronically tunable VCII-based grounded capacitance multiplier. IEEE Trans. Circuits Syst. II Express Briefs 68(1), 72–76 (2020)

G. Tsirimokou, C. Psychalinos, A. Elwakil, and B. Maundy. Fractional-order multiphase sinusoidal oscillator design using current-mirrors, in 2018 41st International Conference on Telecommunications and Signal Processing (TSP), pp. 1–4. IEEE, 2018

A. Yesil, S. Minaei, New simple transistor realizations of second-generation voltage conveyor. Int. J. Circuit Theory Appl. 48(11), 2023–2038 (2020)

A. Yesil, S. Minaei, C. Psychalinos, \(\pm \)0.45 V CMOS second-generation voltage conveyor based on super source follower. Circuits Syst. Signal Process. 2, 1–15 (2021)

A. Yesil, D. Ozenli, 4th order current-mode and transresistance-mode mosfet-c low-pass filter for multi-standard receivers. Microelectron. J. 115, 105159 (2021)

E. Yuce, L. Safari, S. Minaei, G. Ferri, G. Barile, V. Stornelli, A new simulated inductor with reduced series resistor using a single VCII\(\pm \). Electronics 10(14), 1693 (2021)

E. Yuce, L. Safari, S. Minaei, G. Ferri, V. Stornelli, New mixed-mode second-generation voltage conveyor based first-order all-pass filter. IET Circuits Dev. Syst. 14(6), 901–907 (2020)

Funding

Open access funding provided by HEAL-Link Greece.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

There are no relevant conflict of interest to report.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Psychalinos, C., Yesil, A., Minaei, S. et al. Flipped Voltage Follower-Based Voltage Conveyors: Investigation and Possible Enhancements. Circuits Syst Signal Process 42, 2028–2048 (2023). https://doi.org/10.1007/s00034-022-02230-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-022-02230-0