Abstract

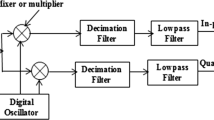

This paper presents an implementation of a reconfigurable digital down converter (DDC) that can translate high sample rate to lower sample rate signal on field-programmable gate array (FPGA) platform using polyphase filtering. The proposed DDC consists of a polyphase mixer, a cascaded integrator comb (CIC) filter, and a finite impulse response (FIR) filter. The polyphase mixer reduces computational complexity and multiplier blocks simultaneously. Furthermore, the modified CIC filter improves the operating speed, and the new design method of the FIR filter saves memory storage to a great extent. The proposed structure is highly flexible so that the decimation factor can be programmed dynamically during runtime in terms of the sample rate, bandwidth, center frequency, and so on. Moreover, the optimum hardware description language (HDL) coding techniques significantly improve the area efficiency and speed performance of the DDC without compromising the functionality. The proposed design is synthesized using Xilinx Vivado 2020.2 and tested on a Xilinx Kintex-7 FPGA XC7K70T-FBG676 as the target device. Comparison results indicate that the proposed design substantially reduces the resources as well as power. A verification test is to certify the feasibility and correctness of the hardware implementation. The proposed DDC is well-matched in any digital radio application.

Similar content being viewed by others

Data availability

All data are available in the manuscript.

References

S. Creaney, I. Kostarnov, Designing efficient digital up and down converters for narrowband systems. XAPP1113 (v1.0) (2008). https://www.xilinx.com/support/documentation/application_notes/xapp1113.pdf

D. Datta, P. Mitra, H.S. Dutta, FPGA implementation of high performance digital down converter for software defined radio. Microsyst. Tech. (2019). https://doi.org/10.1007/s00542-019-04579-w

G.J. Dolecek, S.K. Mitra, A new two-stage sharpened comb Decimator. IEEE Trans. Circuits Syst. I. 52(7), 1414–1420 (2005). https://doi.org/10.1109/TCSI.2005.851390

L. Guo, F. Tan, P. Zhan, H. Zeng, Decomposing numerically controlled oscillator in parallel digital down conversion architecture. J. Circuits Syst. Comp. (2017). https://doi.org/10.1142/S0218126617501262

F. Harris, Multirate Signal Processing for Communication Systems (Pearson Education Ltd., London, 2004).

E.B. Hogenauer, An economical class of digital filters for decimation and interpolation. IEEE Trans. Acoust. Speech Signal Process. 29(2), 155–162 (1981). https://doi.org/10.1109/TASSP.1981.1163535

V. Jayaprakasan, S. Vijayakumar, P.V. Naishadhkumar, Design of CIC based decimation filter structure using FPGA for WiMAX applications. IEICE Electr. Express 16(7), 1–6 (2019). https://doi.org/10.1587/elex.16.20190074

Q. Jing, Y. Li, J. Tong, Performance analysis of resample signal processing digital filters on FPGA. EURASIP J. on Wirel. Commun. Netw. 31, 1–9 (2019). https://doi.org/10.1186/s13638-019-1349-9

T. Liu, S. Tian, L. Guo, Parallel wideband digital up-conversion architecture with efficiency. The J. Eng. 2019(23), 8587–8590 (2019). https://doi.org/10.1049/joe.2018.9061

X. Liu, X. Yan, Z. Wang, Q. Deng, Design and FPGA implementation of a reconfigurable digital down converter for wideband applications. IEEE Trans. VLSI Syst. 25(12), 3548–3552 (2017). https://doi.org/10.1109/TVLSI.2017.2748603

M. Loehning, T. Hentschel, G. Fettweis, Digital down conversion in software radio terminals. In: 2000 10th European Signal Processing Conference Finland 3, IEEE (2000)

U. Meyer-Baese, Digital Signal Processing with Field Programmable Gate Arrays, 3rd edn. (Springer, Cham, 2007).

L. Milic, Multirate Filtering for Digital Signal Processing: Matlab Applications (Information Science Reference, Hershey, NY, USA, 2009). http://firasaboulatif.free.fr/index_files/gaidaa%20book/Digital%20Signal%20Processing/Multirate%20Filtering.pdf

L.L. Motta, B.A.A. Acurio, N.F.T.A. Aniceto, L.G.P. Meloni, Design and implementation of a digital down/up conversion directly from/to RF channels in HDL. Int. the VLSI J. 68, 30–37 (2019). https://doi.org/10.1016/j.vlsi.2019.05.006

S. Navid Shahrouzi, D. G. Perera, HDL code optimizations: impact on hardware implementations and CAD tools. In: 2019 IEEE Pacific Rim Conference on Communications, Computers and Signal Processing (PACRIM), Canada, (2019). https://doi.org/10.1109/PACRIM47961.2019.8985074

V. Obradović, P. Okiljević, N. Kozić, D. Ivković, Practical implementation of digital down conversion for wideband direction finder on FPGA. Sci. Tech. Rev. 66(4), 40–46 (2016). https://doi.org/10.5937/STR1604040O

A.V. Oppenheim, R.W. Schafer, Discrete-Time Signal Processing, 3rd edn. (Prentice Hall, New Jersey, 2010).

P. Sikka, A.R. Asati, C. Shekhar, Power-and area-optimized high-level synthesis implementation of a digital down converter for software-defined radio applications. Circuits Syst. Signal Process (2020). https://doi.org/10.1007/s00034-020-01601-9

V.K. Tiwari, S.K. Jain, Hardware implementation of polyphase decomposition-based wavelet filters for power system harmonics estimation. IEEE Trans. Instr. Meas. 65(7), 1585–1595 (2016). https://doi.org/10.1109/TIM.2016.2540861

W. Wolf, FPGA-Based System Design (Prentice- Hall, Englewood Cliffs, NJ, 2004).

R. Yates, Fixed-point arithmetic: an introduction. August 23, (2007). https://courses.cs.washington.edu/courses/cse467/08au/labs/l5/fp.pdf

Z. Zulfikar, Novel area optimization in FPGA implementation using efficient vhdl code. J. Rekayasa Elektr. 10(2), 61–66 (2012). https://doi.org/10.17529/jre.v10i2.116

Acknowledgements

The authors are expressed their sincere gratitude to MAKAUT for providing the valuable Xilinx Vivado Design Suite 2020.2 and FPGA board.

Funding

Funding not received.

Author information

Authors and Affiliations

Contributions

All the authors listed on the title page have contributed significantly to the work, have read the manuscript, attest to the validity and legitimacy of the data and its interpretation, and agree to its submission. The first author has prepared the proposed architecture, tables, figures, results, and body of the manuscript. The second author or co-author describes the abstract, literature survey discussion, and conclusion sections. Both authors read and approved the final manuscript.

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interests.

Ethical Approval

This article does not contain any studies with human participants or animals performed by any of the authors.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Datta, D., Dutta, H.S. High Efficient Polyphase Digital Down Converter on FPGA. Circuits Syst Signal Process 40, 5787–5798 (2021). https://doi.org/10.1007/s00034-021-01749-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-021-01749-y